目前在用21489內部的IIR加速器去做一個低通濾波器,在例程的基礎上修改參數。通過平板的fda 工具工具去設計參數,但是設計出來的參數不知道如何對應加速器的濾波參數,手冊里也看得不是很明白。

設計的參數如下:

請問這些參數應該如何對應起來?

2023-11-30 08:11:55

1、FIR 濾波器是在數字信號處理(DSP)中經常使用的兩種基本的濾波器之一,另一個為IIR濾波器。 2、FIR代表有限沖激響應(Finite Impulse Response)的簡稱。 3

2011-09-24 16:05:53

低,但是線性相位,就是不同頻率分量的信號經過fir濾波器后他們的時間差不變。這是很好的性質。另外有限的單位響應也有利于對數字信號的處理,便于編程,用于計算的時延也小,這對實時的信號處理很重要IIR

2018-03-12 13:21:07

相位,就是不同頻率分量的信號經過FIR濾波器后他們的時間差不變。這是很好的性質。 另外有限的單位響應也有利于對數字信號的處理,便于編程,用于計算的時延也小,這對實時的信號處理很重要。圖3 在

2016-08-08 08:49:32

輸入數據和歷史輸入數據,IIR的濾波輸出取決于當前輸入數據、歷史輸入數據和歷史輸出數據。以基于FPGA硬件的數字濾波器為例,FIR在處理信號時不需等待前一個信號的濾波輸出,只需要考慮輸入數據便可實時

2019-06-27 04:20:31

的輸入信號值。對于IIR濾波器,沖激響應理論上應會無限持續,其輸出不僅取決于當前和過去的輸入信號值,也取決于過去的信號輸出值。2.FIR:有限脈沖響應濾波器。有限說明其脈沖響應是有限的。與IIR相比

2019-06-26 06:15:35

DSP技術廣泛應用于各個領域,但傳統的數字信號處理器由于以順序方式工作使得數據處理速度較低,且在功能重構及應用目標的修改方面缺乏靈活性。而使用具有并行處理特性的FPGA實現數字信號處理系統,具有很強的實時性和靈活性,因此利用FPGA實現數字信號處理成為數字信號處理領域的一種新的趨勢。

2019-10-17 08:12:27

、數字濾波器設計(IIR、FIR及特殊形式的濾波器)等;下篇內容包括信號的正交變換(正交變換的定義與性質、K-L變換、DCT及其在圖像壓縮中的應用)、信號處理中若干典型算法(如抽取與插值、子帶分解、調制

2023-09-19 08:01:36

的基礎。隨后幾章闡述了計算機算法的概念、理論、FIR和IIR濾波器的實現、多抽樣率數字信號系統、DFT和FFT算法、未來很可能實現的高級算法以及自適應濾波器等。每一章都包含練習。附錄中給出了Verilog源代碼

2023-09-19 06:38:28

?DaVinci是一款高度集成的片上系統(SoC),集成了數字視頻所需的幾乎全部組件??TMS320C64x+DSP內核+ARM926處理器+視頻加速器??10/100M網口??主/從USB口

2011-09-14 10:06:11

對于一個從事電子信息行業的人員,對于數字信號處理器應該特別了解了。數字信號處理器,簡稱為DSP,可以說是一種專用的微處理器,從其體系結構方面來看,可以針對數字信號處理當中,進行必要的優化。DSP

2020-12-09 14:01:39

利用對稱性減少乘法器。上述兩個模塊設計可以參考“FPGA數字信號處理(二)并行FIR濾波器Verilog設計” https://blog.csdn.net/fpgadesigner/article

2020-09-27 09:22:58

Hi,HenryLj.mo請問下在Sigma 300里面使用硬件加速器slew,slew mode為RC type時,對應的time constant 與數據從當前值到目標值得時間有什么關系,或者說不同的time constant的值有什么用? Thanks,Jack

2019-01-29 06:55:13

ADSP系列數字信號處理器原理介紹,一共7個部分

2016-05-28 09:22:40

平臺的基礎,依賴這款基于Keystone的DSP實時算法處理和網絡對接。進行全新掃描—由于圖像處理是數字信號處理的長項…

2022-11-21 07:03:10

FPGA實現高速FFT處理器的設計介紹了采用Xilinx公司的Virtex - II系列FPGA設計高速FFT處理器的實現方法及技巧。充分利用Virtex - II芯片的硬件資源,減少復雜邏輯,采用

2012-08-12 11:49:01

H.264解碼器中CABAC硬件加速器怎么實現?

2021-06-07 06:48:58

英特爾媒體加速器參考軟件是用于數字標志、交互式白板(IWBs)和亭位使用模型的參考媒體播放器應用軟件,它利用固定功能硬件加速來提高媒體流速、改進工作量平衡和資源利用,以及定制的圖形處理股(GPU)管道解決方案。該用戶指南將介紹和解釋如何使用英特爾媒體加速器視窗參考軟件。

2023-08-04 07:07:34

利用MCU處理類似FPU運算內容,會因為MCU本身的運算架構限制,讓 運算結果得出時間會相對拉長,而在導入硬件加速器處理浮點運算時,因為硬件呼叫或是資料傳遞就能透過硬件算出數據,MCU本身耗在浮點運算

2016-10-14 17:17:54

DSP成為針對這一函數的最佳內核。來看看如何在SAR函數中充分利用這款高性能DSP。無需討論太多—我們在智能手機、平板電腦等設備上使用了越來越多的流媒體視頻,這使我們現在很少有時間進行面對面的交談

2018-09-10 15:16:55

數字信號處理器

2023-03-24 15:01:31

`《基于FPGA的數字信號處理》是一本有關如何在FPGA上實現數字信號處理的著作。本書以Xilinx高端FPGA作為開發平臺,以數字信號處理理論為基礎,結合當前的FPGA技術,深入探討了基于FPGA

2012-04-24 09:33:23

變換法所需要注意的問題,脈沖響應不變法不存在這種問題)。確定H(S)后,就可以通過雙線性變換得到其數字域的差分方程。 3.對于IIR和FIR的比較,有些書上有論述。我引用陳懷琛的“數字信號處理

2019-09-29 14:06:31

很強的數據處理能力,然而系統必要的控制功能是DSP所不擅長的。什么是數字信號處理器性價比的新標桿?我們需要注意什么?

2019-08-02 07:25:28

Cortex-M3處理器的簡單微控制器(MCU)以及單獨的專有專用數字信號處理器(DSP)。但是現在,我們看到越來越多的產品制造商(或原始設備制造商-OEM)轉向具有DSP擴展功能的單個高性能,低功耗MCU,例如

2022-07-29 14:48:46

您好!當我使用ADSP-21489的fir加速器時,存在很大的噪音,未知如何解決,希望這里有高人幫我解決。

附件上有工程,該工程參考iir加速器使用例子編寫。

2023-11-30 07:49:32

)。而且,在我的測試中,我發現關閉“硬件加速器”允許屏幕在旋轉時正確地繪制,但是這使得系統使用起來非常緩慢和痛苦(壞的用戶體驗)。謝謝任何幫助。

2020-04-03 10:56:36

哪位大神關于《數字信號處理與數字信號處理器》的DSP論文,求分享。。。。

2014-05-27 16:25:52

在VDSP++的環境下程序已經實現,但是到了CCES下,把中斷初始化函數修改了,還是無法正確配置中斷,直接返回IIR的中斷初始化失敗,請問CCES下怎么使用IIR加速器?

2023-11-30 08:20:36

嗨,我需要在XC7K325T FPGA中充分利用GTX資源。結果,我必須以這種方式使用一個四邊形,它的兩個頻道應該服務于10Gb / s鏈路和另外兩個--1Gb / s鏈路。這意味著,兩個通道必須

2020-07-22 13:25:20

模式。系統的主要功能器件包括arm Cortex-M3處理器、兩組硬件加速器、AHB總線矩陣、AXI互聯模塊、APB橋接器、DDR3存儲器、攝像頭模塊、片上存儲模塊、HDMI顯示模塊、APB外設

2022-08-26 15:23:33

無需被修改就可支持多核平臺。 操作系統專為充分利用多個處理器而設計,且無需修改就可運行。為了充分利用多核技術,應用開發人員需要在程序設計中融入更多思路,但設計流程與目前對稱多處理(SMP)系統

2019-06-20 06:47:01

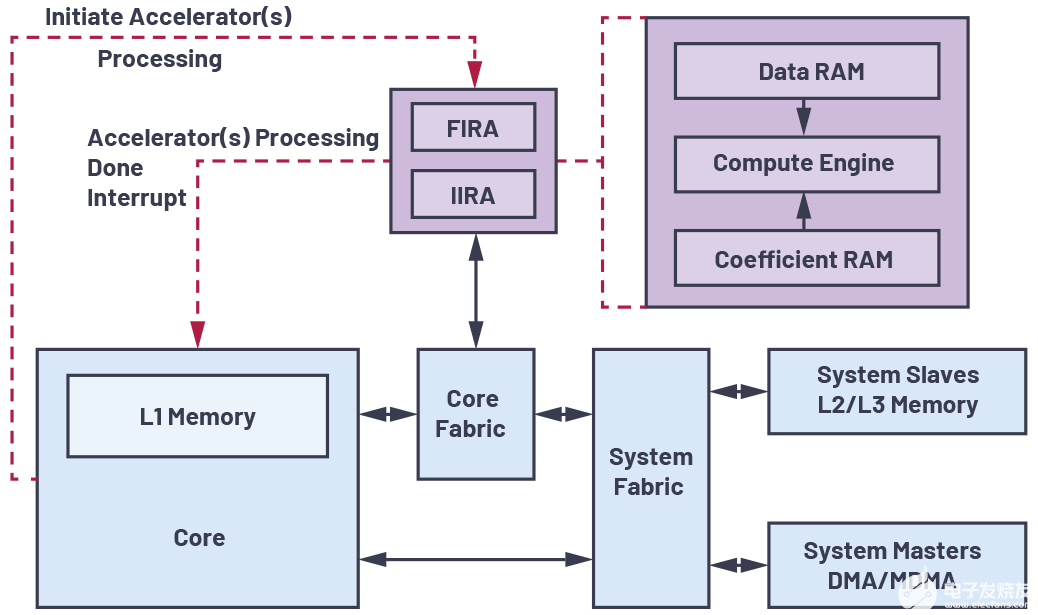

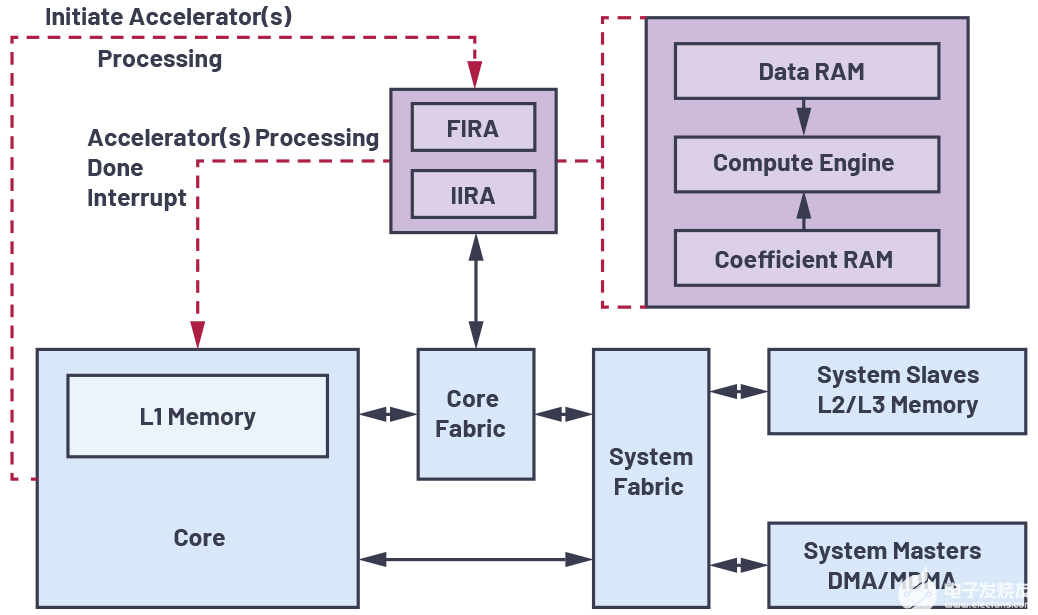

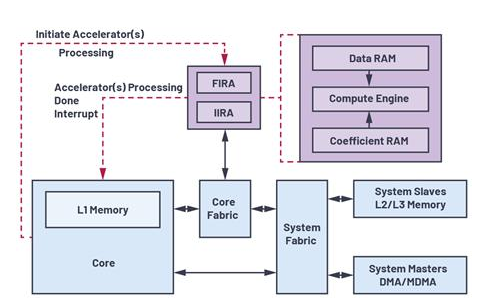

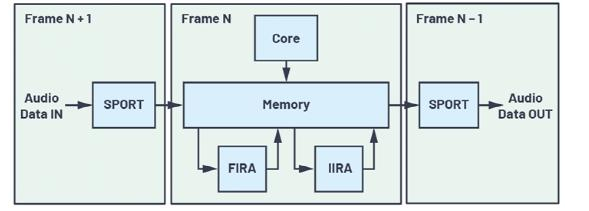

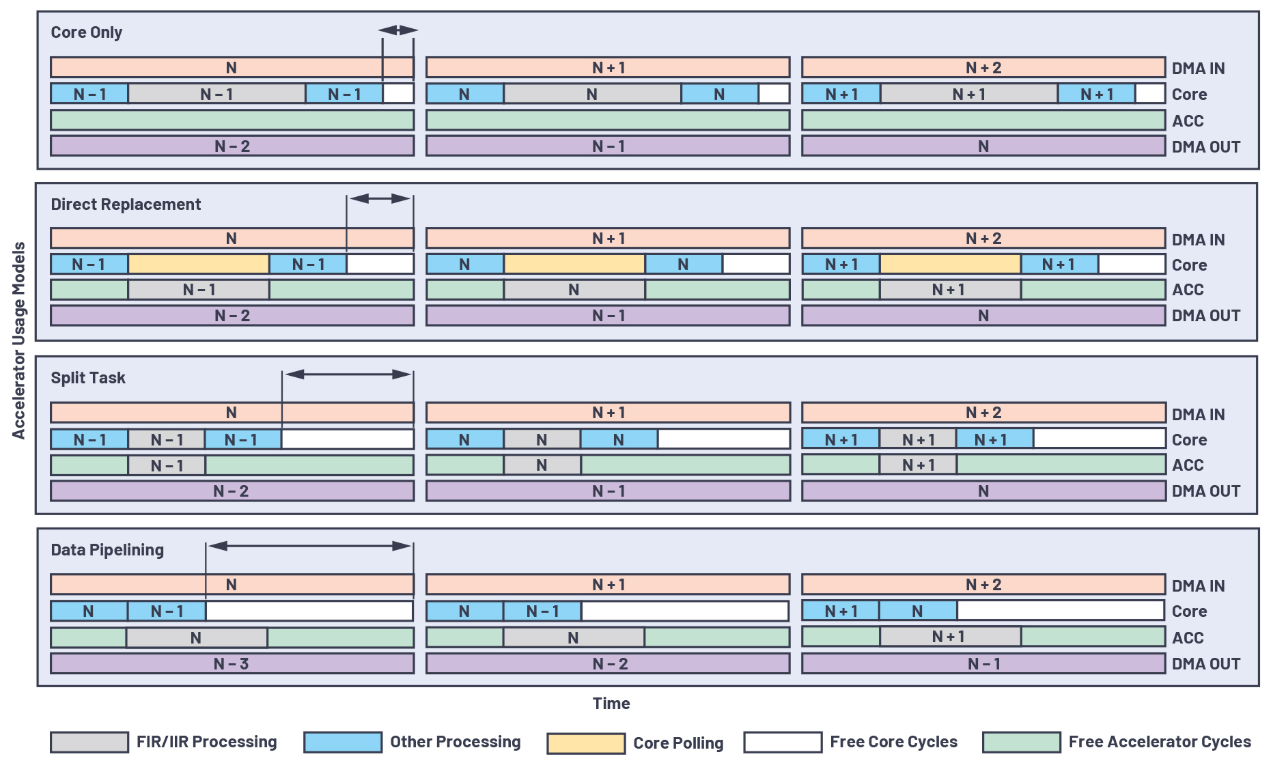

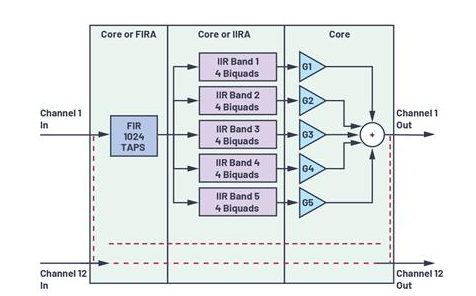

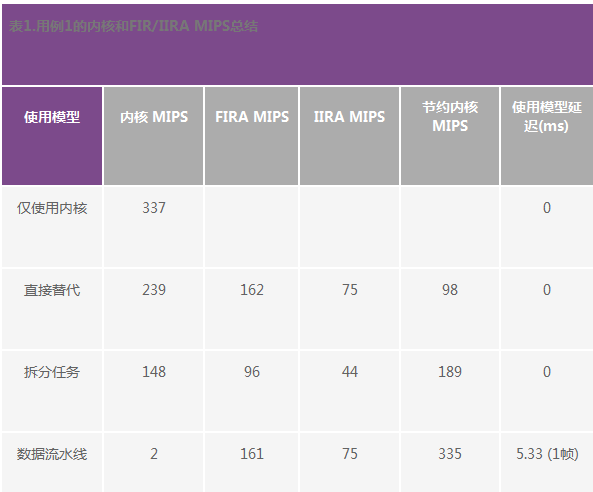

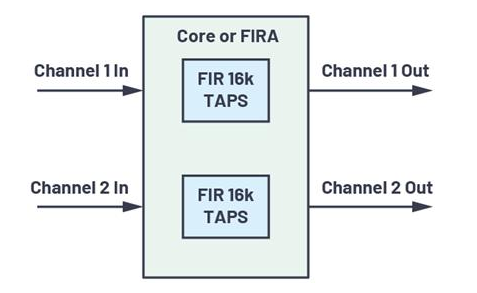

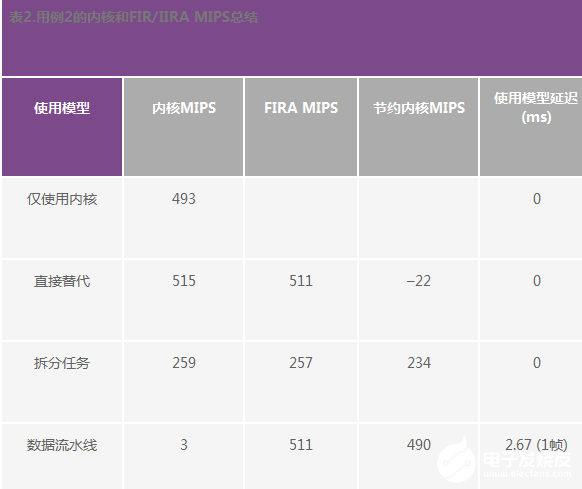

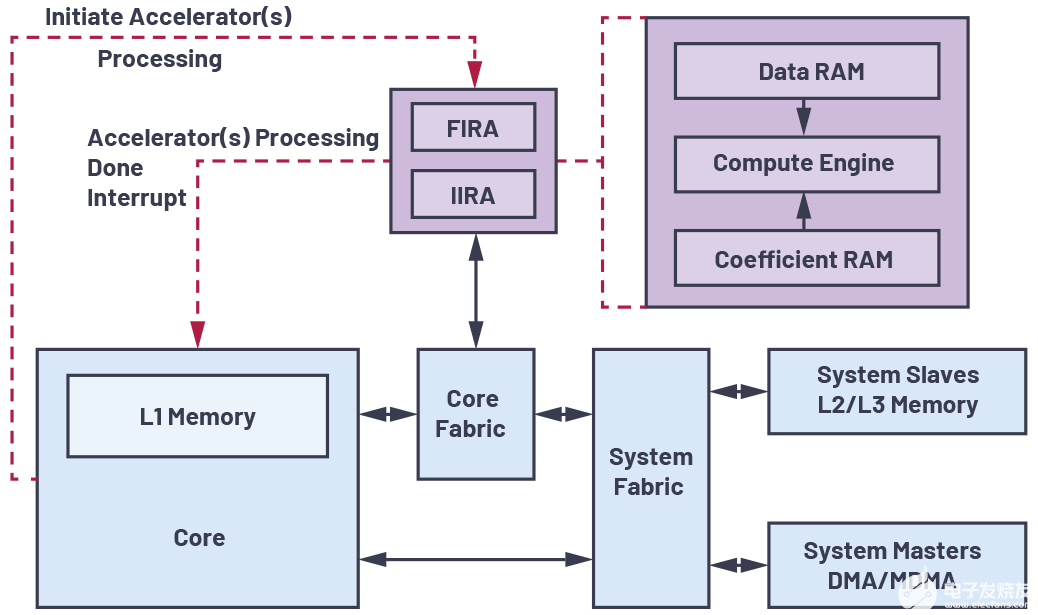

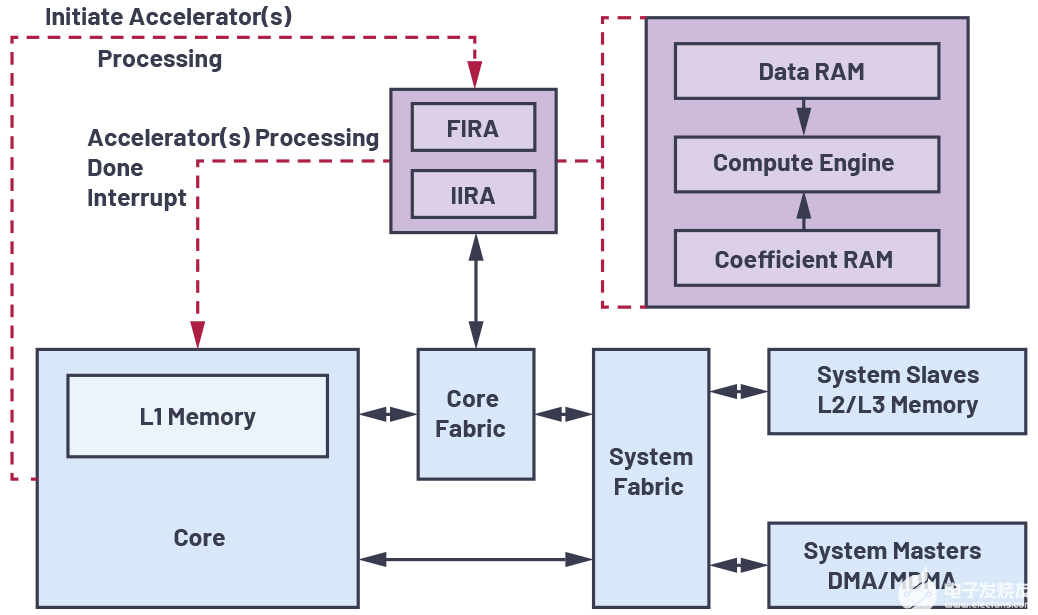

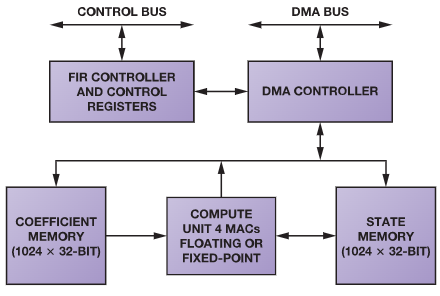

上的片內FIR和IIR硬件加速器也分別稱為FIRA和IIRA,我們可以利用這些硬件加速器來分擔FIR和IIR處理任務,讓內核去執行其他處理任務。在本文中,我們將借助不同的使用模型以及實時測試示例來探討如何在實踐中利用這些加速器。

2020-12-28 06:26:54

,光纖配線箱為各種應用提供了更豐富的功能和更靈活的布線環境。選擇正確的光纖配線箱,充分利用光纖配線箱至關重要。下面我將告訴大家如何在數據中心里充分利用光纖配線箱,使布線環境更為靈活。靈活布線中的重要

2016-09-13 15:59:30

電子設計人員使用的工具箱日新月異。要找到適合工作的工具,不僅需要了解手頭上的任務和現有工具,還要知道如何充分利用這些工具。對于設計人員來說,在隔離柵內移動信號和電源是一項常見的挑戰。為了提高

2021-12-31 06:42:10

在之前的文章(《如何實現比4G快十倍?毫米波技術是5G的關鍵》)中我們介紹了如何利用毫米波技術獲得更多的頻譜資源,接下來的問題是如何充分利用這些頻譜資源——如何讓多個用戶通訊但又互不干擾,專業術語叫做頻譜復用。圖片來源:Phoenix

2019-07-11 07:09:25

普遍存在速度與處理級數的矛盾,有效解決此問題具有重要的現實意義。隨著片上系統(SOC)時代的到來,可編程邏輯器件不僅為FIR濾波器的設計提供了一條可行而高效的方法,而且更被廣泛地使用于數字信號處理

2019-07-30 07:22:48

(PermanentMagnet SynchronousMotor,PMSM)。電機控制硬件使用dsPIC30F外設,而數學運算則由DSP引擎完成。為充分利用 dsPIC30...

2021-08-27 07:29:05

如何去選擇數字信號處理器 (DSP)?

2021-05-25 07:20:05

在開關電源轉換器中,如何充分利用SiC器件的性能優勢?

2021-02-22 07:16:36

嗨!我已經創建了一個硬件加速器(在vhdl中)并且合成成功完成。但是,當我使用創建和導入外圍設備向導時,它向我顯示我的包在庫中不可用,盡管它是。我能做什么 ???L'enfer,c'est l

2019-02-27 14:15:31

來激勵電路仿真。本文詳細說明如何 使用LTspice音頻WAV文件生成不太為人所知的立體聲語法(以及更高的通道計數)。 《模擬對話》第54卷第二期本期內容摘要:充分利用數字信號處理器上的片內FIR

2020-11-17 11:26:14

各位大神,求助利用matlab解決數字信號處理的問題

2015-12-27 17:05:33

,它不但有完整的設計公式,而且還有較為完整的圖表供查詢,因此,充分利用這些已經有的資源會給數字濾波器的設計代理很大的方便。IIR數字率變頻器的設計步驟是:1. 按一定的規則將給出的數字濾波器的技術指標轉換

2016-09-29 08:35:33

的濾波輸出取決于當前輸入數據、歷史輸入數據和歷史輸出數據。以基于FPGA硬件的數字濾波器為例,FIR在處理信號時不需等待前一個信號的濾波輸出,只需要考慮輸入數據便可實時濾波;IIR需要等待上一個信號

2023-05-29 16:47:16

英特爾媒體加速器參考軟件是用于數字標志、交互式白板(IWBs)和亭位使用模型的參考媒體播放器應用軟件,它利用固定功能硬件加速來提高媒體流速、改進工作量平衡和資源利用,以及定制的圖形處理股(GPU)管道解決方案。該用戶指南將介紹和解釋如何為Linux* 使用英特爾媒體加速器參考軟件。

2023-08-04 06:34:54

讓你的內存每秒都能充分利用:內存釋放專家

2009-06-01 18:45:26

目前在用21489內部的IIR加速器去做一個低通濾波器,在例程的基礎上修改參數。通過Matlab的FDAtool去設計參數,但是設計出來的參數不知道如何對應加速器的濾波參數,手冊里也看得不是很明白。設計的參數如下:請問這些參數應該如何對應起來?

2018-11-09 09:40:51

如題C6745最高頻率465Mhz,此時有3648 MIPS 和 2736 MFLOPS的計算能力,如果單純對768K采樣率的信號做一個1024階的FIR濾波 大概會占用百分之多少呢 大概多少MIPS或者MFLOPS呢另外C6745內部有沒有FFT、IIR、FIR硬件加速器呢

2018-07-25 08:50:08

日前,德州儀器 (TI) 宣布推出采用控制律加速器 (CLA) 的新型 TMS320F2803x Piccolo 微處理器 (MCU),可促進具有更高可靠性與效率的嵌入式控制應用的開發。CLA

2019-07-26 06:21:46

問下ARM3的硬件加速器只能用verilog寫嗎?

2022-09-30 10:45:39

減輕計算密集型 2D FFT 運算負載的 FFTC 硬件加速器,可實現低延遲和高精度附加了 JESD 的寬帶采樣信號處理解決方案,包含數字信號處理器 (DSP)、ADC 和 DAC 板、演示軟件、配置

2018-09-20 09:07:06

數字信號處理本書的具體內容為:離散信號與系統分析基礎、離散傅里葉變換、離散傅里葉變換快速算法、IIR數字濾波器的設計、FIR數字濾波器的設計、功率譜估計、數字系統的結

2009-10-09 18:04:45 71

71 ADSP-21583處理器是新型、高性能、高效、實時系列的一部分,使用兩個增強型SHARC+?內核和先進的DSP加速器(FFT、FIR、IIR)提供高于24千兆/秒的浮點運算性能

2023-07-07 14:47:24

ADSP-SC584處理器是新型、高性能、高能效、實時系列的一部分,使用兩個增強型SHARC+?內核和先進的DSP加速器(FFT、FIR、IIR)提供高于24千兆/秒的浮點運算性能

2023-07-07 15:16:12

描述 ADSP-21587處理器是新的高性能、高能效、實時系列的一部分,使用兩個增強的SHARC+內核和先進的DSP加速器(FFT、FIR、IIR),每秒提供超過24千兆浮點運算

2024-01-08 14:25:00

充分利用MAXQ®處理器的非易失存儲服務

摘要:需要非易失數據存儲的應用通常都需要使用外部串行EEPROM。這篇文章介紹了僅使用MAXQ微控制器中已有的閃存提供非易失

2009-05-02 09:28:54 777

777

并行編程無進展使多核芯片未能充分利用

《福布斯》文章指出,為什么應用軟件總是無法充分利用芯片的強大功能呢?如何充分有效地利用處

2010-04-01 16:43:43 614

614 數字信號處理器(DSP)

數字信號處理器(digital signal processor, 簡寫 DSP)是一種專用于(通常為實時的)數字信號處理的微處理器。

2010-01-04 10:54:54 3403

3403 本文提出一種方案把數字信號處理部分從PC機軟件中分離出來交給DSP處理,DSP處理完畢后再把數據交還PC機進行管理。這樣充分利用DSP對數字信號高速處理的優勢,提高信號處理系統的實

2011-08-04 10:56:57 1296

1296

的實時性和靈活性,因此利用FPGA實現數字信號處理成為數字信號處理領域的一種新的趨勢。 以往基于FPGA的數字信號處理系統的模型及算法采用VHDL或VerilogHDL等硬件描述語言描述。但這些硬件描述語言往往比較復雜,而采用Altera公司推出的專門

2017-10-31 10:37:23 0

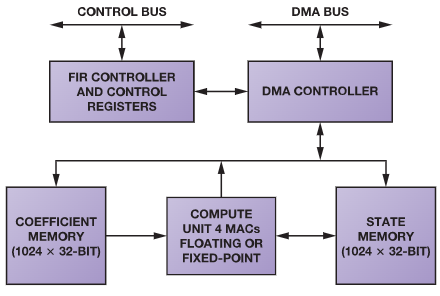

0 率超過兩倍。本文以下一代音頻系統為例,說明硬件加速器在這方面的應用。 為什么使用硬件加速器 FIR濾波器、IIR濾波器和FFT操作在數字信號處理器中應用十分普遍,且具有規則的結構,因此可以用硬件直接實現,特別是用硬件加速器。硬件加速器是專用

2017-12-04 15:22:36 1036

1036 很多人認為硬件加速器無非是一種速度更快的仿真器而已。毫無疑問,由于硬件加速器使用物理硬件進行仿真,使用硬件加速器驗證復雜的集成電路和大型片上系統(SoC)能比軟件仿真器快若干數量級。與仿真用通用計算機相比,仿真用單一功能計算機能提供更高容量、更高效的系統。

2018-03-28 14:50:00 3160

3160

正確利用硬件加速器對邏輯仿真進行加速是非常有效的。如果知道某項設計在仿真中的運行速度(用每秒仿真了多少設計時鐘來衡量),你就能很容易地估計出該設計的原始性能。舉個例子,我們假設仿真器以每秒1000

2018-03-05 10:13:13 3

3 本教程討論基于Xilinx FPGA的Memcached硬件加速器的技術細節,該硬件加速器可為10G以太網端口提供線速Memcached服務。

2018-11-27 06:41:00 3433

3433 硬件加速是指在計算機中通過把計算量非常大的工作分配給專門的硬件來處理以減輕中央處理器的工作量之技術。尤其是在圖像處理中這個技術經常被使用。

2019-08-15 15:29:35 6839

6839

硬件加速器提升下一代SHARC處理器的性能

2021-04-23 13:06:32 6

6 EE-408:使用ADSP-2156x高性能FIR/IIR加速器

2021-05-17 17:06:30 8

8 充分利用超級大寫電腦

2021-05-21 19:04:42 0

0 OpenHarmony 分論壇-華秋電子新硬件加速器 今天的華為開發者大會2021上,OpenHarmony分論壇上展示了華秋電子新硬件加速器 。 HDC分論壇-OpenHarmony 分論壇推薦鏈接:http://t.elecfans.com/live/1708.html 責任編輯:haq

2021-10-23 16:53:48 1500

1500

上的片內FIR和IIR硬件加速器也分別稱為FIRA和IIRA,我們可以利用這些硬件加速器來分擔FIR和IIR處理任務,讓內核去執行其他處理任務。在本文中,我們將借助不同的使用模型以及實時測試示例來探討如何在實踐中利用這些加速器。

2022-05-05 14:08:16 1034

1034 APS排程可以充分利用設備產能,提高設備利用率,減少停機換產損失,實現設備、人員、物料等約束。

2022-10-20 17:09:59 501

501

充分利用電位計 — 別讓旋轉亂套!

2022-11-07 08:07:15 0

0 處理器上的片上FIR和IIR硬件加速器(也稱為FIRA和IIRA)可用于卸載FIR和IIR處理任務,從而騰出內核用于其他處理。在本文中,我們將討論如何借助經過測試的實時示例說明的不同使用模型在實踐中使用這些加速器。

2022-12-20 11:22:36 855

855

處理器上的片上FIR和IIR硬件加速器(也稱為FIRA和IIRA)可用于卸載FIR和IIR處理任務,從而騰出內核用于其他處理。在本文中,我們將討論如何借助經過測試的實時示例說明的不同使用模型在實踐中使用這些加速器。

2022-12-20 11:39:25 782

782

借助硬件加速器開發您的設計

2023-01-03 09:45:15 594

594 SHARC ADSP-2146x處理器集成了硬件加速器,可實現三種廣泛使用的信號處理操作:FIR(有限脈沖響應)、IIR(無限脈沖響應)和FFT(快速傅里葉變換)。加速器卸載了核心處理器,并有可能使處理器的計算吞吐量增加一倍以上。本文以加速器在下一代音頻系統中的應用為例。?

2023-03-03 14:46:51 761

761

數字濾波器是數字信號處理中最常用的一種技術,可以對數字信號進行濾波、降噪、增強等處理,其中最常見的兩種數字濾波器是IIR濾波器和FIR濾波器。本文將從IIR濾波器和FIR濾波器的原理、特點和應用等方面進行詳細介紹,以便更好地理解兩種濾波器的區別。

2023-06-03 10:21:43 12912

12912 作為數字信號處理的一個實際任務就是要求能夠快速、高效、實時完成處理任務,這就要通過通用或專用的數字信號處理器來完成。因此,數字信號處理器是用來完成數字信號處理任務的一個軟、硬件環境和硬件平臺。

2023-08-07 16:58:08 630

630

電子發燒友App

電子發燒友App

評論