關鍵詞: 機載 , 記錄系統 , 視頻 , 數字

通過嵌入式計算機PC104對MPEG A/V編碼芯片SZ1510進行配置和控制,可以縮短研制高性能航空機載環境下數字式彩色視頻記錄儀的開發時間。文中詳細介紹了該機載數字視頻記錄系統的軟、硬件設計思想及注意事項。

機載視頻記錄系統在飛行員的日常訓練中發揮著十分重要的作用。該系統可以實時記錄飛行器的飛行及訓練過程中的各種信息,能夠直觀、真實的反映飛行員在空中的飛行和操作情況。通過地面回放設備的回放,飛行員可以準確地把握自身的不足并及時改進,從而提高訓練水平。但由于視頻信號數據量大,技術要求高,國產飛機大多沒有信息監視和記錄系統。為了提高我軍戰機的作戰性能?研制一種信息監視和記錄系統迫在眉睫。

隨著大規模集成電路的發展,采用數字圖像壓縮技術實現高壓縮比、高質量的圖像數字壓縮記錄系統已成為可能。數字化的記錄方法可以將視頻數據經過壓縮記錄在大容量的存儲器上,并能有效消除噪聲、增加記錄時間、加快拷貝和復制速度,快速回放和查找,同時還可以快速地通過計算機網絡進行傳送。基于以上原因,筆者為某新型飛機研制了高性能的適于航空機載環境的數字式彩色視頻記錄系統。本記錄系統的核心芯片選用以色列Zepax公司的SZ1510 MPEG-1編碼芯片。

1 工作原理

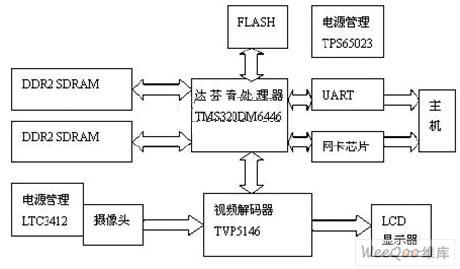

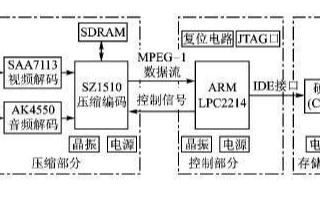

圖1所示是本記錄系統的結構組成示意圖。整個系統由三大部分組成,即壓縮控制部分、存儲部分和電源部分三大模塊。其中壓縮部分由一路MPEG-1音視頻壓縮電路和控制單元PC-104組成,主要功能是實現對輸入音視頻信號的數字壓縮。存儲部分由大容量硬盤組成,用于完成對壓縮數據的長時間記錄。電源部分負責對各模塊電路提供電源。

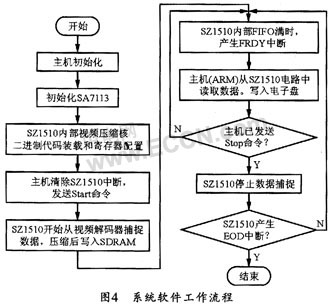

在系統啟動時,主控計算機首先對壓縮卡進行初始化,當設置好MPEG-1壓縮格式及數據速率后,壓縮卡開始工作,并在主控計算機的控制下將壓縮后的圖像數據寫入硬盤。在工作過程中,主控計算機還將不斷監視相關信號,并在圖像中加入相應的標志,直到接收到關機信號,系統自動結束壓縮卡的工作,并關閉主機。

2 系統硬件設計

整個系統的核心是以色列Zepax公司的SZ1510 MPEG-1編碼芯片,它由PC104控制,另外,該系統還包括PCI橋芯片PLX9030以及視頻解碼芯片SAA7113等。

2.1 SZ1510芯片簡介

Zepax公司的SZ1510IC內部采用可編程的專業硬件體系結構,它可以高效使用存儲器,并能合理進行資源分配。內核采用TI公司的TMS320C54X高性能DSP來完成MPEG1音頻編碼、解碼以及CD格式的音/視頻流的組合,同時進行一般的系統控制。

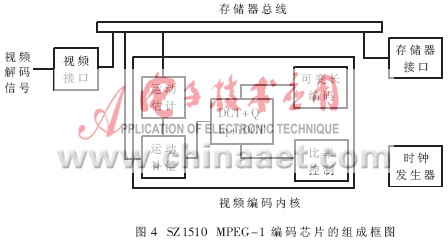

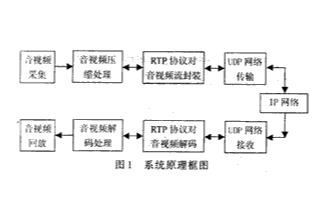

該芯片具有功能多、功耗小、溫度范圍寬等特點,其組成電路如圖2所示。它主要由運動估計與補償單元、DCT與反DCT變換單元、可變長編碼單元、控制單元、SDRAM接口單元、通用總線接口單元組成。內部的壓縮處理完全采用流水線結構,開機后只需簡單的初始化即可獨立工作,同時自動送出壓縮好的數據。外部電路的時鐘為27MHz,工作電壓為3.3V。

系統中的視頻壓縮有三種比特率可供選擇,其中恒定比特率需要填充冗余,最大比特率不需要填充冗余,而可變比特率的壓縮質量比較恒定,但比特率可變。音頻壓縮部分支持3244.1及48kHz取樣率以及音頻PCM、實時MPEG12層音頻編碼等。

2.2 PC104計算機簡介

考慮到控制單元的體積、可靠性和控制能力,可選用嵌入式計算機PC104作為主控單元。根據視頻壓縮的特點,推薦選擇安普公司的AmproP5E/266產品,該產品溫度特性好、功能強大、可靠性高、軟硬件移植方便且易于調試。

3 軟件設計

SZ1510共有128個寄存器,每個寄存器都有一個索引號。外界對這些寄存器的訪問都是通過IOAR I/O Adress Register 和IODR(I/O Data Register)來完成的。訪問時首先將這個寄存器的索引號寫入IOAR?然后將要寫的數據寫入IODR,這樣,SZ1510即可自動把數據送到某個寄存器。

主機訪問SZ1510是通過PLX9030進行的。對PLX9030中寄存器的訪問通常是按內存方式進行的,其方法是常規段加偏移方式。不過,它的寄存器訪問總線寬度有的是16bits(如0x4c),有的是32bits(如0x50),具體可參考有關文獻(5)。

3.1 硬件初始化

對系統硬件的初始化主要是初始化PLX9030和SZ1510。LX9030的初始化比較簡單,一是使能中斷,向寄存器0x4c中寫入0x0041,二是對PLX9030的Local bus進行軟復位,即先將寄存器0x50的第30位置1,再將其置0。

SZ1510的初始化過程如下:

(1)向中斷使能寄存器寫入0x40,以使能Ready中斷;

(2)等待SZ1510的Ready中斷;

(3)等到Ready中斷后,向SZ1510的0x1E寄存器寫入0x0A,設置它內部的DSP時鐘為94.5MHz;

(4)向0x013寄存器寫入0x55,對SZ1510進行軟復位;

(5) 向中斷使能寄存器0x0C寫入0x40?使能Ready中斷;

(6) 等候RDY中斷;

(7) 待Ready中斷后對SAA7113進行初始化;

(8) 對SZ1510進行軟復位,即向0x0B寄存器寫入0x55,同時向0x0C寄存器寫入0x40;

(9) 等待Ready中斷,等到后向SZ1510的內部DSP裝載二進制代碼;

(10)進行SZ1510內部視頻壓縮核的二進制代碼裝載。

3.2 SZ1510二進制代碼的裝載

SZ1510 內部有一段程序空間,可用來裝載二進制代碼。這段空間以塊(Blank)為單位,每塊的大小是256字節。

用于視頻編碼核的二進制代碼的裝載空間為0x000~0x004和0x00c等六個塊,共1.5k字節代碼。具體裝載的步驟如下:

(1) 向0x2E寄存器寫0x01,表示外部的SDRAM是1M%26;#215;16bits;

(2) 向0x0C寄存器寫0x03,使能FIFO Ready 和 End of Data中斷;

(3) 向0x11寄存器寫0x1,設定工作模式為內部內存寫模式;

(4)向0x10寫0x20,設定SZ1510?下轉第10頁 (上接第6頁)輸出數據的FIFO大小為256字節;

(5)對每塊程序空間進行二進制代碼裝載,具體過程如下:

●向0x08寄存器寫0x04,發送開始命令;

●等待Ready中斷,清除Ready中斷;

●向Data in寄存器0x01寫256個字節;

●等待End of Data中斷,然后清除中斷;

(6)查程序空間的代碼是否裝載完畢,如沒有,回到(5)繼續裝載。

3.3 SZ1510視頻數據的獲取

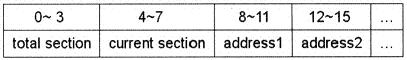

SZ1510內部有一個256字節的FIFO。一旦該FIFO滿,即產生一個FIFO Ready中斷,以通知主機讀取FIFO中的數據,然后通過256次讀Data out寄存器來完成數據傳輸。

4 注意事項

SZ1510芯片的PLL PCB設計要求如下

(1)應用設計EMI濾波裝置以減少VDDA的電源噪聲。

(2)LPF到SZ1510的整體電路管腳長度應當小于0.5英寸。

(3)設計PCB時,外部LPF應盡量接近封裝腳。

(4)VDDA和VSSA端應接0.1μF的旁路電容以減少噪音。

電子發燒友App

電子發燒友App

評論