本文探究的嵌入式多核處理器采用同構(gòu)結(jié)構(gòu),實(shí)現(xiàn)同一段代碼在不同處理器上的并行執(zhí)行。##緩存優(yōu)化(Cache friendly)的目標(biāo)是減少數(shù)據(jù)在內(nèi)存和緩存之間的拷貝。

2014-12-16 14:43:44 1377

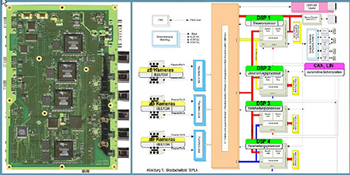

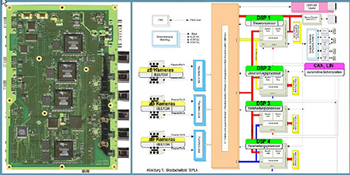

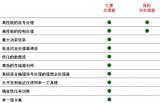

1377 視頻信號(hào),兩路分別輸出到外部顯示器上,視頻格式分別為高清LVDS和高清DVI。 高清視頻處理模塊主要功能電路包括圖形處理器電路、視頻疊加和縮放邏輯電路、編解碼電路和供電復(fù)位時(shí)鐘電路。模塊系統(tǒng)組成框圖

2018-11-07 10:42:22

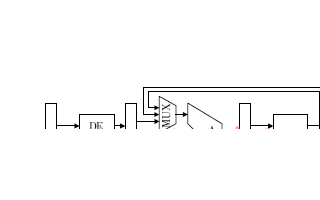

DSP技術(shù)廣泛應(yīng)用于各個(gè)領(lǐng)域,但傳統(tǒng)的數(shù)字信號(hào)處理器由于以順序方式工作使得數(shù)據(jù)處理速度較低,且在功能重構(gòu)及應(yīng)用目標(biāo)的修改方面缺乏靈活性。而使用具有并行處理特性的FPGA實(shí)現(xiàn)數(shù)字信號(hào)處理系統(tǒng),具有很強(qiáng)的實(shí)時(shí)性和靈活性,因此利用FPGA實(shí)現(xiàn)數(shù)字信號(hào)處理成為數(shù)字信號(hào)處理領(lǐng)域的一種新的趨勢(shì)。

2019-10-17 08:12:27

與多核處理器配合使用,那么從信號(hào)到最后測(cè)量的并行化測(cè)量就實(shí)現(xiàn)了。并行化測(cè)試利用多核處理器、PCI Express總線和LabVIEW軟件,用戶可以創(chuàng)建并行化的測(cè)量系統(tǒng),它們能夠同時(shí)測(cè)試一個(gè)待測(cè)單元

2014-12-12 16:02:30

處理器與音視頻外設(shè)之間怎么連接?

2021-06-08 06:46:15

處理器專家生成的代碼中是否有任何用于 MPC5748G 內(nèi)核之間通信的示例代碼。

我正在為 3 個(gè)不同的內(nèi)核使用處理器專家代碼,我想將數(shù)據(jù)從內(nèi)核 1 發(fā)送到內(nèi)核 2 進(jìn)行處理。例如,我從核心 1

2023-05-06 06:19:40

編程,說(shuō)明需要的結(jié)果,而不說(shuō)明如何計(jì)算。機(jī)器語(yǔ)言:機(jī)器語(yǔ)言的每條語(yǔ)句即是處理器可以直接執(zhí)行的一條指令,這些指令是以二進(jìn)制0、1序列的形式表示,對(duì)應(yīng)數(shù)字集成電路的高低電平。不同的處理器指令的機(jī)器代碼

2018-02-07 11:41:21

具有強(qiáng)大的處理能力,有許多算法實(shí)現(xiàn)時(shí)必須采用并行處理。因此,傳統(tǒng)的基于單內(nèi)核微控制器的解決方案面臨很大挑戰(zhàn),融合MCU及DSP的異構(gòu)雙處理器或多處理器解決方案,以及具有強(qiáng)大運(yùn)算能力的多內(nèi)核處理器是智能

2010-03-16 10:52:08

低功率模式經(jīng)常被忽視而沒(méi)有得到利用。有了現(xiàn)在的高性能嵌入式處理器,“開”或“關(guān)”不再是一個(gè)問(wèn)題。新的處理器可有多個(gè)狀態(tài),如運(yùn)行、打盹、小睡、睡眠以及深度睡眠模式等,每種狀態(tài)下對(duì)處理器時(shí)鐘、PLL以及

2019-07-15 06:40:13

功能實(shí)現(xiàn)自動(dòng)隊(duì)列監(jiān)控與管理。多內(nèi)核導(dǎo)航器可充分限制軟件開銷,降低同步時(shí)延,并可提高IPC吞吐量。此外,它還支持無(wú)鎖編程模型。圖2是使用多內(nèi)核導(dǎo)航器的IPC示意圖。圖2:使用多內(nèi)核導(dǎo)航器實(shí)現(xiàn)處理器間

2014-09-02 16:01:04

視頻后處理器PNX5100有什么作用?

2021-06-02 06:32:46

近年來(lái),隨著視頻監(jiān)控系統(tǒng)在各個(gè)領(lǐng)域的廣泛應(yīng)用,作為視頻監(jiān)控系統(tǒng)組成之一的多畫面處理器的應(yīng)用也愈來(lái)愈普遍。如使用一臺(tái)九畫面處理器,則可在一臺(tái)監(jiān)視器上同時(shí)監(jiān)控9個(gè)目標(biāo),只需使用一臺(tái)錄像機(jī)便可對(duì)9路視頻信號(hào)同時(shí)實(shí)時(shí)錄像。目前多畫面處理器有黑白/彩色四、九、十六畫面處理器等6種類型。

2019-09-18 06:55:45

的多功能指令。Blackfin處理器支持有限的指令級(jí)并行功能,一個(gè)32位指令可以與兩個(gè)16位指令并行發(fā)出,使得編程人員能在一個(gè)指令周期中使用許多內(nèi)核資源。Blackfin處理器的匯編語(yǔ)言使用代數(shù)語(yǔ)法,易于編碼和閱讀。該架構(gòu)經(jīng)過(guò)優(yōu)化,能夠與C/C++編譯器一起使用,軟件實(shí)現(xiàn)快速、高效。

2013-11-06 13:20:19

Cortex-M4內(nèi)核,Sitara AM57x處理器非常適用于那些不只需要單核性能的嵌入式應(yīng)用。這類集全部功能于一體的處理器賦予了靈活性全新的意義。AM57x處理器沒(méi)有幾乎相同的內(nèi)核,而是讓設(shè)計(jì)人

2018-09-04 09:54:55

該處理器包括一個(gè)內(nèi)核、一個(gè)嵌套的矢量化中斷控制器(NVIC)、高性能總線接口和其他功能。

該處理器包含以下功能:

·處理器核心。

·嵌套矢量化中斷控制器(NVIC)與處理器內(nèi)核緊密集成,實(shí)現(xiàn)低延遲

2023-08-18 06:09:49

ARM處理器中斷處理的編程是怎么實(shí)現(xiàn)的?

2021-04-27 06:46:53

本帖最后由 eehome 于 2013-1-5 10:10 編輯

ARM處理器啟動(dòng)代碼的分析與編程

2012-08-03 22:01:48

處理器內(nèi)核二、經(jīng)典ARM處理器編程模型三、Cortex-M4處理器四、STM32F407芯片簡(jiǎn)潔一、ARM處理器特點(diǎn)1.ARM處理器主要特點(diǎn)(1)ARM7系列采用馮諾依曼結(jié)構(gòu)(輸入輸出、控制器、存儲(chǔ)器、處理器),ARM9~11采用哈佛體系結(jié)構(gòu)(存儲(chǔ)器分為程序存儲(chǔ)器和數(shù)據(jù)存儲(chǔ)器)(2)屬于RISC型處理器結(jié)

2021-12-13 07:18:29

熟悉ARM軟件開發(fā)。

它旨在幫助您編寫ARMv8-A處理器的引導(dǎo)代碼。

您可以參考本應(yīng)用筆記中的引導(dǎo)代碼示例,并為基于ARMv8-A處理器的裸機(jī)系統(tǒng)編寫自己的引導(dǎo)代碼。

2023-08-23 06:20:29

字處理器內(nèi)核(The VLIW core)、一個(gè)可編程位流協(xié)處理器(The VLx)、視頻濾波協(xié)處理器(VF)、片內(nèi)存儲(chǔ)器、顯示刷新控制器(DRC)和大量可用的數(shù)字I/O接口組成。 BSP-15支持

2018-11-27 11:49:31

充當(dāng),利用DSP的HPI接口組成一個(gè)多DSP互 連并行系統(tǒng),一般是一個(gè)主處理器和一個(gè)從處理器,此種方法的一個(gè)應(yīng)用實(shí)例是在雷達(dá)中的應(yīng)用。滑窗算法是數(shù)字信號(hào)處理中一種常用的基本算法,但滑窗算法一般

2019-04-08 09:36:19

FPGA實(shí)現(xiàn)高速FFT處理器的設(shè)計(jì)介紹了采用Xilinx公司的Virtex - II系列FPGA設(shè)計(jì)高速FFT處理器的實(shí)現(xiàn)方法及技巧。充分利用Virtex - II芯片的硬件資源,減少?gòu)?fù)雜邏輯,采用

2012-08-12 11:49:01

的起始地址。開始真正的Linux內(nèi)核1、入口在arch/arm/kernel/head-armv.S2、查找處理器類型

2022-06-13 16:41:04

采用一種單指令多數(shù)據(jù)(SIMD)架構(gòu),這種架構(gòu)包含兩個(gè)能夠并行執(zhí)行代碼的運(yùn)算單元,這意味著用戶可以在這兩個(gè)運(yùn)算單元中于同一周期內(nèi)執(zhí)行相同的指令,速度最快的SHARC處理器的內(nèi)核時(shí)鐘頻率最高可達(dá)

2018-12-29 14:15:47

最近在關(guān)注SHARC處理器,因?yàn)檫@處理器在國(guó)內(nèi)音響中用的越來(lái)越多,剛才發(fā)現(xiàn)SHARC處理器編程參考(包含ADSP-2136x、ADSP-2137x和ADSP-214xx處理器)(修訂版2.4,2013年4月)PDF無(wú)法下載,請(qǐng)問(wèn)該文件是否不存在,對(duì)應(yīng)的正式編程參考是什么?

2023-11-30 07:22:04

STM32內(nèi)核處理器好用嗎

2015-09-02 19:38:10

處理器功能在硬件中實(shí)現(xiàn)以替代幾種軟件指令。通過(guò)減少多種代碼指令為單一指令,以及在硬件中直接實(shí)現(xiàn)指令的方式,從而實(shí)現(xiàn)代碼加速。最常用的協(xié)處理器是浮點(diǎn)單元(FPU),這是與CPU緊密結(jié)合的唯一普通協(xié)處理器

2015-02-02 14:18:19

與可編程邏輯以及可編程I/O。使用Zynq-7000 SoC您就可以在一顆芯片上實(shí)現(xiàn)復(fù)雜的、軟件驅(qū)動(dòng)控制的實(shí)時(shí)視頻處理。OmniTek OSVP可擴(kuò)展視頻處理器可在一個(gè)單一IP模塊提供完整的多視頻

2014-05-14 16:14:01

代碼加速和代碼轉(zhuǎn)換到硬件協(xié)處理器的方法如何采用FPGA協(xié)處理器實(shí)現(xiàn)算法加速?

2021-04-13 06:39:25

庫(kù)功能節(jié)省開發(fā)時(shí)間受益于使用高級(jí)編程語(yǔ)言(例如C或C ++)進(jìn)行編程,而不是通常用于專有DSP的手動(dòng)匯編程序該文章將介紹易于使用的Arm Cortex-M處理器上的信號(hào)處理功能,以及如何利用Arm

2022-07-29 14:48:46

恩智浦半導(dǎo)體(NXP Semiconductors)發(fā)布了一款具有專利的運(yùn)動(dòng)精確圖像處理(Motion Accurate Picture Processing)技術(shù)的視頻后處理器

2018-08-27 16:14:13

運(yùn)行中更換或重新啟動(dòng)幾乎所有的模塊,甚至是設(shè)備驅(qū)動(dòng)程序。QNX對(duì)多核處理器的支持基于其微內(nèi)核結(jié)構(gòu),通信被集成到QNX消息傳遞原語(yǔ),本地的IPC和遠(yuǎn)端節(jié)點(diǎn)間的IPC一樣。在單CPU上運(yùn)行的進(jìn)程分布到多

2019-06-29 08:30:00

類別:嵌入式系統(tǒng)處理器知識(shí)產(chǎn)權(quán)許可商ARMHoldingsplc已經(jīng)成功開發(fā)出雙內(nèi)核Cortex-A9處理器設(shè)計(jì)(被稱為Osprey)的兩個(gè)實(shí)現(xiàn)。Cortex-A9處理器能與其他Cortex系列

2021-12-13 06:03:17

傳統(tǒng)數(shù)字濾波器硬件的實(shí)現(xiàn)主要采用專用集成電路(ASIC)和數(shù)字信號(hào)處理器(DSP)來(lái)實(shí)現(xiàn)。FPGA內(nèi)部的功能塊中采用了SRAM的查找表(lo-ok up table,LUT)結(jié)構(gòu),這種結(jié)構(gòu)特別適用于并行處理結(jié)構(gòu),相對(duì)于傳統(tǒng)方法來(lái)說(shuō),其并行度和擴(kuò)展性都很好,它逐漸成為構(gòu)造可編程高性能算法結(jié)構(gòu)的新選擇。

2019-10-22 07:14:04

高性能處理器內(nèi)核。該處理器架構(gòu)基于一個(gè)10級(jí)RISC MCU/DSP流水線和一個(gè)專為實(shí)現(xiàn)最佳代碼密度而設(shè)計(jì)的混合16/32位指令集架構(gòu),該架構(gòu)很適合于高密度、大運(yùn)算量的圖像處理系統(tǒng); 高帶寬的DMA

2018-10-30 17:13:15

模塊。2 DSP芯片選型根據(jù)系統(tǒng)的性能要求,通過(guò)比較各種高性能DSP處理器,并著重對(duì)構(gòu)成并行處理系統(tǒng)的性能和便捷性進(jìn)行分析,確定選用AD公司的ADSP Tiger SHARC系列處理器中的TS201S組成多

2019-05-21 05:00:19

的降壓或升壓轉(zhuǎn)換器和低壓差線性穩(wěn)壓器(LDO),同時(shí)還需滿足上電和斷電時(shí)序、高精度耗電計(jì)量等需求,為用戶提供預(yù)計(jì)的剩余電池續(xù)航時(shí)間。由于多內(nèi)核架構(gòu)中時(shí)序要求非常關(guān)鍵,上電和斷電控制對(duì)應(yīng)用處理器尤為重要

2018-09-25 14:28:58

多內(nèi)核是指在一枚處理器中集成兩個(gè)或多個(gè)完整的計(jì)算引擎(內(nèi)核),多核處理器是單枚芯片(也稱為“硅核”),能夠直接插入單一的處理器插槽中,但操作系統(tǒng)會(huì)利用所有相關(guān)的資源,將它的每個(gè)執(zhí)行內(nèi)核作為分立的邏輯

2019-06-20 06:47:01

傅里葉變換、脈沖壓縮、線性預(yù)測(cè)編碼語(yǔ)音處理、高速定點(diǎn)矩陣乘法等,有較好的應(yīng)用前景和發(fā)展空間。那有誰(shuí)知道該如何利用FPGA實(shí)現(xiàn)級(jí)聯(lián)信號(hào)處理器嗎?

2019-07-30 07:22:48

USART串口輸出該怎樣去使用呢?如何利用USART串口輸出實(shí)現(xiàn)外部設(shè)備與處理器的通信?

2022-02-18 06:29:10

本文介紹的基于dsPIC30F的高精度數(shù)據(jù)采集器,利用了高精度、低噪聲、22位分辨率的新型Δ-Σ的A/D轉(zhuǎn)換器MCP3551進(jìn)行數(shù)據(jù)采樣轉(zhuǎn)換,實(shí)現(xiàn)了dsPIC30F微處理器與PC機(jī)的RS485通信功能,并能夠通過(guò)LED顯示輸出。

2021-05-11 06:24:49

應(yīng)用中編程(In-Application Program-ming,IAP)。利用在應(yīng)用中編程,僅需通過(guò)一根串口線,就可以完成產(chǎn)品固件的更新。本文對(duì)STM32處理器的在應(yīng)用中編程進(jìn)行了詳細(xì)的分析,結(jié)合硬件和驅(qū)動(dòng)給出了IAP的具體實(shí)現(xiàn)方法,稍加修改,便可應(yīng)用于STM32處理器的所有系列產(chǎn)品。

2020-11-24 06:42:43

小白求助,求大佬分享ARM處理器內(nèi)核列表

2021-10-25 08:27:54

,KeystoneI/II 等)主要研究:2、研究適合于嵌入式多核處理器及嵌入式云計(jì)算平臺(tái)的輕量級(jí)并行編程模型3、云計(jì)算平臺(tái)下,利用嵌入式多核眾核平臺(tái)進(jìn)行并行視頻分析處理技術(shù)二:構(gòu)建嵌入式云計(jì)算平臺(tái)兩種方法:1、在

2014-07-19 14:27:26

嵌入式是不是把linux的內(nèi)核代碼修改好了燒入arm處理器中,再把編寫好的應(yīng)用程序的代碼燒入arm處理器中?還是系統(tǒng)和應(yīng)用程序一起做好,一起寫入到arm處理器中?

2022-05-31 09:33:56

和可編程I/O選項(xiàng)需要處理器來(lái)實(shí)現(xiàn)與多種工業(yè)電機(jī)驅(qū)動(dòng)器和工廠自動(dòng)化設(shè)備的對(duì)接。由于網(wǎng)絡(luò)互連與目前工程設(shè)計(jì)領(lǐng)域的融合度越來(lái)越高,可編程實(shí)時(shí)單元工業(yè)通信子系統(tǒng)(PRU-ICSS) 使得設(shè)計(jì)人員能夠利用任何

2018-09-04 10:07:50

微處理器的結(jié)構(gòu)是由哪些部分組成的?微處理器的代碼是如何執(zhí)行的呢?

2022-02-28 09:25:10

怎么利用FPGA和嵌入式處理器實(shí)現(xiàn)低成本智能顯示模塊?

2021-04-28 07:10:33

怎么實(shí)現(xiàn)多內(nèi)核處理器開發(fā)趨勢(shì)下的高性能視頻系統(tǒng)設(shè)計(jì)?

2021-06-03 06:19:40

FPGA的嵌入式應(yīng)用。某人工神經(jīng)網(wǎng)絡(luò)的FPGA處理器能夠?qū)?shù)據(jù)進(jìn)行運(yùn)算處理,為了實(shí)現(xiàn)集數(shù)據(jù)通信、操作控制和數(shù)據(jù)處理于一體的便攜式神經(jīng)網(wǎng)絡(luò)處理器,需要設(shè)計(jì)一種基于嵌入式ARM內(nèi)核及現(xiàn)場(chǎng)可編程門陣列FPGA的主從結(jié)構(gòu)處理系統(tǒng)滿足要求。

2019-09-20 06:15:20

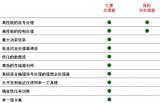

本文旨在介紹一種全新的多內(nèi)核平臺(tái),其能夠通過(guò)優(yōu)化內(nèi)核通信、任務(wù)管理及存儲(chǔ)器接入實(shí)現(xiàn)高密度視頻處理能力,此外,本文還闡述了擴(kuò)展實(shí)施的結(jié)果如何支持多通道和多內(nèi)核 HD 視頻應(yīng)用的高密度視頻處理。

2021-06-01 06:20:28

?DaVinci是一款高度集成的片上系統(tǒng)(SoC),集成了數(shù)字視頻所需的幾乎全部組件??TMS320C64x+DSP內(nèi)核+ARM926處理器+視頻加速器??10/100M網(wǎng)口??主/從USB口

2011-09-14 10:06:11

為了提升性能同時(shí)降低功率要求,在處理器中增加內(nèi)核已經(jīng)成為計(jì)算和嵌入式處理器產(chǎn)業(yè)的標(biāo)準(zhǔn)作法。雖然同樣的演變對(duì)各種高性能處理來(lái)說(shuō)似乎是不可避免的,以往的經(jīng)驗(yàn)使得數(shù)字信號(hào)處理器(DSP)供應(yīng)商更愿意選擇

2009-04-09 23:14:41

有什么方法可以實(shí)現(xiàn)視頻代碼轉(zhuǎn)換嗎?

2021-06-08 09:44:06

卻沒(méi)有增加,這是由于引腳數(shù)量和裸片尺寸所限。由于控制平面、數(shù)據(jù)平面和業(yè)務(wù)代碼都具有不同大小的指令占位、進(jìn)程狀態(tài)和共享數(shù)據(jù),因此多內(nèi)核處理器必須能夠高效地劃分存儲(chǔ)器資源。芯片上的緩存分配機(jī)制和緩存層次越

2019-05-16 10:45:11

隨著多核成為處理器的發(fā)展主流,對(duì)于并行編程(多線程編程)也成為了開發(fā)人員最大的難題,而LabVIEW憑借自身的并行特性可以直觀地實(shí)現(xiàn)多線程的編程方式。僅僅憑借自動(dòng)多線程的特性,還無(wú)法充分地利用多核

2012-01-10 13:48:42

一種基于多內(nèi)核處理器的高性能視頻系統(tǒng)設(shè)計(jì)

2021-06-07 07:07:40

到來(lái)的腳步,10比特甚至12比特的處理技術(shù)在視頻處理器中的應(yīng)用已是大勢(shì)所趨。 二、分辨率規(guī)格轉(zhuǎn)換:一般來(lái)說(shuō),圖像信號(hào)源(例如藍(lán)光DVD、電腦、高清播放盒等)提供的信號(hào)分辨率都有固定的規(guī)格(參考VESA

2012-01-17 17:08:53

系列中 FXT 系列的最新硬件處理器 Xilinx? PowerPC? 440 可提供超標(biāo)量功能,讓用戶能夠?qū)ζ骷?b class="flag-6" style="color: red">編程,使其以高達(dá) 550 MHz 的時(shí)鐘速率并行執(zhí)行一個(gè)或兩個(gè)定點(diǎn)運(yùn)算。盡管用戶能通過(guò)

2018-08-03 11:15:23

LabVIEW的多傳感器信息采集平臺(tái),將多傳感器數(shù)據(jù)采集、預(yù)處理、信息顯示、存儲(chǔ)及數(shù)據(jù)回放集成在一起,解決了以往實(shí)現(xiàn)多傳感器信息同步十分困難的問(wèn)題,為將來(lái)進(jìn)一步研究利用虛擬儀器測(cè)量多傳感器信息及進(jìn)行多傳感器信息

2019-06-03 07:40:04

的媒體處理器MD-32特有的體系結(jié)構(gòu)特點(diǎn),提出C編譯器支持的,在匯編代碼級(jí)通過(guò)指令調(diào)度和轉(zhuǎn)換指令操作數(shù)及其類型的代碼優(yōu)化方法,實(shí)現(xiàn)輸出高效的并行指令。統(tǒng)計(jì)數(shù)據(jù)表明:代碼執(zhí)行效率平均可以提高l5%,而代碼密度平均提高12%。

2011-03-03 10:46:37

數(shù)字媒體處理器是高度集成、成本有效、低功耗、可編程平臺(tái),此平臺(tái)利用 TI 的 DaVinci 處理器技術(shù)來(lái)滿足汽車黑匣子數(shù)字視頻記錄儀、便攜式數(shù)字視頻記錄儀,以及

2022-12-14 14:40:32

要求 。 T31A提供高速CPU算力,出色的圖像信號(hào)處理,流暢的2048x2048分辨率視頻錄制。 CPU(中央處理器)內(nèi)核,配備

2022-12-20 09:45:41

。T31ZX提供高速CPU計(jì)算能力,出色的圖像信號(hào)處理,流暢的2048x2048分辨率視頻錄制。 CPU(中央處理器)內(nèi)核,配備 32k

2022-12-20 10:46:13

的高速緩存架構(gòu)、增強(qiáng)的DMA子系統(tǒng),以及動(dòng)態(tài)電源管理(DPM)功能。這些新的系列成員與現(xiàn)有的Blackfin處理器代碼兼容,使系統(tǒng)設(shè)計(jì)人員能夠利用處理器內(nèi)核結(jié)合的控制與

2023-07-07 11:59:09

新型存儲(chǔ)器配置。這些器件均與先前推出的所有SHARC處理器引腳兼容并實(shí)現(xiàn)了代碼全兼容。這些SHARC處理器系列的最新成員基于一個(gè)單指令、多數(shù)據(jù)(SIMD)內(nèi)核(該內(nèi)

2023-07-07 16:23:15

恩智浦推出業(yè)內(nèi)首顆實(shí)現(xiàn)單芯片3DTV等功能的視頻協(xié)處理器

恩智浦半導(dǎo)體公司(NXP)日前宣布推出業(yè)內(nèi)第一個(gè)能夠在單芯片中實(shí)現(xiàn)3DTV、幀速率轉(zhuǎn)換(FRC)和局部背光調(diào)光功能

2009-12-23 08:40:42 532

532 分享Accuon技術(shù)RGB/視頻并行處理技術(shù)

在信號(hào)處理方面,Accuon已經(jīng)不再停留在依賴網(wǎng)絡(luò)圖像處理器的階段,在此基礎(chǔ)上開發(fā)了世界獨(dú)創(chuàng)的RGB/視頻并行處

2010-02-11 14:51:19 438

438 多內(nèi)核處理器開發(fā)趨勢(shì)下的高性能視頻系統(tǒng)設(shè)計(jì)

時(shí)鐘頻率的提高帶來(lái)的高功耗、深亞微米半導(dǎo)體制造工藝漏電流產(chǎn)生的高功耗以及更多的設(shè)計(jì)挑戰(zhàn)促使處理器設(shè)計(jì)制造

2010-03-04 10:02:55 691

691

設(shè)計(jì)了一款新的應(yīng)用于 多媒體處理 領(lǐng)域的可重構(gòu)多媒體流處理器。該可重構(gòu)多媒體 流處理器 采用并行處理機(jī)制,在經(jīng)過(guò)算法映射后,可以充分利用多媒體算法的高并行度,同時(shí)實(shí)時(shí)處

2011-08-18 14:48:29 21

21 視頻代碼轉(zhuǎn)換是指從一種壓縮視頻格式轉(zhuǎn)換為另一種壓縮視頻格式,通常先要把某種格式解碼為原始視頻幀,然后用新的格式重新編碼。在許多應(yīng)用中高效的代碼轉(zhuǎn)換至關(guān)重要。

2011-09-24 01:02:57 851

851 基于Cortex_M4內(nèi)核微處理器的新型智能小車設(shè)計(jì)與實(shí)現(xiàn)

2017-09-25 13:02:40 8

8 無(wú)需更多編程努力。 此外,圖形化LabVIEW代碼還有助工程師與科學(xué)家可視化顯示并行操作,因?yàn)樗焐砉I(yè)和院校采用的最流行并行編程模式。 并行編程的挑戰(zhàn) 并行編程正很快成為用來(lái)構(gòu)建大多數(shù)多核處理器的必要。

2017-11-16 19:30:41 1287

1287

多核處理器、FPGA和PCI Express正在改變現(xiàn)代PC機(jī)的版圖,并幫助LabVIEW圖形化編程根據(jù)工程師應(yīng)用邏輯的數(shù)據(jù)流向,實(shí)現(xiàn)真正的并行化處理和并行化測(cè)量。利用NI TestStand軟件

2017-11-16 20:31:57 8828

8828

并行處理器指可以一次可處理多個(gè)運(yùn)算的處理器。雙核處理器也是并行處理器,因?yàn)槠湟淮慰蛇\(yùn)行兩個(gè)運(yùn)算(以此類推),但其本質(zhì)上還是串行處理器的組合,所以提起并行處理器,一般指經(jīng)特殊設(shè)計(jì)的多線程處理器。

2017-12-08 10:40:20 2927

2927 針對(duì)當(dāng)前大量遺產(chǎn)代碼無(wú)法重復(fù)利用的問(wèn)題,設(shè)計(jì)一種新的編譯工具將C的串行代碼轉(zhuǎn)換為基于MPI+OpenMP的混合并行編程代碼,降低了并行編程的開發(fā)成本。首先,通過(guò)對(duì)JavaCC的優(yōu)化,實(shí)現(xiàn)一種可以解析

2017-12-12 14:53:39 0

0 關(guān)鍵詞:處理器 , 高性能 , 內(nèi)核 , 趨勢(shì) , 視頻系統(tǒng) 時(shí)鐘頻率的提高帶來(lái)的高功耗、深亞微米半導(dǎo)體制造工藝漏電流產(chǎn)生的高功耗以及更多的設(shè)計(jì)挑戰(zhàn)促使處理器設(shè)計(jì)制造商開始將思路轉(zhuǎn)向到多內(nèi)核集成

2019-03-02 07:51:01 321

321

指令均勻地分配給芯片中的眾多執(zhí)行單元。本設(shè)計(jì)是針對(duì)VLIW微處理器的基本功能設(shè)計(jì)實(shí)現(xiàn)的,是針對(duì)64位指令字和192位數(shù)據(jù)進(jìn)行操作處理,主要功能是將指令和數(shù)據(jù)分別劃分到3個(gè)并行操作單元中,在執(zhí)行單元中根據(jù)3個(gè)并行指令控制,對(duì)3個(gè)并行操作單元的數(shù)據(jù)進(jìn)行并行處理,同時(shí)對(duì)操作處理數(shù)據(jù)進(jìn)行存儲(chǔ)處理管理。

2020-01-31 16:55:00 922

922

介紹了一種視頻處理器的設(shè)計(jì),該處理器接收數(shù)字YCbCr視頻信號(hào),利用一片DDR2SDRAM存儲(chǔ)器作為幀緩存,對(duì)接收的視頻信號(hào)進(jìn)行格式轉(zhuǎn)換,幀率提升,色空間轉(zhuǎn)換。提出并實(shí)現(xiàn)一種改進(jìn)的自動(dòng)聚焦算法,實(shí)時(shí)

2021-03-31 09:24:16 5

5 EE-263:在TigerSHARC?處理器上并行實(shí)現(xiàn)定點(diǎn)FFT

2021-05-16 08:53:56 2

2 Blackfin 處理器包括一個(gè)具有 10 級(jí) RISC MCU/DSP 流水線的高性能 16/32 位嵌入式處理器內(nèi)核、用于實(shí)現(xiàn)最佳代碼密度的可變長(zhǎng)度 ISA 以及具有面向加速視頻和多媒體處理的指令的全 SIMD 支持。

2023-08-07 17:00:04 397

397 訊維視頻處理器就是我們?cè)诒O(jiān)控系統(tǒng)中經(jīng)常運(yùn)用到的畫面處理器,它的主要功能就是將多監(jiān)控?cái)z像機(jī)的監(jiān)控畫面同時(shí)顯示在一臺(tái)輸出顯示設(shè)備上。現(xiàn)在大多視頻畫面分割器有4分割、9分割、16分割和32分割,就是分別

2023-08-24 16:39:34 346

346 LED視頻處理器又叫畫面處理器,圖像轉(zhuǎn)換器、視頻控制器、圖像處理器畫面轉(zhuǎn)換器、視頻格式轉(zhuǎn)換器獨(dú)立視頻源等。

2023-12-13 16:09:21 530

530 視頻處理器是一種專門用來(lái)處理視頻信號(hào)的器件或組件。它的主要作用是對(duì)輸入的視頻信號(hào)進(jìn)行處理和優(yōu)化,從而提高畫質(zhì)、增強(qiáng)效果、提供更好的音視頻體驗(yàn)。視頻處理器通常由多個(gè)功能模塊組成,每個(gè)模塊負(fù)責(zé)不同的處理

2024-02-01 17:23:33 503

503

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論