基于LPC2210和SZ1510的車載數(shù)字視頻壓縮記錄系統(tǒng)設(shè)計

近些年來,計算機(jī)技術(shù)、多媒體技術(shù)和數(shù)據(jù)通信技術(shù)的發(fā)展飛速,促使數(shù)字視頻的應(yīng)用也越來越廣(如視頻監(jiān)控、視頻會議和移動電視等)。隨后,各種壓縮算法的研究使得數(shù)字視頻的存儲和傳輸極為方便,同時也相繼出現(xiàn)了各種視頻記錄系統(tǒng)。本文設(shè)計的嵌入式視頻記錄系統(tǒng),可以將攝像頭拍攝到的模擬視頻數(shù)據(jù)轉(zhuǎn)變成數(shù)字視頻數(shù)據(jù),經(jīng)壓縮后存儲在大容量的存儲器上,并可通過專用的回放設(shè)備再現(xiàn)汽車行使的整個過程。該視頻記錄系統(tǒng)可用來記錄汽車內(nèi)各項(xiàng)儀表和前方外視景等視頻信息及突發(fā)事件標(biāo)記,它可以將汽車行使過程中的所有信息以數(shù)字視頻的方式連續(xù)動態(tài)地記錄下來。本系統(tǒng)可以和汽車黑匣子結(jié)合,以方便管理部門根據(jù)所記錄的有關(guān)數(shù)據(jù)對車輛進(jìn)行有效的管理,更能為事故后的分析提供準(zhǔn)確的依據(jù),判斷汽車肇事的真正原因。同時可以通過記錄查看平常是否緊急加速、是否急剎車等行駛數(shù)據(jù),以此分析并改善不良駕駛習(xí)慣,起到預(yù)防事故的作用。

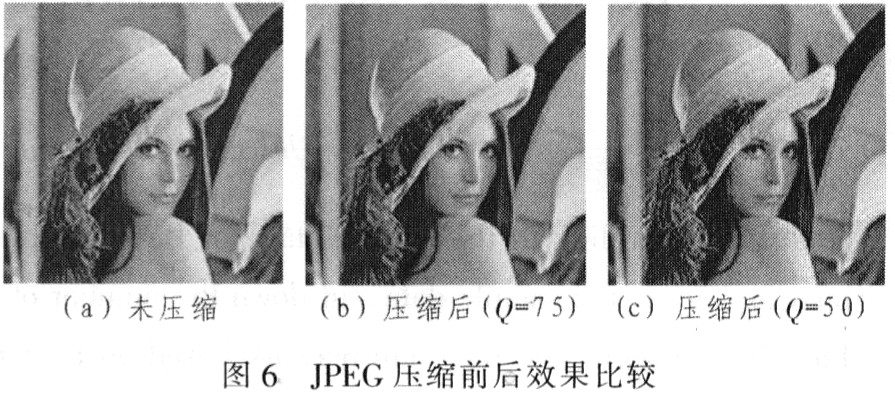

常見的視頻壓縮方法有MPEG系列租H.26X系列。考慮到壓縮技術(shù)的成熟度、成本和主要用途,本記錄系統(tǒng)采用MPEG-1數(shù)字圖像壓縮記錄技術(shù),來實(shí)現(xiàn)對1路視頻信號的連續(xù)圖像長達(dá)4小時的實(shí)時循環(huán)記錄。此外,本視頻記錄系統(tǒng)還具有成本低、體積小、功耗低等特點(diǎn)。

1 系統(tǒng)工作原理

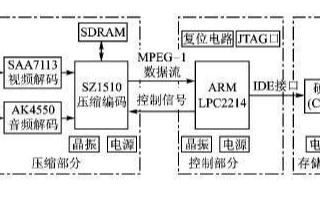

視頻記錄系統(tǒng)設(shè)計的側(cè)重點(diǎn)是降低成本,減小體積,同時降低系統(tǒng)的功耗,提高系統(tǒng)的整體性能。它能夠?qū)ζ嚿系?路視頻信號進(jìn)行長達(dá)4小時的連續(xù)實(shí)時動態(tài)循環(huán)記錄。本系統(tǒng)主要由視頻解碼及壓縮編碼器、ARM處理器、電子盤三部分組成。其中視頻解碼器和壓縮編碼器共同組成壓縮單元,ARM處理器是系統(tǒng)的控制單元,電子盤是系統(tǒng)的存儲單元。其視頻記錄系統(tǒng)的結(jié)構(gòu)組成如圖1所示。系統(tǒng)工作時,先將攝像機(jī)拍攝到的視頻信號通過視頻解碼器SAA7113H進(jìn)行解碼和A/D轉(zhuǎn)換,以輸出8位4:2:2格式的YCbCr數(shù)字視頻信號,該數(shù)字化視頻信號送入SZ1510壓縮編碼芯片進(jìn)行壓縮后可產(chǎn)生MPEG-1數(shù)據(jù)流,然后由ARM處理器將壓縮好的數(shù)據(jù)通過IDE接口存入存儲載體——電子盤,從而實(shí)現(xiàn)對1路視頻信號的連續(xù)實(shí)時循環(huán)記錄。

系統(tǒng)上電并啟動后,ARM處理器首先通過SZ1510芯片的HOST接口對SZ1510內(nèi)部寄存器進(jìn)行配置,并通過I2C總線對視頻解碼器SAA7113H進(jìn)行初始化。當(dāng)設(shè)置好MPEG-1壓縮格式及數(shù)據(jù)速率后,系統(tǒng)開始正常工作,并對輸入的模擬視頻信號經(jīng)視頻解碼器進(jìn)行解碼和A/D轉(zhuǎn)換,再將生成的CCIR-601數(shù)字視頻流傳人壓縮編碼芯片SZ1510進(jìn)行處理,然后由SZ1510將數(shù)字視頻數(shù)據(jù)轉(zhuǎn)化為符合MPEG-1格式的影視文件,最后將MPEG-1數(shù)據(jù)流在ARM處理器的控制下通過IDE接口以文件形式寫入電子硬盤進(jìn)行存儲。系統(tǒng)工作時,ARM還將不斷監(jiān)視相關(guān)信號,并在圖像中加入相應(yīng)的標(biāo)志,直到接收到關(guān)機(jī)信號,系統(tǒng)自動結(jié)束壓縮工作。

2.1 視頻解碼及壓縮編碼電路設(shè)計

由于MPEG-1壓縮算法需要很大的運(yùn)算量,用軟件很難實(shí)時完成,所以本系統(tǒng)采用專用的視頻壓縮芯片來實(shí)現(xiàn)對視頻信號的實(shí)時高效壓縮。目前,常用的MPEG-1壓縮芯片有VW2010、W99200F、WIS 7007SB等。本設(shè)計選用SAA7113H進(jìn)行解碼,并采用Zapex公司的SZ1510MPEG-1 A/V編碼芯片進(jìn)行圖象壓縮。SAA7113的主要作用是把輸入的模擬視頻信號解碼成標(biāo)準(zhǔn)的8位“VPO”數(shù)字信號,它相當(dāng)于一種“A/D'’器件,是一種可編程視頻處理芯片,可通過I2C總線實(shí)現(xiàn)編程控制,并具有4路視頻輸入、抗混疊濾波、自動鉗位和增益控制、多制式解碼以及亮度、對比度和飽和度控制等功能。它對輸人的PAL制式視頻信號進(jìn)行采樣和解碼后,可將生成的CCIR-601數(shù)字視頻流(色度空間為YCbCr,取樣為4:2:2)送到視頻壓縮芯片SZ1510的數(shù)字視頻輸入接口。它的輸入時鐘由24.576 MlHz的有源晶振提供,并可分別從RTS1和RTS0管腳輸出為SZ1510提供的行同步信號HS和場同步信號VS,其中行同步信號HS又可作為行有效象素識別信號輸入到SZ1510的VIHACT管腳;并從LLC腳輸出27 MHz的像素時鐘,作為SZ1510內(nèi)部的數(shù)字視頻流的采樣時鐘和芯片的主時鐘。系統(tǒng)初始化可通過ARM芯片的I2C總線來實(shí)現(xiàn)。片選信號由ARM產(chǎn)生RESET信號來提供。

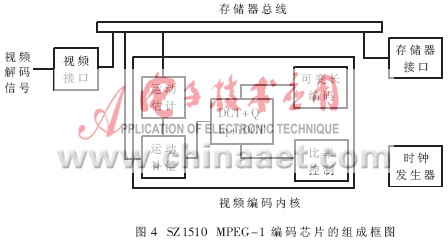

系統(tǒng)中的壓縮編碼芯片SZ1510是ZAPEX公司生產(chǎn)的一款高性能的MJPEG、MPEG-1編碼芯片,可對視頻信號實(shí)現(xiàn)高達(dá)25 f/s的壓縮,并支持多種工作模式和比特率模式,還可靈活實(shí)現(xiàn)模式組合,同時可在視頻中疊加視頻標(biāo)記和時間標(biāo)記。該芯片內(nèi)部主要由視頻編碼核、TMS320C54X高性能DSP核、接口電路(視頻接口、存儲器接口、主機(jī)與串口接口)、DMA控制器和時鐘產(chǎn)生電路等組成。其內(nèi)部的壓縮核已經(jīng)過優(yōu)化,適合于高效、實(shí)時的MPEG-1數(shù)字圖像壓縮,且具有功能多、功耗低、溫度范圍寬等特點(diǎn)。

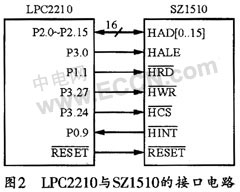

系統(tǒng)中的SZ1510是從設(shè)備,受主機(jī)ARM的控制。它的HOST接口是控制和數(shù)據(jù)交換的接口。SZ1510可以選擇多種總線類型,它有復(fù)用和不復(fù)用的Intel和Motorola總線類型(復(fù)用模式下,HAD[7:0]即可作為數(shù)據(jù)線,又可作為地址線;非復(fù)用模式時,HAD[7:0]只能作為數(shù)據(jù)線),不復(fù)用總線又可分為8位和16位,并可由HCONFIG[l:0]引腳和Syscofig[3]寄存器進(jìn)行選擇配置。本系統(tǒng)把HCONFIG0置低,HCONFIG1置高,Sysconfig[3]寫1,故可使其工作在Intel 8051類型的非復(fù)用16位數(shù)據(jù)總線模式下。

由于SZ1510有多種工作模式,根據(jù)系統(tǒng)要求,本設(shè)計使SZ1510工作在LVE(Live Video Encoding)實(shí)時視頻編碼模式。在這種模式下,SZ1510可從視頻解碼器獲得實(shí)時數(shù)字視頻數(shù)據(jù),然后根據(jù)MPEG1/M-JPEG進(jìn)行壓縮并傳到主機(jī)。具體工作過程是:SZ1510對輸入到其內(nèi)部的CCIR-601數(shù)字視頻流經(jīng)過視頻預(yù)處理、自動裁減、場景變化檢測、運(yùn)動估計、運(yùn)動補(bǔ)償、離散余弦變換/反離散余弦變換和可變長編碼等處理后,再將生成的MPEG-1視頻基本流存儲于SDRAM中,然后經(jīng)過輸出端口大小為256字節(jié)的FIFO緩沖進(jìn)行數(shù)據(jù)輸出。正常工作時,F(xiàn)IFO每滿一次就產(chǎn)生一個FRDY (FIFO讀)中斷以通知主機(jī)讀取FIFO中的數(shù)據(jù),并由主機(jī)從Data_out寄存器讀取數(shù)據(jù)。之后,當(dāng)SZ1510發(fā)出一個EOD(數(shù)據(jù)結(jié)束)中斷時,數(shù)據(jù)傳輸結(jié)束。

在視頻壓縮工作模式下,SZ1510有3種輸出比特率可供選擇:恒定比特率、最大比特率、可變比特率。恒定比特率需要填充冗余,最大比特率不需要填充冗余,可變比特率的壓縮質(zhì)量比恒定比特率可變。比特率的選擇可通過設(shè)置Ven_cntl寄存器的1、2位來確定,當(dāng)其為0時,選擇的是恒定比特率;為1時,選擇的是最大比特率;為3時,選擇的是可變比特率。

2.2 控制及存儲電路設(shè)計

考慮到控制部分的體積、可靠性和控制能力,本系統(tǒng)中的CPU采用Philips公司的ARM7TD-MI-S內(nèi)核微控制器LPC2210。這是一個能夠支持實(shí)時仿真和跟蹤的16/32位ARM7TDMI-S CPU。對于代碼規(guī)模有嚴(yán)格控制的應(yīng)用,可使用16位Thumb模式,該模式可將代碼規(guī)模降低30%以上,而性能的損失卻非常小。LPC2210采用144腳封裝,具有極低的功耗。另外,該芯片還具有多個32位定時器、8路10位ADC、PWM輸出以及多達(dá)9個外部中斷。通過配置總線,LPC2210最多可提供76個GPIO。

LPC2210可與SZ1510的HOST接口相連,并可通過HOST接口對SZ1510進(jìn)行控制和設(shè)置。正常工作時,LPC2210把從HOST接口輸出的MPEG-1格式視頻流以文件形式送人電子盤進(jìn)行存儲。LPC2210與SZ1510的接口電路如圖2所示。其中,HAD[0…15]接到ARM的P2.0~P2.15A作為16根數(shù)據(jù)線;P3.0接到HALE腳可實(shí)現(xiàn)SZ1510內(nèi)部IOAR(I/O Address Registerl)和IODR(I/O DataRegister)寄存器的選擇;P1.1和P3.27分別接讀、寫選通管腳HRD和HWR;通過將P3.24接到HCS可選通SZ1510;將P0.9接到HINT可發(fā)送SZ1510中斷請求信號。

從重量和可靠性出發(fā),本記錄單元最終選用電子盤來實(shí)現(xiàn)。該電子盤的主體為Flash芯片,該芯片耐沖擊,耐高溫,體積小,壽命長,適合在汽車環(huán)境下工作。雖然電子盤的價格昂貴,但是考慮到系統(tǒng)只采集1路視頻信號,記錄的數(shù)據(jù)量也不是很大(計算后得出記錄單元的容量為3G時),記錄長度可達(dá)4.5個小時,所以,選用電子盤完全能夠?qū)崿F(xiàn)任務(wù)要求。

LPC2210的GPIO引腳與IDE接口的連接電路如圖3所示。圖中,P2.16~P2.31為數(shù)據(jù)線,P1.16~P1.20為地址和選通信號,P0.17和P0.20為設(shè)備的復(fù)位和狀態(tài)請求信號,用P0.21和P0.19則可實(shí)現(xiàn)讀寫控制。

3 系統(tǒng)軟件設(shè)計

本系統(tǒng)的所有軟件程序事先均應(yīng)通過JTAG口燒錄到ARM中,這樣,系統(tǒng)上電后便可自動運(yùn)行這些程序以控制系統(tǒng)的工作。系統(tǒng)軟件工作流程圖如圖4所示。

3.1 SZ1510的寄存器配置

SZ1510有128個寄存器,每個寄存器都有一個索引號,外部主機(jī)是通過HOST接口(HALE管腳)來設(shè)置SZ1510內(nèi)部的兩個寄存器IOAR (I/O地址寄存器)、IODR(I/O數(shù)據(jù)寄存器)以實(shí)現(xiàn)對SZ1510的控制和配置。訪問時,首先由主機(jī)的A0管腳發(fā)送一個低電平到HALE管腳以選中IOAR寄存器,然后將要訪問的寄存器索引號寫入IOAR;接著由主機(jī)的A0管腳發(fā)送一個高電平到HALE管腳,以選中IODR寄存器,然后再將要寫入的數(shù)據(jù)寫入IODR,這樣,SZ1510就會自動把配置的數(shù)據(jù)送到指定地址的寄存器。

對Z1510進(jìn)行初始化時,先由主機(jī)寫任意值到0x0B寄存器;接著在主機(jī)至少等待1微秒后,向Int_enable中斷使能寄存器寫入0x40,以使能RDY(Ready)中斷;然后,主機(jī)便等待SZ1510的Ready(Int_source[6])中斷;之后,當(dāng)主機(jī)等到RDY中斷后,它將清除RDY中斷并開始向SZ1510的內(nèi)部DSP裝載二進(jìn)制代碼。

3.2 SZ1510的二進(jìn)制代碼裝載

由于復(fù)位后內(nèi)部寄存器的內(nèi)容是未知的,因此,主機(jī)必須進(jìn)行程序代碼的裝載,以初始化視頻編碼核的可編程RAM。SZ1510內(nèi)部的程序空間是以塊(Blank)為單位進(jìn)行劃分的,每塊的大小是256字節(jié)。用于視頻編碼核的二進(jìn)制代碼的裝載空間為0x000~0x004和0x00c六個塊,共1.5k字節(jié)代碼。具體裝載時,先由主機(jī)向0x2E寄存器寫0x01,以表示外部的SDRAM是1M×16bits;接著由主機(jī)向0x0C寄存器寫0x03,以使能FIFOReady和End of Data中斷;然后由主機(jī)向0x11寄存器寫0x1,以設(shè)定工作模式為內(nèi)部內(nèi)存寫模式;再由主機(jī)向0x10寫0x20,以設(shè)定SZ1510輸出數(shù)據(jù)的FIFO大小為256字節(jié);最后對每塊程序空間進(jìn)行二進(jìn)制代碼裝載,其具體過程如下:

(1)主機(jī)寫0x3F寄存器,選擇下載程序空間;

(2)主機(jī)向0x08寄存器寫0x04,發(fā)送開始命令;

(3)主機(jī)等待Ready中斷;

(4)主機(jī)通過讀0x0e寄存器,清除Ready中斷;

(5)主機(jī)向Data_in寄存器0x01寫256個字節(jié);

(6)主機(jī)等待EOD(End 0f Data)中斷,

(7)主機(jī)通過讀0x0e寄存器,清除EOD中斷;

(8)主機(jī)查程序空間的代碼是否裝載完畢,如沒有則繼續(xù)裝載。

4 結(jié)束語

本系統(tǒng)可實(shí)時長時間記錄攝像頭傳輸?shù)钠囃獠考败噧?nèi)各儀表顯示的視頻信號,所記錄的壓縮數(shù)據(jù)流符合MPEG-1圖像壓縮標(biāo)準(zhǔn)。本設(shè)計中采用的壓縮視頻流速率為1.5 Mbps。對于一個3GB的電子盤,本系統(tǒng)可連續(xù)記錄超過4.5個小時的汽車視頻數(shù)據(jù)。由此可見,本系統(tǒng)體積小、功耗低,便于移動環(huán)境下對視頻數(shù)據(jù)的實(shí)時長時間壓縮數(shù)據(jù)記錄。

電子發(fā)燒友App

電子發(fā)燒友App

評論