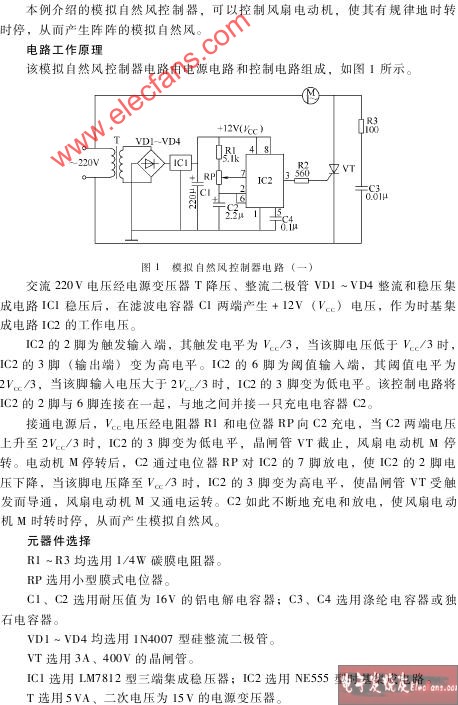

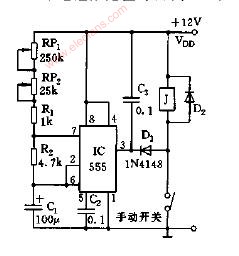

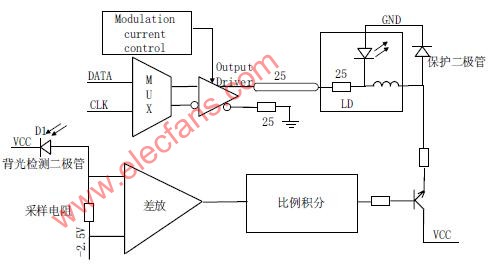

??? 參與疊加的信號有兩路:現(xiàn)場視頻信號、疊加圖形信號。由于只要求完成對攝象頭獲取的圖像的疊加,并在監(jiān)視器上重顯圖像,疊加信號可以為黑電平和白電平。而視覺效果上黑電平更明顯,所以我們選擇疊加黑電平。這個“二選一”開關(guān)可用美國MAXIM公司生產(chǎn)的MAX442來實(shí)現(xiàn)。MAX442芯片是內(nèi)含放大器的視頻兩路開關(guān),它具有140MHz的單位增益帶寬,250V/μs的轉(zhuǎn)換速率;相位誤差小于0.09°,增益誤差小于0.07%;通道切換速率為36ns,可以直接驅(qū)動50Ω或75Ω的同軸電纜。雖然它價(jià)格相對較貴,但考慮到選用它之后,系統(tǒng)的性能可以得到較大幅度的改善,而且本項(xiàng)目的總體成本仍然很低,即性能價(jià)格比合理,所以選擇這種芯片。

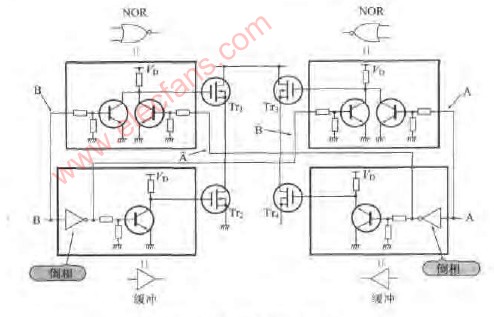

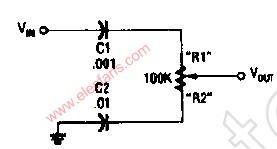

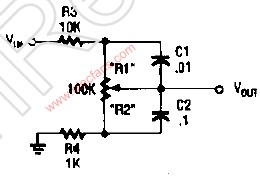

??? MAX442的引腳圖與連接電路如圖6所示,圖中的電容容值單位為μF,電阻單位為Ω。INO,IN1為兩路視頻信號的輸入端,分別外接現(xiàn)場視頻信號和黑電平;地址線AO控制“二選一”開關(guān),選擇輸出哪個通道的信號。AO在屏幕編輯緩沖區(qū)中僅占一位空間,所以疊加控制字可以按位讀寫修改,這大大減少了所需的屏幕編輯緩沖區(qū)RAM的存儲空間。在RAM中數(shù)據(jù)是按照字節(jié)存取的,因此在輸出時,需要把從RAM中讀出的數(shù)據(jù)進(jìn)行并串轉(zhuǎn)換,送到MAX442的AO端。這種“八選一”的數(shù)字邏輯電路用可編程芯片GAL可以很方便地實(shí)現(xiàn),成本也不高,因此我們選擇用GAL實(shí)現(xiàn),邏輯表達(dá)式從略。

屏幕編輯緩沖區(qū)的控制設(shè)計(jì)

??? 屏幕編輯緩沖區(qū)選擇用RAM,是因?yàn)橛脩粢蟑B加的均是規(guī)則的幾何圖形,由CPU 90C32動態(tài)計(jì)算圖形各點(diǎn)的位置算法非常簡單;用戶完全可以接受。

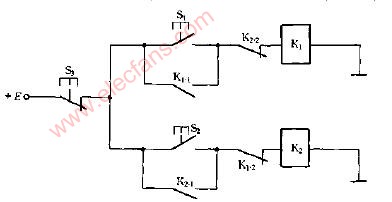

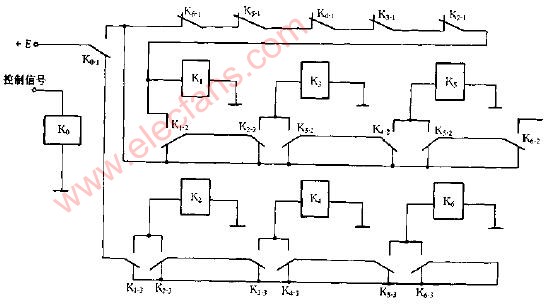

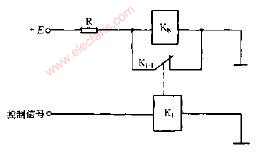

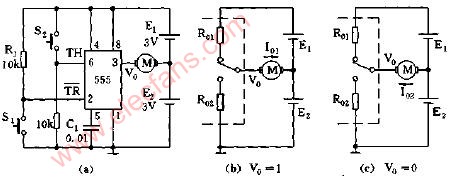

??? CPU和視頻輸出端都要對屏幕編輯緩沖區(qū)進(jìn)行訪問,其中CPU要完成對RAM的刷新,即“寫”RAM;輸出端僅需讀RAM。也就是說,對RAM的訪問可以定為“寫時禁止讀”,“讀時禁止寫”。讓它們共用數(shù)據(jù)總線DB和地址總線AB,而通過控制CPU和行場計(jì)數(shù)器的地址鎖存器的使能端E,來分時使用。可見,這兩組地址鎖存緩沖器的使能端E是互斥的,可以僅用90C32的一根PI端口I/O線來作一個“單刀雙擲開關(guān)”,由CPU通過控制這根I/O線來實(shí)現(xiàn)總線的分時使用。所以在電路設(shè)計(jì)中,RAM的片選端CS直接接地,寫使能端WR與CPU的WR相連,而讀使能端OE與行/場計(jì)數(shù)器的地址鎖存器的使能端E相連。當(dāng)CPU要對屏幕編輯緩沖區(qū)寫時,選通它的地址鎖存器的使能端E,同時行場計(jì)數(shù)器的地址鎖存器被禁止,RAM的讀使能端也被禁止,即RAM處于“只寫”狀態(tài)。反之,當(dāng)CPU不需要對RAM刷新時,選通行/場計(jì)數(shù)器的地址鎖存器的使能端E,同時RAM的讀使能也被選通,RAM處于“讀”狀態(tài),并且禁止寫操作。用這種“存儲器雙總線技術(shù)”,避免了對屏幕編輯緩沖區(qū)的沖突訪問,從而保證數(shù)據(jù)的完整性,得到穩(wěn)定、正確的疊加視頻圖像。

??? CPU 90C32的典型擴(kuò)展電路包括程序存儲區(qū)的擴(kuò)展、數(shù)據(jù)存儲區(qū)的擴(kuò)展、時鐘電路和晶振電路的擴(kuò)展。考慮到項(xiàng)目需求并保留一定的擴(kuò)充余地,存儲器ROM選用27256芯片,RAM選用61256芯片。其中除RAM(屏幕編輯緩沖區(qū))為臨界區(qū),需要特殊設(shè)計(jì)以外,其它電路與通用的單片機(jī)擴(kuò)展電路完全相同,在此不另做介紹。

??? 2.4 按鍵譯碼電路

??? 本項(xiàng)目中,用戶在人機(jī)交互選擇疊加光標(biāo)的形狀與大小時,僅需要四個按鍵,因此不必使用功能強(qiáng)大的8279芯片,直接擴(kuò)展90C32即可。四個按鍵經(jīng)過譯碼,送到90C32的P1端口,這個譯碼邏輯非常簡單,同樣用GAL實(shí)現(xiàn),邏輯表達(dá)式從略。在實(shí)際使用中,用戶選擇一次光標(biāo)的大小與形狀之后,總會穩(wěn)定一段時間去進(jìn)行其主要工作,所以操作按鍵的時間對于整個系統(tǒng)的工作時間而言是很短的。CPU對按鍵的響應(yīng)采用中斷方式,這可以比輪詢方式大大減少對CPU處理器資源的占用。在按鍵電路中,一共占用P1端口2根I/O線,AO、A1是譯碼后的按鍵地址(或代碼);另有INT是檢測是否有按鍵被按下的中斷信號線,它與90C32的外接中斷輸入端 相連接。通常INT為高電平,若有按鍵被按下,INT為低電平,CPU可響應(yīng)中斷。

相連接。通常INT為高電平,若有按鍵被按下,INT為低電平,CPU可響應(yīng)中斷。

??? 按鍵電路的設(shè)計(jì),也選擇簡單、典型而可靠的通用電路實(shí)現(xiàn)。目前,按鍵是利用機(jī)械觸點(diǎn)的合與斷來作用的,當(dāng)電信號通過按鍵時,在閉合及斷開的瞬間均有抖動過程,會出現(xiàn)一系列的負(fù)脈沖,持續(xù)時間一般為5~10ms。按鍵的穩(wěn)定閉合期,由操作人員的按鍵動作所決定,一般為十分之幾秒至幾秒時間。為了保證CPU對按鍵的一次閉合,僅做一次鍵輸入處理,必須去除抖動影響。通常去抖影響的措施有硬、軟件兩種,本項(xiàng)目用兩重 去抖來提高可靠性:硬件設(shè)計(jì)中,為每個按鍵在輸入端加一個一端接地的電容,濾去毛刺脈沖;軟件設(shè)計(jì)中,有按鍵去抖過程,具體思想在軟件設(shè)計(jì)中詳細(xì)講述。

電子發(fā)燒友App

電子發(fā)燒友App

評論