在當今的多媒體系統芯片中整合進經過硅驗證并針對特定音頻功能優化過的音頻IP,有利于降低功耗、減少體積和縮減成本。但隨著下一代設計走向28nm工藝技術,也隨之會出現新的挑戰。音頻編解碼器中的音頻設計包括了很多模擬電路,它不會隨著工藝技術的發展而與時俱“小”,因此并不遵循傳統的摩爾定律。

28nm工藝技術增加了晶圓成本,系統架構師和SoC設計師必須要考慮這對將音頻編解碼器整合進SoC的經濟性產生了何種影響。Synopsys公司測試了幾款目前在市場上出售的移動多媒體設備,發現目前多數智能手機和平板電腦可以支持用28nm工藝開發的音頻編解碼器。

本文介紹了測試結果還討論了將音頻功能整合進28nm移動多媒體SoC所面臨的商業和技術挑戰,同時闡述了如何克服這些挑戰的見解。本文還解釋了一些關鍵的設計考慮,包括縮放限制、電源電壓的要求和系統劃分選擇等。

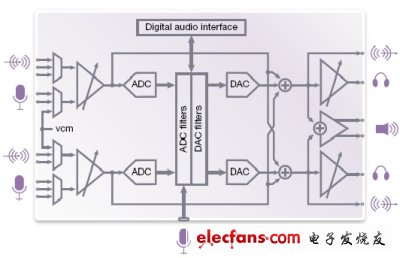

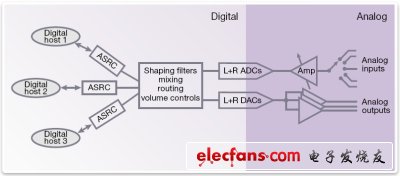

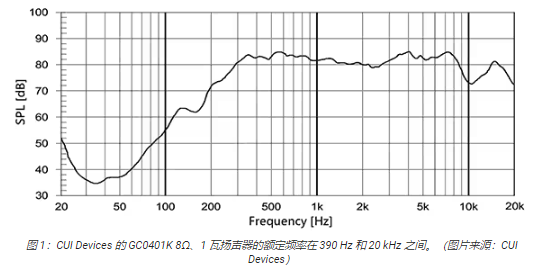

音頻編解碼器基礎:為解釋清楚和便于討論,可使用下圖1描述的一款音頻編解碼器。音頻編解??碼器包含麥克風和線輸入、信號流送和混合、放大器模塊、多通道ADC和DAC。它還包括各種輸出驅動器,包括線輸出、耳機和揚聲器驅動器以及一個包含抽取/插值濾波器的小數字信號處理模塊和一個標準的I2S數字音頻接口。

圖1:典型的音頻編解碼器方框圖。

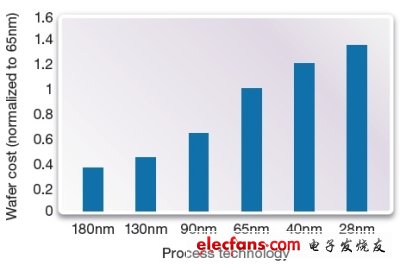

28nm工藝技術的成本考慮:在28nm工藝技術,晶圓成本比65nm技術高得多。對遵循摩爾定律的數字電路來說,更高的晶圓成本可以通過增加的門密度、可能整合進更多功能和更高性能予以補償以證明其物有所值。

模擬電路,諸如廣泛使用I/O器件的音頻編解碼器,不以與主要使用內核器件的數字電路一樣的方式隨工藝節點的縮小而減小。除非晶圓面積可減少25-30%,否則更高的晶圓成本將顯著增加音頻技術的整體硅成本。

例如,為保持相同的硅成本,用65nm技術實現的一款2.5mm2的音頻編解碼器,在用28nm工藝實現時,需要縮小至1.9mm2。下圖2顯示了到2013年,每個12英寸晶圓的成本預測(以65nm工藝為標準)。而28nm晶圓的生產成本預計將比65nm晶圓的高近40%。

圖2:2013年,不同工藝的晶圓生產成本,以65nm為標準 (資料來源:Selantek公司)。

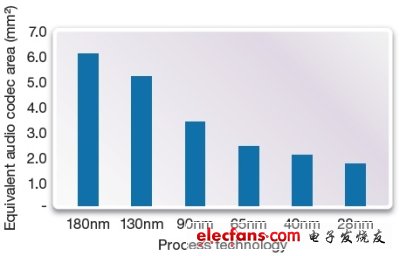

因為與65nm技術實現的相同功能音頻電路比,28nm技術的該電路性能并沒有顯著提升,所以決定是否集成音頻功能的關鍵因素之一是硅芯片的成本。下圖3顯示了與用65nm工藝實現的2.5mm2的音頻編解碼器相比,為保持相同的硅成本,用不同的工藝技術實現所要求的面積。

圖3:與用65nm工藝實現的2.5mm2的音頻編解碼器相比,為保持相同的硅成本,不同的工藝技術實現所要求的面積。

本文以下各節將討論在28nm工藝幾何尺寸,整合音頻編解碼器的關鍵技術挑戰。每個挑戰都可以通過改進電路或系統來解決,以為SoC提供最優化的功耗和成本。

音頻編解碼器的尺寸縮小限制

有三個主要的電路模塊制約著音頻編解碼器隨工藝的發展而縮小:

有源放大器和梯形電阻:有源放大器和梯形電阻用于混合不同音頻源的眾多音量控制和開關應用中。器件匹配特性制約著有源放大器的性能。減少單個器件的體積對器件匹配性能產生負面影響并顯著降低了有源放大器的性能。基于該原因,與40nm或65nm工藝的放大器相比,采用28nm工藝節點實現相同性能的有源放大器的面積并不會減少很多。為避免任何可察覺的雜音(如拉鏈噪音),音量增益步進必須低于1dB。這就需要可變抽頭電阻具有大量的抽頭,從而增加了總面積。

數據轉換器:大多數的音頻編解碼器采用Σ-Δ(sigma-delta)ADC和DAC電路實現。開關電容電路的噪音水平與電容值成反比。因此,對于一個給定的音頻性能要求來說,就對應一個所需的最小電容值,所以,電容面積不會隨工藝節點的縮小而減小。使問題進一步復雜的是,隨著電源電壓從2.5V(或3.3V)降低到28nm工藝的1.8V,為保持相同的動態范圍,必須降低噪聲水平。所以,電容的面積和容值必須加大。

輸出驅動器:必須低失真地提供大輸出電流。為了支持驅動耳機和揚聲器所需的大輸出電流,輸出器件必須很大,它也不會隨工藝技術的縮小而變小。數據轉換器模塊與此一樣,如將在下面更詳細討論的,當工作電壓從2.5V降至1.8V時,會對輸出驅動電路的面積和性能有影響。

以下兩節將探討在28nm工藝、采用1.8V電壓實現輸出驅動器時的權衡與影響。

工作電壓對輸出驅動器性能的制約

在65nm和40nm工藝,許多集成的音頻編解碼器的模擬電路使用2.5V的I/O晶體管且實際上將2.5V器件過驅至3.3V以提高音頻性能。然而,在28nm工藝,大多數SoC設計將轉而采用1.8V的I/O晶體管。目前,還沒能普遍支持將1.8V晶體管過驅至2.5V或3.3V。最終結果是電源電壓和實現線和耳機驅動器的晶體管工作電壓被限制在1.8V。

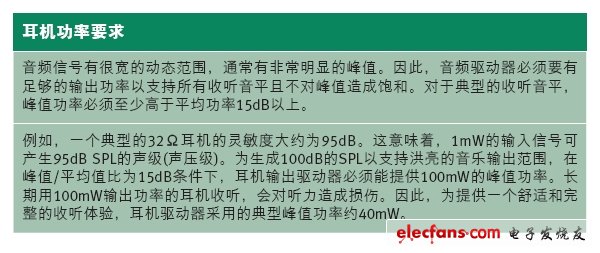

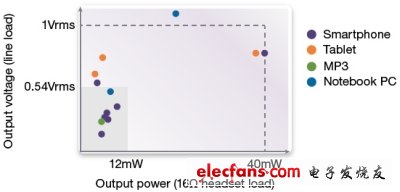

因電源電壓被限制在1.8V,所以對音頻輸出性能有根本制約。對線輸出驅動器來說,與3.3V工作電壓時1.0Vrms的可用輸出電壓擺幅比,1.8V時擺幅被限制在僅有0.54Vrms。對32歐姆的耳機來說,耳機驅動器的輸出功率被限制在只有12mW,而以前的65 nm和40nm工藝,耳機驅動器可從更高的工作電壓提供40mW功率(詳見表1“耳機功率要求”)。

表1: 耳機功率要求

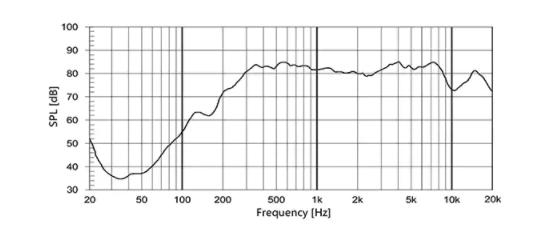

Synopsys測試了13款最新型號的移動多媒體設備,包括智能手機、平板電腦、MP3播放器和筆記本電腦,以評估目前市場上出售的音頻設備的實際性能。在這13款產品中,55%在1.8V工作電壓時,具有良好性能,就線輸出電壓RMS擺幅來說,其中3款略高于比對指標。圖4所示,一款0.54Vrms和12mW耳機驅動器的線驅動器的輸出功能表現良好或優于目前市場出售的許多設備。

圖4:一款市售的移動多媒體設備、平板電腦和智能手機樣品用的耳機驅動器的輸出功率 。

但其他的樣品測試使用了一款專用音頻集成電路(IC),以根據更好的聆聽體驗所需的40mW功率提供更高輸出功率。無論是智能手機還是平板電腦,都有公開發表的拆解報告,其中指認了獨立、專用音頻編解碼器IC。在這些情況下,使用外部音頻IC消除了28nm工藝對電源電壓的限制,但代價是:一個額外組件將需要更多系統功耗、更大面積和更高費用。

此外,也有消費類電子產品絕對要求更高的輸出驅動水平(或出于系統要求或基于消費者可覺察到性能差異的市場差異化策略),這使得有必要支持典型的40mW功率要求。在這種情況下,接入3.3V電源有兩種主要途徑:

第一個選擇是接入用于USB接口的3.3V電源。絕大多數的移動多媒體SoC會有至少一個USB接口(通常是幾個),因此有一個3.3V電源。由于該電源用于高速USB接口,因此,可能存在一個在不影響USB性能的前提下,可提供的最大負載電流限制。

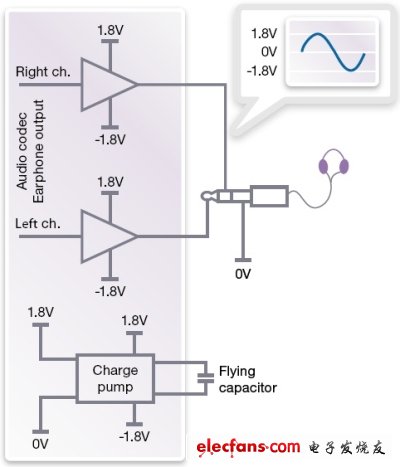

第二個選擇是采用現有的1.8V電源、借助電荷泵來產生3.3V正電源及一個1.8V負電源(圖5)。由于線輸出和耳機驅動器需要相對較低的電流,電荷泵所需的開關可以做得很小。負電源的一個額外好處是,輸出驅動器是中點接地的,從而生成了一個真正的接地(True-Ground)配置,它允許音頻編解碼器的輸出直接連接到其他器件,而不需要大塊頭的直流阻隔電容。

圖5:真正接地(True-Ground)的配置提供了一個以地電位為中心的輸出信號,它不需要隔直電容。

在這兩個選擇中,1.8V器件都需要進行正確的級聯以承受3.3V電壓。

為揚聲器驅動器找到合適的系統位置

對在28nm工藝整合進音頻編解碼器提出特殊挑戰的輸出驅動器是揚聲器驅動器。通常情況下,采用3.3V電源供電的揚聲器驅動器可提供高達500mW功率。為了獲得上好的音頻性能,揚聲器的驅動功率不應低于250mW。然而,因只有1.8V可用來驅動揚聲器驅動器的邏輯門,所以必須顯著增加輸出器件的體積以支持大電流需求,從而導致往往不可接受的硅片面積成本的增加。

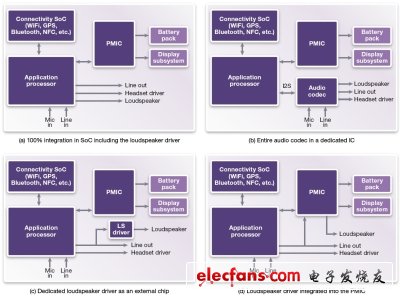

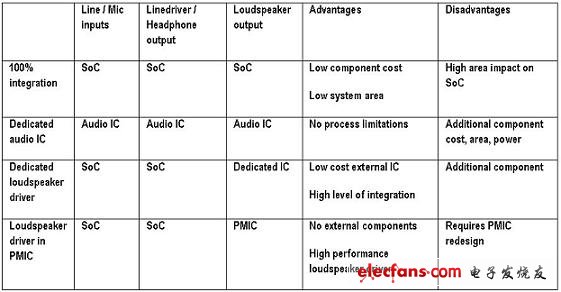

結果是,在28nm SoC內集成進揚聲器驅動器在技術上并不總是可行或實際的,這使得設計師有必要考慮系統級選項。圖6顯示了在移動多媒體系統內實現揚聲器驅動器的四種常見選擇。第一種,是將驅動器完全集成到SoC內(圖6a)。第二種,是將整個音頻編解碼器功能由一個專用音頻IC來實現,并使用I2S數字接口連接專用音頻IC和SoC(圖6b)。

圖6: 移動多媒體系統內的揚聲器驅動器實施選項。

第三種,是將除揚聲器驅動器外的所有音頻功能都集成到SoC內,并使用一款低成本、專用的揚聲器驅動器(圖6c)。第四種選擇,是將揚聲器驅動器整合進電源管理IC(PMIC)(圖6d)。因為PMIC業已支持高電壓和大電流,它成為高功率電路合乎邏輯的一個所在。此外,表2列出了每個選擇的優缺點。

表2:在移動多媒體系統內實現揚聲器驅動器的優缺點。

總之,基于揚聲器驅動器的大功率和大電流要求,它是在1.8V電壓下、以一種有面積效率的方式最難整合的輸出驅動器。為了支持揚聲器驅動器,SoC設計師必須決定是否將該功能集成到系統內的另一個模塊(如電源管理IC),或采用外部揚聲器驅動器對其進行支持。

將模擬功能轉移到數字域

在智能手機或平板電腦中,在音頻編解碼器上可能存在三個數字宿主。一個是基帶處理器,它處理語音信號并送至蜂窩射頻用來發送和接收。第二個是應用處理器,它處理智能手機存儲器上的媒體文件。第三個是藍牙射頻,它無線連接立體聲耳機。

每個音頻信號都工作在不同的時鐘域。第一個,工作在通常是13MHz的射頻時鐘。第二個,可能工作在480MHz的USB時鐘。第三個,可能工作在16MHz,即藍牙芯片的典型工作頻率。這樣一個系統內的音頻編解碼器不僅橋接了數字域和模擬域,它同時還橋接了數字生態系統中的不同時鐘域。

典型的音頻編解碼器將若干模擬信號源連接在一起并輸出到一個單一的數字宿主(digital host)。然而,在當今有眾多數字宿主的系統中,每個數字宿主都有其自己的時鐘域且往往互相并不同步。因此,將大多信號控制(音量、混合和交換)移到數字域,使ADC和DAC盡可能地接近模擬終端就很有好處(圖7)。

圖7:借助多個數字音頻宿主的基于數字化的音頻處理。

借助將更多的信號處理從模擬域轉到數字域,音頻編解碼器可以增加遵循摩爾定律的數字電路的百分比并減少不那么隨工藝的縮小而減小的電路比例。這將導致一種新的以數字為中心的架構,其中,所有的信號處理在數字模塊實施;而其外圍是模擬電路,不僅包含數據轉換器,還包含異步采樣率轉換器(ASRC)以匹配輸入時鐘域。

本文小結

隨著移動多媒體SoC縮小到28nm工藝技術,集成音頻編解碼器功能的挑戰將變得更加棘手。系統架構師和SoC設計師必須考慮到如下五個重點事項:

1. 先進節點所增加的硅成本。與65nm工藝相比,先進工藝節點增加的晶圓成本要求將音頻編解碼器的面積減少25%;

2. 音頻編解碼器隨工藝縮小而減小的限制。對28nm技術來說,音頻編解??碼器設計中對I/O器件的使用限制了在保持相同性能的前提下,減少芯片面積的能力;

3. 電源電壓制約了輸出驅動器的性能。以1.8V電壓驅動音頻輸出信號,會限制輸出驅動的性能;

4. 為揚聲器驅動器在系統內找到合適的位置。揚聲器驅動器是將音頻編解碼器整合進28nm技術所遭遇的最具挑戰性的工作。為揚聲器驅動器功能找到合適的系統劃分對優化整體性能至關重要;

5. 將模擬功能轉移到數字域。可對音頻編解碼器架構進行改造,通過用數字域實現更多功能,以充分分享數字域隨28nm工藝技術的縮小而減小帶來的好處。

?

總之,將音頻編解碼器整合進新一代的SoC的技術還值得我們去研究和挑戰!

?

電子發燒友App

電子發燒友App

評論