,這使其在 AI 應用中面臨著一些挑戰。

Larzul 表示,想要解決這些問題的解決方案便是實現現場可編程門陣列 (FPGA),這也是他們公司的研究領域。FPGA 是一種處理器,可以在制造后定制

2024-03-21 15:19:45

較高端的場合。

單片機是一個微控制器,通過加載模塊軟件來實現某種功能,單片機是成型的芯片;

FPGA是用來設計芯片的芯片。

速度上的區別

FPGA由于是硬件電路,運行速度直接取決于晶振速度,系統穩定

2024-03-16 07:14:47

TINYFPGA AX1

2024-03-14 22:18:36

TINYFPGA AX2

2024-03-14 22:18:36

TINYFPGA BX

2024-03-14 22:18:36

作為AnaPico經典的寬帶頻率綜合器模塊,APSYN420具備以下特征:? 低相位噪聲:-108dBc/Hz@10GHz,100kHz? 0.001Hz頻率分辨率? +23dBm的典型且穩定

2024-03-13 17:03:18

。

三、智能照明控制系統在城市綜合管廊中的應用

1.智能照明控制系統

(1)智能照明控制系統的組成

智能照明控制系統主要由智能照明主機、通信網絡、繼電器開關模塊、調光模塊、控制面板、網關、照度傳感器

2024-02-27 14:52:07

我們的體驗之旅了!

做個簡單的8段數碼管測試吧,打開工程,輸入代碼,經過綜合-實現-配置相關IO后生成bit,連接好下載器如下圖

雙擊open target打開下載界面,點擊自動識別按鈕,自動識別

2024-02-23 20:51:11

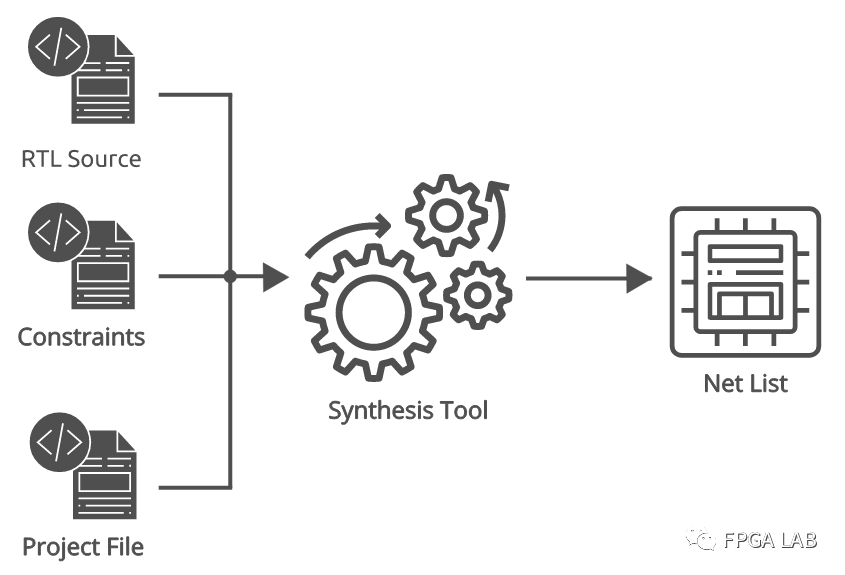

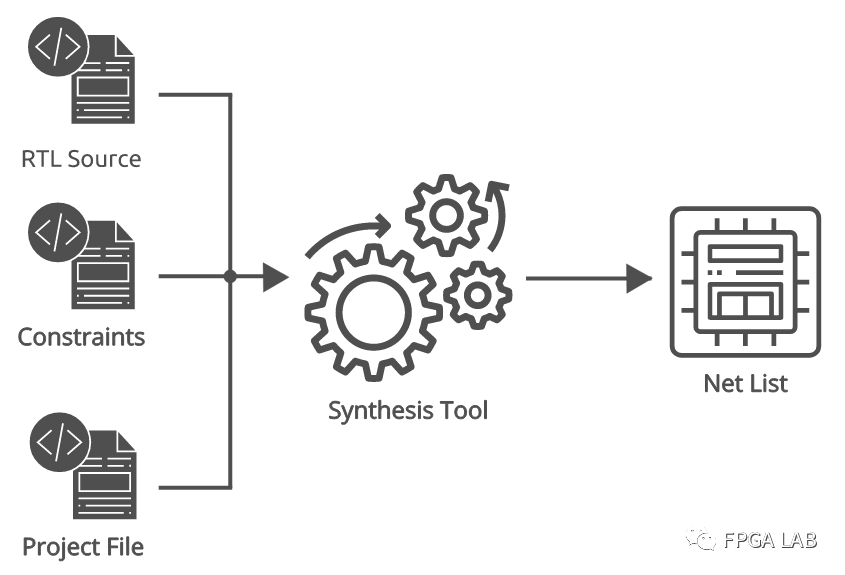

了,這就大大的降低了工作量。這就是可綜合的概念,也就是說在對這一抽象層次上硬件單元進行描述可以被EDA工具理解并轉化為底層的門級電路或其他結構的電路。在FPGA設計中,就是在將這以抽象層級的意見描述成

2024-02-22 11:00:27

1.基礎問題

FPGA的基礎就是數字電路和HDL語言,想學好FPGA的人,建議床頭都有一本數字電路的書,不管是哪個版本的,這個是基礎,多了解也有助于形成硬件設計的思想。在語言方面,建議初學者學習

2024-02-22 10:57:13

競爭冒險:在組合電路中,當邏輯門有兩個互補輸入信號同時向相反狀態變化時,輸出端可能產生過渡干擾脈沖的現象,稱為競爭冒險。那么 FPGA 產生競爭冒險的原因是什么呢? 信號在 FPGA 器件內部通過

2024-02-21 16:26:56

計算密集型任務,如矩陣運算、圖像處理、機器學習等。與CPU相比,FPGA在這些任務上具有更高的性能和更低的延遲。 此外,FPGA在通信密集型任務中也具有顯著優勢。由于FPGA上的收發器可以直接

2024-02-21 16:10:49

有朋友提問,下面的代碼為什么在DC里可以綜合成DFF,而在FPGA上卻綜合成了latch。

2024-02-20 16:12:34 154

154

FPGA在金融領域的具體應用案例,幫助讀者了解理論與實踐的結合,以及如何在真實世界的問題中應用FPGA技術。

研究前景:指出了未來神經網絡加速器研究的潛力,為有志于在該領域深入研究的學者和工程師提供了方向

2024-01-31 21:14:06

斬波電路的開關頻率由什么決定? 斬波電路的開關頻率是指電路中開關元件(一般是晶體管或MOSFET)的開關動作頻率。這個頻率是由多個因素決定的,包括電路設計的目標、開關元件的參數、電路的工作條件

2024-01-31 16:43:18 219

219 引入到FPGA,或者將信號從FPGA傳送到外部。

互連資源 (Interconnect Resources):互連資源是一種復雜的開關網絡,它允許在FPGA中的不同邏輯塊之間建立連接。用戶可以通過編程來

2024-01-26 10:03:55

的天下。

FPGA 在人工智能系統的前端部分也是得到了廣泛的應用,例如自動駕駛,需要對行駛路線、紅綠燈、路障和行駛速度等各種交通信號進行采集,需要用到多種傳感器,對這些傳感器進行綜合驅動和融合處理

2024-01-17 17:03:05

幾周前,我們考察了Cologne Chip的 GateMate FPGA 。在本博客中,我們將探索 GateMate FPGA 工具鏈以及如何啟動并運行初始的 hello world 應用程序

2024-01-11 00:52:12

FPGA驗證是其中的重要的組成部分,如何有效的利用FPGA 的資源,管腳分配也是必須考慮的一個重要問題。一般較好的方法是在綜合過程中通過時序的一些約束讓對應的工具自動分配,但是從研發的時間段上來考慮

2024-01-10 22:40:14

描述語言HDL,或者寄存器傳輸級語言RTL,下文中我們統稱RTL。

對于初學者,這里我們先不討論高層次綜合的內容,也就是用C語言或者python編程FPGA。關于高層次綜合的內容,可以看我之前

2024-01-02 23:03:31

基本邏輯單元組成的邏輯連接網表,而并非真實的門級電路。

5.綜合后仿真

綜合后仿真檢查綜合結果是否與原設計一致。在仿真時,把綜合生成的標準延時文件反標注到綜合仿真模型中,可估計門延時帶來的影響。但這一步

2023-12-31 21:15:31

中SCK的頻率為44M。請問

1)、在Datasheet中,SCK時鐘的最大頻率卻提供了一個最小值,是什么意思?頻率到底應該大于40M還是小于40M?

2)、當前我使用的三線串口的SL信號存在一些毛刺

2023-12-18 06:42:55

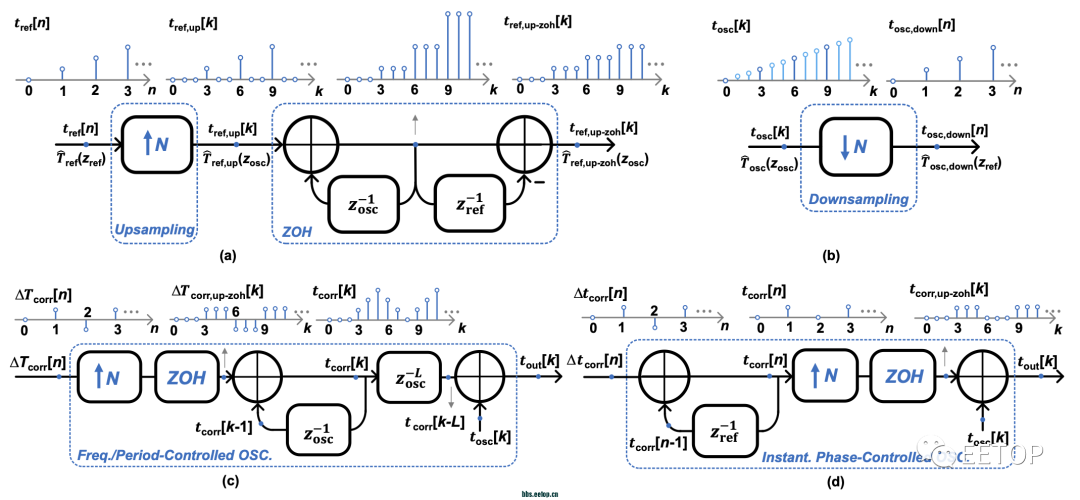

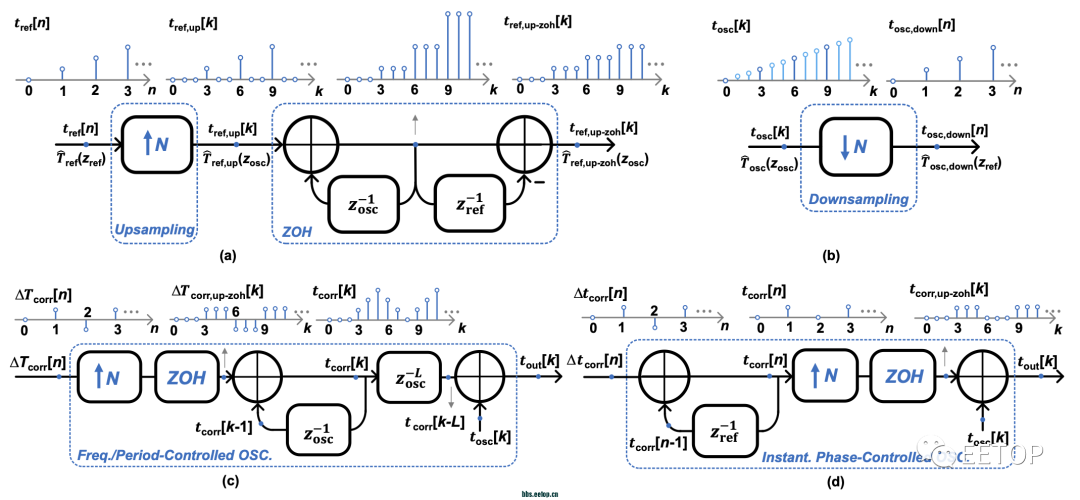

繼實現振蕩器閃爍相噪理論統一后,我們再次實現頻率綜合器的相噪理論一統。

2023-12-01 11:43:37 368

368

您好,我在fpga中采用spi通信讀ad9173寄存器時,發現ad9173沒有響應。其中spi通信速率為10M完全滿足datasheet不大于80M的要求。其中通信方式采用四線制。讀取寄存器為

2023-12-01 06:10:50

上次分享了基于FPGA的線性插值的背景和方法原理,今天分享

方法原理的驗證。

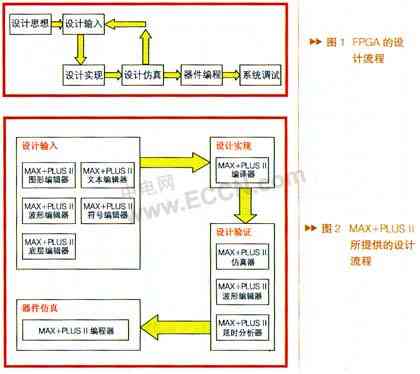

通常FPGA的開發分為電路功能設計、設計輸入、功能仿真、綜合優化、綜合后仿真、實現、布線后仿真、板級仿真以及芯片編程

2023-11-23 23:09:43

的微處理器(MPU)和微控制器(MCU)、現成的圖形處理單元(GPU)、FPGA和自定義片中系統(SOC)裝置。要決定使用哪種方法,需要根據具體的應用需求來綜合考慮。

舉例來說,在研究諸如5G基站這樣

2023-11-20 18:56:02

電子、AI、數據中心。

安路科技(上海)

核心技術:全流程TD軟件系統

主要產品:高端PHOENIX(鳳凰)、中端EAGLE(獵鷹)、低端ELF(精靈)系列FPGA。

應用方案:LED顯示屏、工業自動化

2023-11-20 16:20:37

放大電路的頻率補償的目的是什么?有哪些方法? 放大電路的頻率補償是為了改善信號在不同頻率下的放大效果,以使輸出信號更加準確、穩定和可靠。頻率補償是放大電路設計中的一個重要環節,它的目的是提高整體性

2023-11-17 14:16:12 831

831 電子發燒友網站提供《使用Vivado高層次綜合(HLS)進行FPGA設計的簡介.pdf》資料免費下載

2023-11-16 09:33:36 0

0 。

時序約束可以讓VIvado和Quartus等FPGA開發軟件,在布線時檢測綜合出來的邏輯電路是否滿足這個時序要求,并生成時序報告。

一、建立/保持時間

1、基本概念

設定時序約束的目的就是為了滿足

2023-11-15 17:41:10

模塊間利用金屬連線互相連接或連接到I/O模塊。FPGA的邏輯是通過向內部靜態存儲單元加載編程數據來實現的,存儲在存儲器單元中的值決定了邏輯單元的邏輯功能以及各模塊之間或模塊與I/O間的聯接方式,并最終

2023-11-14 15:30:30

前段時間寫了一篇關于Buck電路開關頻率的文章《Buck電源芯片的開關頻率為什么經常是400kHz或者2.2MHz?》,沒想到有1.3w+的閱讀量。說明同學們對這塊很感興趣。今天我們就再深入挖掘下,選擇不同開關頻率對實際電路有哪些影響。

2023-11-13 10:01:41 1477

1477

,緩存器等,并了解這些元件的功能、信號和接口。

四、數字信號處理

數字信號處理(DSP)在FPGA設計中是一個重要的領域,用于設計各種信號處理電路,包括音頻采集和處理,圖像和視頻處理等

2023-11-09 11:03:52

,FPGA已經從配角變成了主角。

FPGA在通信領域上有著極廣泛的應用,就拿現在很火熱的5G網絡來說,幾乎在5G基站里面的每一塊電路板都需要用到FPGA;還有在機器人學習中,FPGA在感知計算的場景下

2023-11-03 10:32:41

實現時序,寄存器模塊存儲電路狀態,RAM模塊存儲大量數據,IO與外部進行通信,一個最基礎的FPGA芯片架設完畢。

新生產的FPGA,也只是在這個基礎上加一些高速接口、專用運算模塊DSP、嵌一個CPU

2023-11-03 10:29:05

ASIC 和基于處理器的系統的最大優勢,它能夠提供硬件定時的速度和穩定性,且無需類似自定制 ASIC 設計的巨額前期費用的大規模投入。但是和所有的數字電路一樣,FPGA 電路中也存在毛刺問題。它的出現會

2023-11-02 17:22:20

fpga與dsp通訊怎樣同步時鐘頻率?dsp和fpga通信如何測試? 在FPGA與DSP通訊時,同步時鐘頻率非常重要,因為不同的設備有不同的時鐘頻率,如果兩者的時鐘頻率不同步,會導致通訊數據的錯誤

2023-10-18 15:28:13 1059

1059 逆變電路的頻率由什么決定 逆變電路的頻率是由兩個主要因素決定的,電路中所使用的元器件及其參數、以及控制元件(例如晶體管或場效應管)的開關速度。 在逆變電路中,最為重要的元器件是電感和電容,因為它們

2023-10-16 15:57:10 878

878 如何改變逆變電路的輸出頻率 逆變電路是一種能夠將直流電轉換成交流電的電路,在實際應用中廣泛使用。其輸出頻率是由電路中的元器件參數所決定的。如果要改變逆變電路的輸出頻率,可以采取以下方法: 1. 改變

2023-10-16 15:57:03 1792

1792 本專題為FPGA基礎電路內容合計,這里有算法電路的基礎電路與典型電路,還有時序邏輯電路和組合邏輯電路,如果您是剛入門的新手開發者,那么這個專題一定適合你!

2023-09-25 15:40:01

在進行FPGA的設計時,經常會需要在綜合、實現的階段添加約束,以便能夠控制綜合、實現過程,使設計滿足我們需要的運行速度、引腳位置等要求。通常的做法是設計編寫約束文件并導入到綜合實現工具,在進行

2023-09-21 07:45:57

簡單的存儲器,任何可能有五個或六個輸入的布爾組合函數可以在每個邏輯塊中實現。通用路由結構允許任意布線,因此可以以期望的方式連接邏輯元件。

由于這種通用性和靈活性,FPGA可以實現非常復雜的電路。目前

2023-09-21 06:04:41

系統的性能。脈沖信號載波頻率同步技術的關鍵是在噪聲背景中快速準確地估計載波頻率。為實現高精度鑒頻,通常要使用高階數窄帶濾波器來提高待測信號的信噪比,其延時較大,不適用于信號持續時間較短的脈沖信號

2023-09-20 08:28:04

密勒電容對放大電路頻率的影響? 密勒電容是指在放大電路中引入的補償電容,它可以幫助控制放大電路的頻響性能,提高放大電路的穩定性和可靠性。因為電容對電路的頻率響應具有重要的影響,所以在設計放大電路

2023-09-18 09:15:50 686

686 邏輯綜合是將RTL描述的電路轉換成門級描述的電路,將HDL語言描述的電路轉換為性能、面積和時序等因素約束下的門級電路網表。

2023-09-15 15:22:52 1913

1913

開關頻率對buck電路的影響?? Buck電路是一種降壓轉換電路,用于將電源電壓轉換為所需的較低電壓來驅動負載。開關頻率對Buck電路的性能、效率和穩定性都有著重要的影響。 Buck電路通常由開關

2023-09-12 15:52:23 2784

2784 低頻率超聲波線路板PCB驅動電路將超聲逆變電源的控制電路通過數字化來實現。本文創新地利用FPGA構建了全數字頻率跟蹤系統——數字鎖相環和全數字功率調節系統——數字PWM調制、數字PID調節,從而取代

2023-09-07 15:16:37 217

217

添加。

3. 綜合、實現、生成比特流文件

1) 在左側Flow Navigator中依次點擊‘Run Synthesis’、‘Run Implementation’和‘Generate

2023-08-17 19:31:54

PCB噴碼機在電路板FPCB行業的詳細應用狀況。 不論是PCB噴碼機、FPC噴碼機、電路板噴碼機,我們都曾經聽過很多,特別是電路板行業內的廠

2023-08-17 14:35:11

求助:

將hbirdv2代碼綜合后下載到FPGA板(不是MCU200T或DDR200T)上,由于板子上沒有MCU_FLASH,所以引腳綁定時qspi接口懸空,出現如下錯誤

本人猜測

2023-08-16 08:02:14

今天給大俠帶來基于 FPGA Vivado 信號發生器設計,開發板實現使用的是Digilent basys 3。話不多說,上貨。

需要源工程可以在以下資料獲取里獲取。

資料匯總|FPGA軟件安裝包

2023-08-15 19:57:56

FPGA高級時序綜合教程

2023-08-07 16:07:55 3

3 FPGA實現,按鍵控制,四個按鍵實現波形轉換(三角波,正弦波,方波),頻率可調,電壓可調。

2023-08-07 11:47:04 3

3 今天跟大家分享的內容很重要,也是調試FPGA經驗的總結。隨著FPGA對時序和性能的要求越來越高,高頻率、大位寬的設計越來越多。在調試這些FPGA樣機時,需要從寫代碼時就要小心謹慎,否則寫出來的代碼

2023-08-01 09:18:34 1041

1041

“全局時鐘和第二全局時鐘資源”是FPGA同步設計的一個重要概念。合理利用該資源可以改善設計的綜合和實現效果;如果使用不當,不但會影響設計的工作頻率和穩定性等,甚至會導致設計的綜合、實現過程出錯

2023-07-24 11:07:04 655

655

常見的FPGA核心電路可以歸納為五個部分:電源電路、時鐘電路、復位電路、配置電路和外設電路。下面將對各部分電路進行介紹。

2023-07-20 09:08:31 468

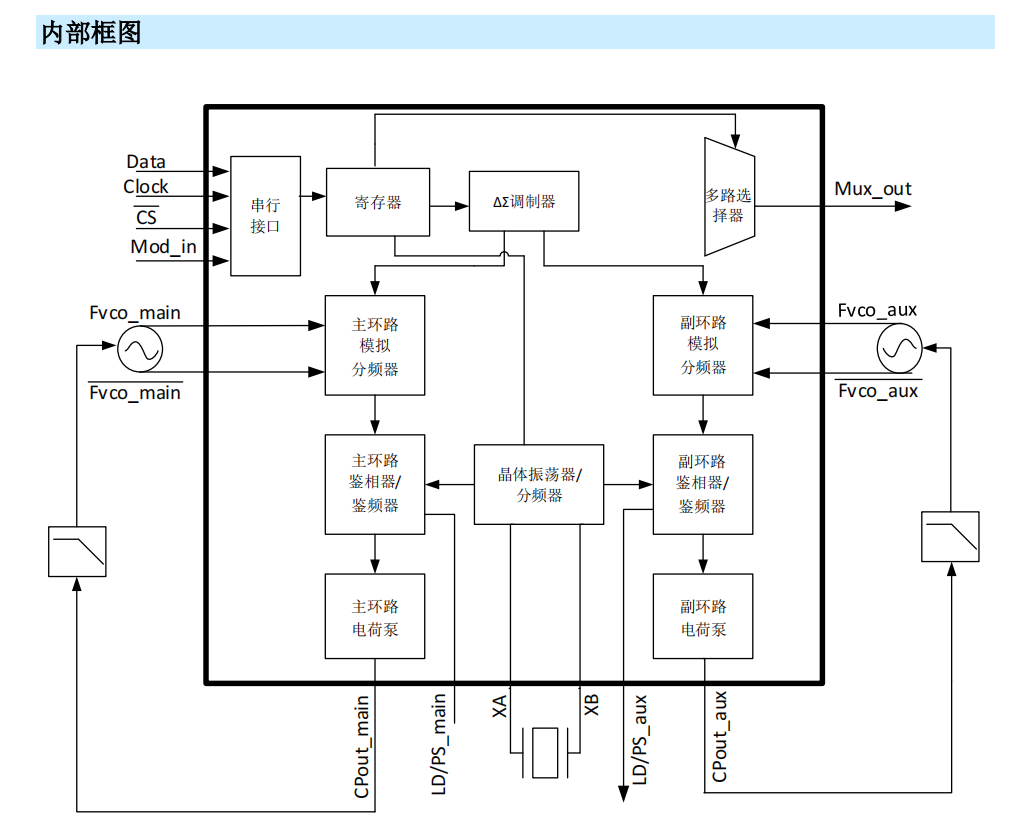

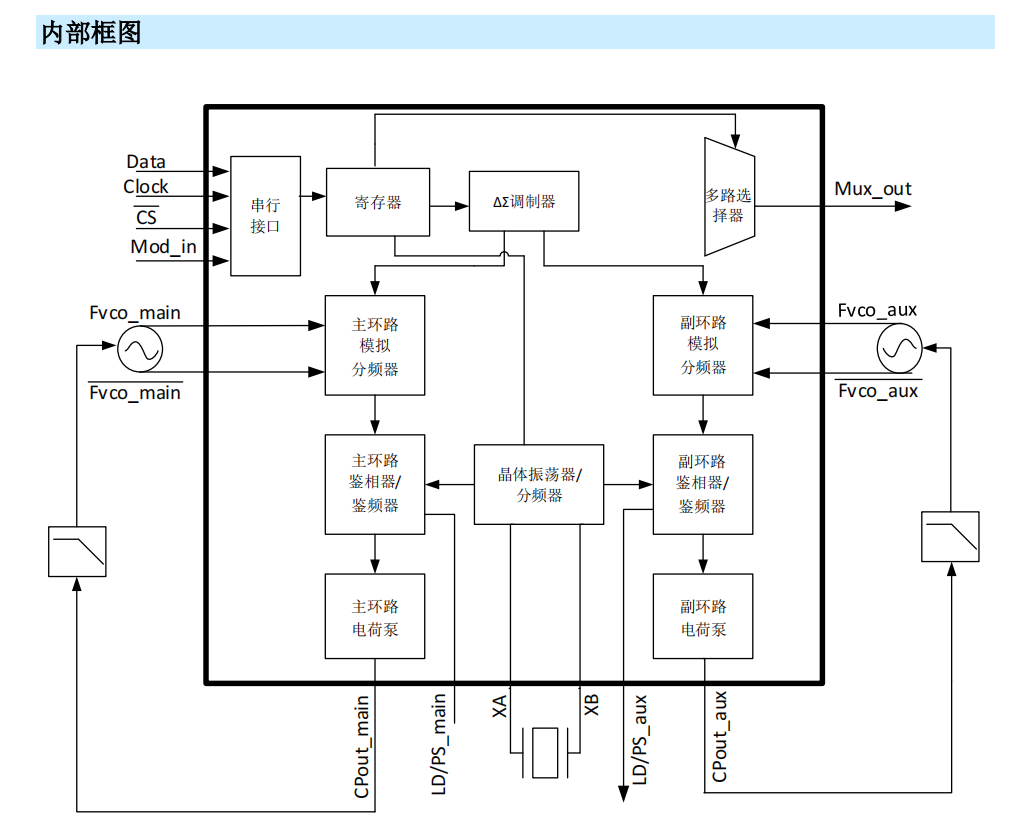

468 MS72300 是一款雙環路、小數 N 分頻頻率綜合器。包含主環路和副環路鎖相環。它提供了極高的頻率分辨率、快的輸出頻率切換速度和低相位噪聲性能。芯片須使用外部壓控振蕩器,主環路最大工作頻率 2.1GHz,適合應用于無線通信系統中。

2023-07-01 16:36:19 1009

1009

的計算機、電視、音響系統、視頻記錄設備、遠程通訊電子設備無一不采用電子系統、數字電路系統。因此,數字技術的應用越來越廣泛。尤其在通信系統和視頻系統中,數字系統尤為突出。而隨著FPGA的出世,數字系統更加

2023-06-27 20:42:56

構建FPGA的第一階段稱為綜合。此過程將功能性RTL設計轉換為門級宏的陣列。這具有創建實現RTL設計的平面分層電路圖的效果。

2023-06-21 14:26:16 508

508

的數量也在飛快地增長, 其所需要的計算資源和內存資源也在不斷增加。目前通用CPU已經無法滿足CNN的計算需 求,如今主要研究大多通過專用集成電路(ASIC),圖形處理器(GPU)或者現場可編程門 陣列

2023-06-20 19:45:12

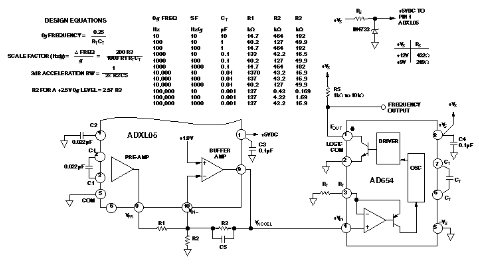

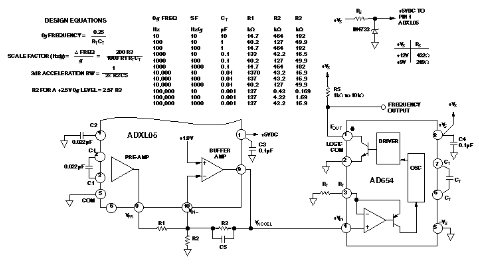

單片加速度計的輸出可以連接到電壓-頻率轉換器(VFC),該電路的輸出是可變頻率的,以簡單且低成本地產生與加速度成比例的頻率。由此產生的高電平交流信號中的信息可以通過具有衰減和非線性響應的嘈雜環境發送,但可以可靠地恢復。對于加速度到數字轉換,可以輕松編程微處理器以讀取頻率并直接計算施加的加速度。

2023-06-17 10:54:42 712

712

頻率范圍擴大。 6. 中和 并接在三極管放大器的基極與發射極之間,構成負反饋網絡,以抑制三極管極間電容造成的自激振蕩。 7. 穩頻 在振蕩電路中,起穩定振蕩頻率的作用。 8. 定時 在RC時間常數電路中

2023-06-08 14:09:21

可以使用任何可綜合的標志符。

②在描述時序電路的always 塊中的reg 型信號都會被綜合成寄存器,這是和組合邏輯電路所不同的。

③時序邏輯中推薦使用非阻塞賦值“<=”,原因將后面詳細

2023-06-02 14:20:17

、移位寄存器或RAM。在Xilinx公司的FPGA器件中,CLB由多個(一般為4個或2個)相同的Slice和附加邏輯構成,如圖1-3所示。每個CLB模塊不僅可以用于實現組合邏輯、時序邏輯,還可以配置為分布式

2023-05-30 20:53:24

芯片實物圖

FPGA 發展歷程在 PLD 未發明之前,工程師使用包含若干個邏輯門的離散邏輯芯片進行電路系統的搭建,復雜的邏輯功能實現起來較為困難。

為了解決這一問題,20 世紀 70 年代

2023-05-30 20:40:25

以及設計芯片,而是針對較多領域產品都能借助特定芯片模型予以優化設計。從芯片器件的角度講,FPGA 本身構成 了半定制電路中的典型集成電路,其中含有數字管理模塊、內嵌式單元、輸出單元以及輸入單元等

2023-05-30 20:38:46

1.基礎問題

FPGA的基礎就是數字電路和HDL語言,想學好FPGA的人,建議床頭都有一本數字電路的書,不管是哪個版本的,這個是基礎,多了解也有助于形成硬件設計的思想。 在語言方面,建議初學者

2023-05-30 20:37:49

。

8、在設計中對所有模塊的輸入時鐘、輸入信號、輸出信號都用D觸發器或寄存器進行同步處理,即輸出信號直接來自觸發器或寄存器的輸出端。這樣可以消除尖峰和毛刺信號。

注:仿真結果和實際綜合的電路

2023-05-30 17:15:28

有人說FPGA不需要上電復位電路,因為內部自帶上電復位信號。也有人說FPGA最好加一個上電復位電路,保證程序能夠正常地執行。不管是什么樣的結果,這里先把一些常用的FPGA復位電路例舉出來,以作公示。

2023-05-25 15:50:45 2104

2104

和時序邏輯電路分成獨立的always描述。

十三、循環語句規則

1、在設計中不推薦使用循環語句;

2、在非常有必要使用的循環語句時,可以使用for語句。

十四、約束規則

1、對所有時鐘頻率

2023-05-23 18:15:44

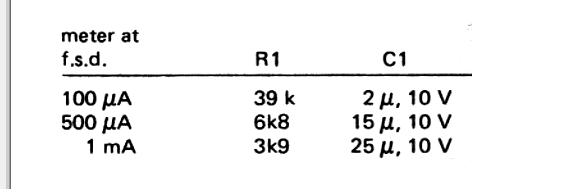

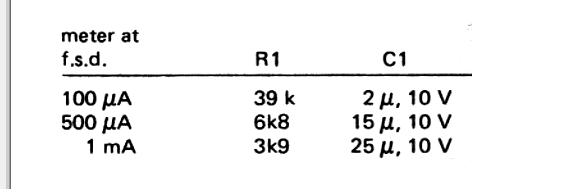

以下簡單的模擬頻率計電路可用于測量頻率,可以是正弦波或方波。要測量的輸入頻率必須至少為25 mV RMS,以實現最佳檢測和測量。

2023-05-18 18:17:49 1544

1544

節拍頻率指示器用于指示我們感興趣的信號頻率何時超過參考頻率。這是一個這樣的指示電路,它使用LED來指示我們的信號何時超過參考頻率。這些指示電路可用于功能和美學目的。該電路接受輸入信號和參考信號中的任何類型的波形。

2023-05-13 14:35:22 543

543

目的編碼,是指: 什么樣的代碼或代碼塊,對應綜合結果的什么樣的電路(What Statements is What Circuit) 需要什么電路,應該使用什么樣的代碼描述(What Circuit

2023-05-11 20:17:26 321

321 隨著FPGA對時序和性能的要求越來越高,高頻率、大位寬的設計越來越多。在調試這些FPGA樣機時,需要從寫代碼時就要小心謹慎,否則寫出來的代碼可能無法滿足時序要求。

2023-05-06 09:33:27 773

773

的分析一下。

背景

1、亞穩態發生原因

在FPGA系統中,如果數據傳輸中不滿足觸發器的Tsu和Th不滿足,或者復位過程中復位信號的釋放相對于有效時鐘沿的恢復時間(recovery time)不滿足

2023-04-27 17:31:36

在進行FPGA的設計時,經常會需要在綜合、實現的階段添加約束,以便能夠控制綜合、實現過程,使設計滿足我們需要的運行速度、引腳位置等要求。通常的做法是設計編寫約束文件并導入到綜合實現工具,在進行

2023-04-27 10:08:22 768

768 。這種產品的升級換代很大程度上都是由于半導體工藝的升級換代引起的。

隨著半導體工藝的升級換代,FPGA芯片也在升級換代的過程中,提供了更強大的功能,更低的功耗和更好的性價比。那么在確定一個系列的FPGA

2023-04-25 20:48:35

在RLC并聯諧振電路中諧振頻率的是怎么推導出來的?

2023-04-25 14:24:51

為什么llc諧振變換器在工作頻率大于諧振頻率時刻?

2023-04-25 14:23:36

FPGA設計的電路速度指什么?? 比如設計電路速度為200MHz,是指每秒鐘可以吞吐200M個數據嗎?? 我的想法是比如FPGA的系統時鐘為50MHz,輸出是通過寄存器寄存后再輸出的,只有在每個時鐘

2023-04-23 14:58:18

在FPGA的開發中,如何對inout信號進行賦值?

2023-04-23 14:25:00

如SPI接口中,FPGA通過模擬產生時鐘和串行數據與一個外部芯片進行通信,其建立和保持時間是有時序要求的,這個時序要求可以通過外部的手冊上獲得。那么在FPGA中模擬這個接口要如何保證這個時序要求呀

2023-04-23 11:35:02

在電路中,變頻器可以通過頻率來控制馬達速度的快慢,但我不想不通,為什么通過改變頻率就可以來控制馬達的速度快慢的啊?在控制電路中,變頻器是不是可以叫做變速器? 在電路中變頻器是如何起到控制作用的?它的工作原理是什么?各位大哥大姐們,我救急啊,望大家幫幫忙....

2023-04-18 16:38:22

在一個靠通電和斷電來控制用電器工作的控制電路中,通電頻率高和占空比大是一個意思嗎?

2023-04-10 11:50:09

FPGA外接50MHZ的晶振,里面的組合邏輯電路運行時刷新頻率是多少呢?

2023-04-10 11:46:50

MODULE USB-TO-FPGA SPARTAN3

2023-04-06 11:27:13

MODULE USB-TO-FPGA SPARTAN 3A

2023-04-06 11:27:11

FPGA設計的五個主要任務:邏輯綜合、門級映射、整體功能邏輯布局、邏輯資源互連布線,最后生成FPGA的bit流

2023-04-06 09:39:45 691

691 按照伯德圖縱坐標增益的對數表示,則截止頻率處的增益為-3dB。 由于電路中包含電容,所以輸出電壓的相位落后輸入電壓。在截止頻率處輸出電壓落后輸入電壓45度。導致輸出信號相位滯后的原因是電容的充電需要

2023-04-04 16:08:53

Schematic。在RTL視圖中,綜合出來的電路圖,只是電路模型而已。在FPGA中是沒有與門的,有的只是LUT等效的二輸入與門電路。綜合分析成功后,會產生一個報告。在報告中,可以看出綜合狀態、軟件

2023-03-30 19:04:10

BOARD EVAL FOR ORCA OR4E6 FPGA

2023-03-30 11:49:36

33-38GHz 頻率綜合器

2023-03-24 14:45:28

在滯回比較器中,如何修改電路使比較器的輸出電壓可變呢?有哪些方法?

2023-03-24 09:48:40

電子發燒友App

電子發燒友App

評論