Cadence Allegro SiP and IC Packaging 16.3版推出

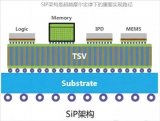

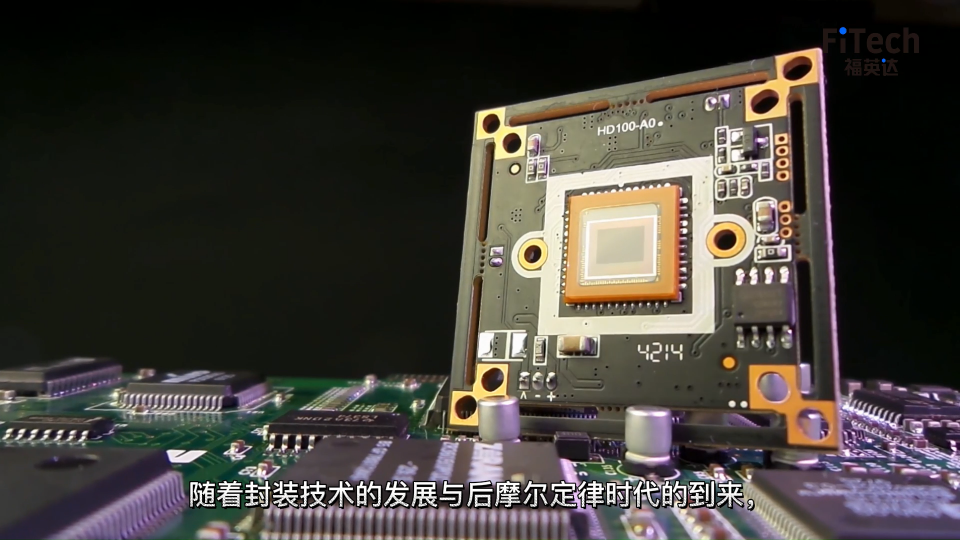

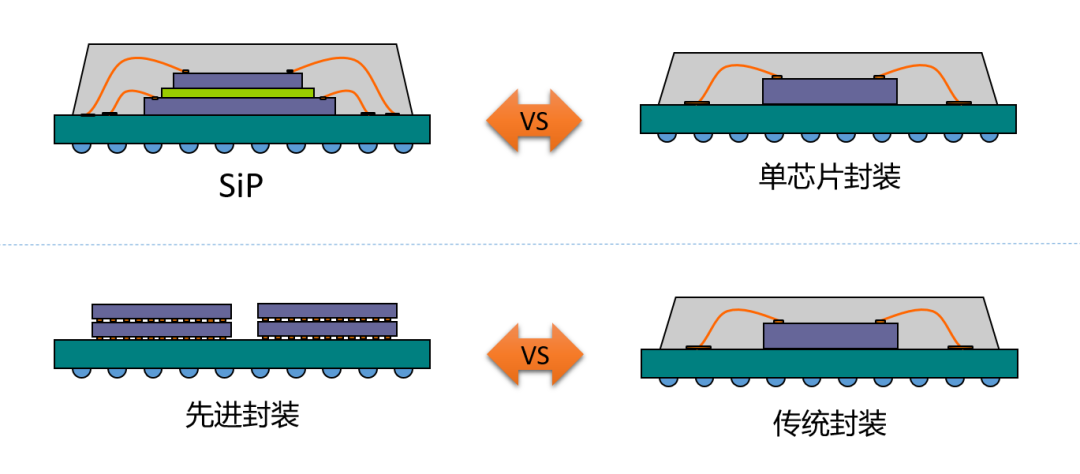

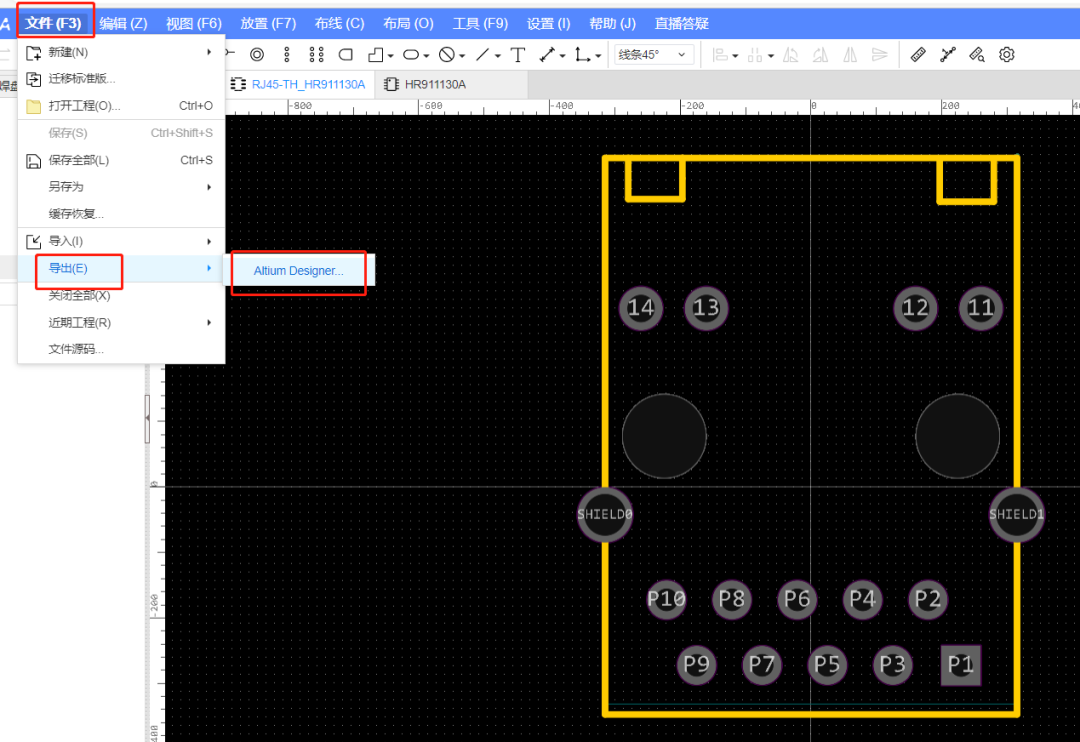

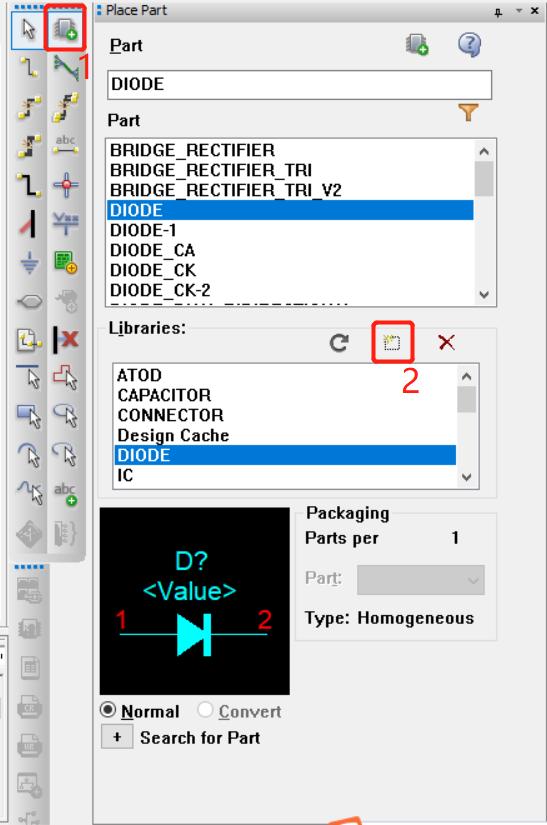

Cadence設計系統公司宣布,利用最新的系統封裝(SiP)和IC封裝軟件,封裝設計者將在芯片封裝協同設計過程中和整個半導體設計鏈中擔當更重要的角色。Cadence Allegro 16.3版提供的新產品的SiP Layout XL,它將協同設計直接融入封裝設計環境中。新的協同設計技術支持在封裝和芯片設計團隊共同對芯片和封裝設計進行優化,整個過程中封裝設計者無需另外學習新的IC設計工具。通過Allegro Package Designer (APD)提供的新型SiP Finishing技術,設計鏈協作也將得到進一步增強。

利用這一新技術帶來的協同設計方法,封裝設計者、封裝設計服務公司,裝配測試公司(OSAT)可以共同參與到多芯片 SiP的設計鏈中。Cadence協同設計技術也使設計鏈合作伙伴彼此之間能夠輕松地傳輸數據。使用了16.3版軟件的公司將受益于更短的設計周期、更高的生產率和更低的成本。

“我們非常期望采用16.3版軟件,因為我們能夠籍此提高生產率,為我們的客戶提供更好的IC封裝協同設計服務”,ASE公司的R&D產品設計經理CT Chiu表示,“我們相信新的Cadence SiP和IC封裝技術將在提高半導體設計鏈效率方面擔當重要的角色。”

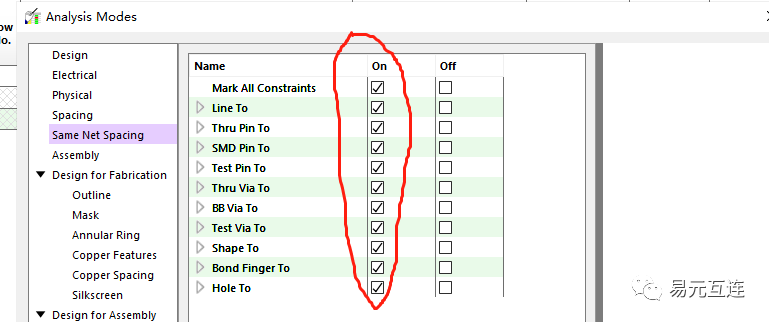

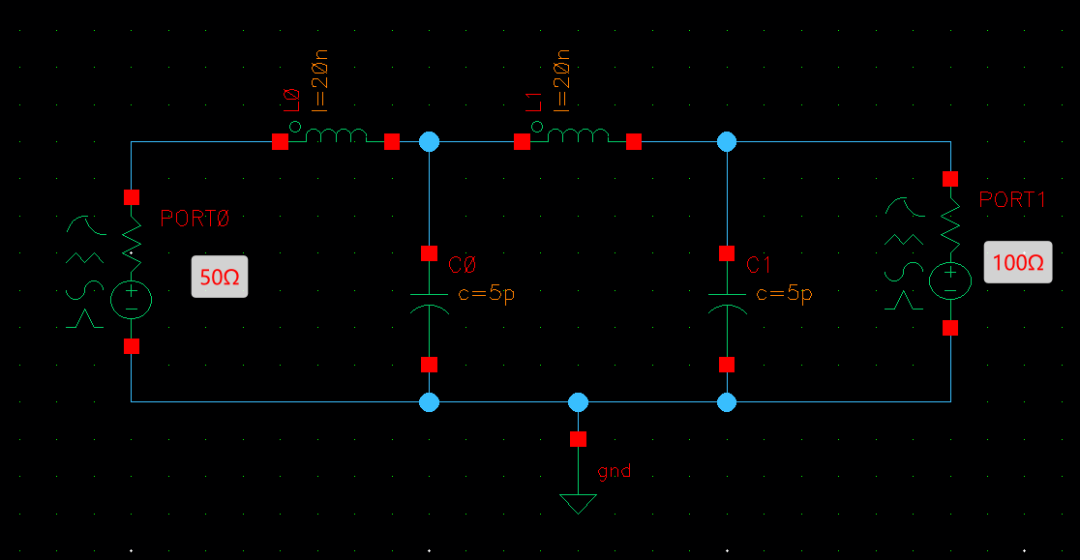

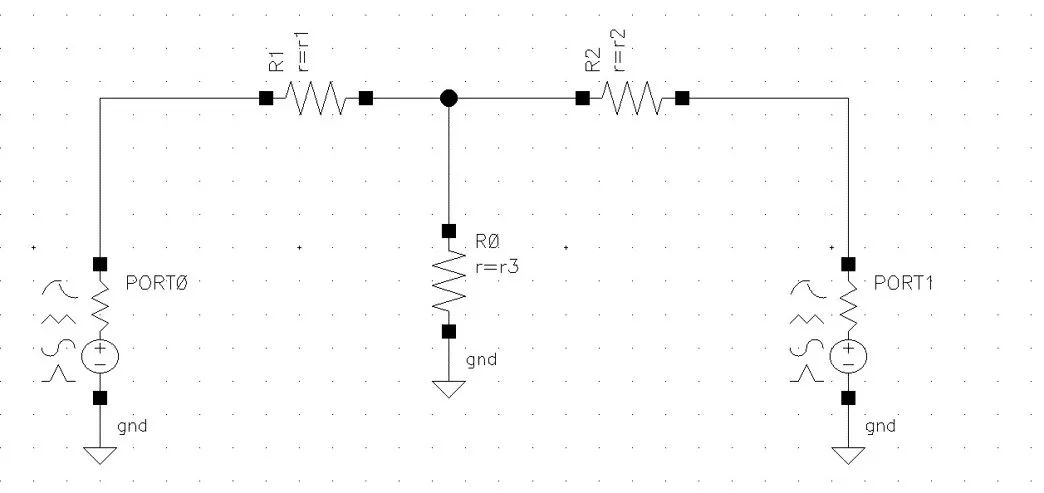

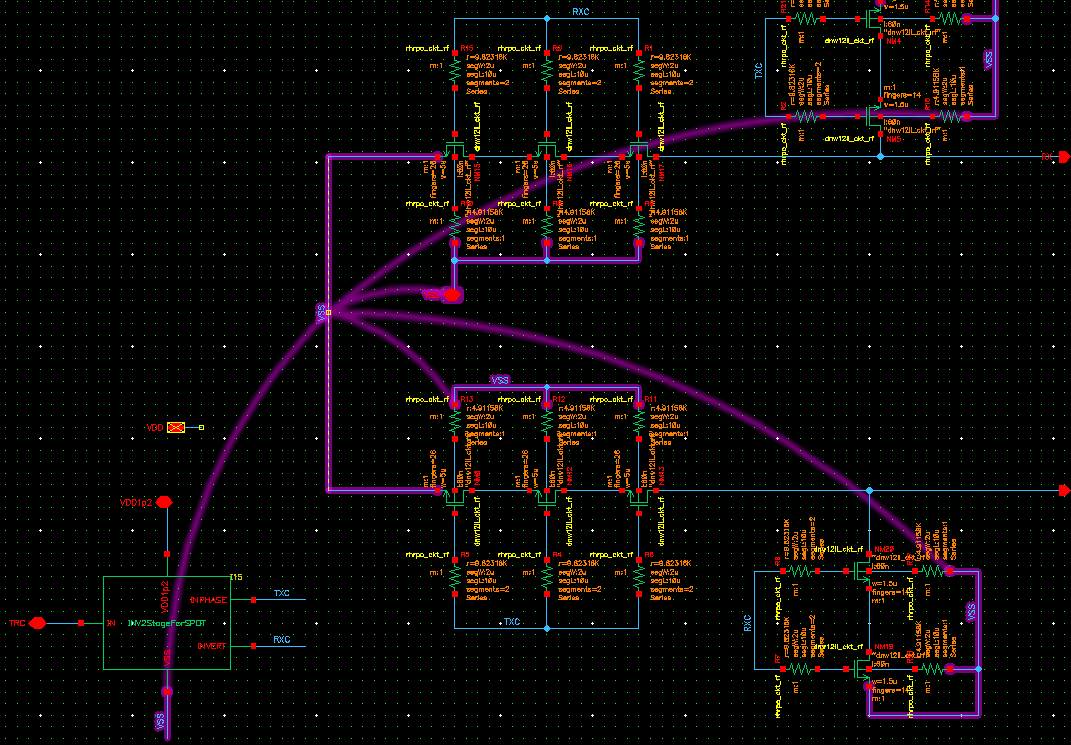

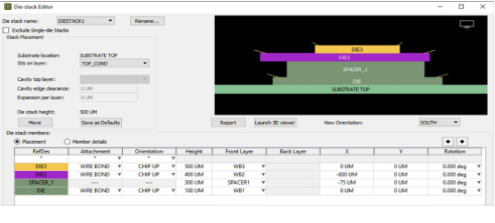

在設計小型化方面,SiP Layout XL為封裝設計者提供了成效顯著的新功能;利用協同設計技術,他們能夠將從封裝環境中直接編輯IC abstrcat 如IO Pad Ring、Bump Matrix和RDL虛擬化連接,然后將封裝設計的建議通過工程更改單(ECO)返標至IC設計團隊;通過Super smooth布線技術, 設計者在確保成品率的同時可實現更高的布線密度,以達到封裝設計小型化;Allegro Constraint Manager中帶有裝配規則檢查(DRC)功能,可確保小型化設計能夠針對共同約束環境中的裝配規則進行檢查;新版的SiP Layout XL支持Windows、Unix或Linux等各種計算機平臺,還擁有三維物理設計效果圖和不同團隊分區設計功能。

最新軟件版本的其他重要功能包括對Wirebond的改進,增強了Leadframe設計中的Wirebonding工藝。另外,Allegro Package Designer現在提供了SiP完成模式,它可以對封裝設計進行讀取和對基板編輯的功能,使APD用戶可以針對最終的artwork/tapeout進行封裝設計準備,實現生產準備設計的就緒。

“我們已經將這些重要的新功能集成在新的軟件版本中,它能夠幫助封裝設計者在協同設計中成為真正的增值合作伙伴”,Cadence產品營銷部門總監Keith Felton表示,“采用最新的Cadence SiP和Allegro Package Designer軟件,可幫助這些工封裝設計工程師在整個半導體設計鏈中成為重要的一環。”

Allegro SiP and IC Packaging 16.3版將于2009年12月初上市。

電子發燒友App

電子發燒友App

評論