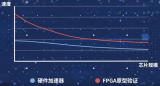

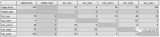

FPGA原型驗證平臺與硬件仿真器在芯片設計和驗證過程中各自發揮著獨特的作用,它們之間存在明顯的區別。

2024-03-15 15:07:03 125

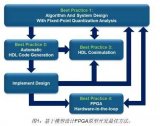

125 FPGA原型驗證流程是確保FPGA(現場可編程門陣列)設計正確性和功能性的關鍵步驟。它涵蓋了從設計實現到功能驗證的整個過程,是FPGA開發流程中不可或缺的一環。

2024-03-15 15:05:33 92

92 TINYFPGA AX1

2024-03-14 22:18:36

TINYFPGA AX2

2024-03-14 22:18:36

TINYFPGA BX

2024-03-14 22:18:36

)和駕駛員信息(DI)的全方面支持。ADAS/AD 領域是賽靈思未來中長期的增長點。而汽車級 ACAP 平臺的推出則是實現自動化駕駛 L4 的基礎。未來智能駕駛技術逐漸成熟,FPGA 用量提升空間巨大

2024-03-08 14:57:22

AMD公司,全球知名的芯片巨頭,近日宣布推出全新的AMD Spartan UltraScale+ FPGA系列產品組合。這一新系列作為AMD成本優化型FPGA、自適應SoC產品家族的最新成員,特別針對成本敏感型邊緣應用進行了優化,旨在提供更高的成本效益和能效性能。

2024-03-07 10:15:40 147

147 我目前正在探索將英飛凌 XMC4300 從控制器與 Xilinx Spartan-6 FPGA 集成到我們項目中的兼容性和通信協議選項。 具體來說,我想了解 XMC4300 是否適用于促進我們在

2024-03-06 07:47:12

今天,英特爾宣布成立全新獨立運營的FPGA公司——Altera。在FPGA Vision線上研討會期間,首席執行官Sandra Rivera和首席運營官Shannon Poulin進行了分享,展示

2024-03-01 11:55:32 200

200

我們用的主平臺是賽靈思,想要通過CYUSB3014+FPGA實現OTG的功能,有幾個問題,想請教一下。

1.是否有可以驗證功能的EVK呢,我找了下FX3 DVK似乎買不到

2024-02-29 07:20:21

根據需求進行重新配置,而ASIC一旦制造完成,其功能就無法更改。

開發周期和成本 :FPGA的開發周期相對較短,成本較低,適合原型驗證和小批量生產。而ASIC的開發周期長,成本較高,但大批量生產時具有

2024-02-22 09:54:36

OMAP-L138(定點/浮點DSP C674x+ARM9)+ FPGA處理器的開發板。

編寫一個用于FPGA訪問ChatGPT 4的程序代碼是一個相當復雜的任務,涉及到硬件設計、網絡通信、數據處理等多個

2024-02-14 21:58:43

芯片原子鐘賽思是一家為萬物互聯同頻的時頻科技企業,基于業界的時頻科研與方案能力,賽思打造出軟硬一體化的時頻產品體系,面向電力、交通、通信、智能樓宇、數據中心、前沿領域等核心場景提供解決方案,持續為

2024-02-02 09:39:57

使用了使用任務編譯器的 Aurix Development Studio IDE。 在將代碼從 GNU 編譯器移植到 TASKING 編譯器的過程中,標準定義庫存在多個問題(編譯錯誤)。

您是否已經擁有

2024-01-31 07:29:03

高云是一家專業從事現場可編程邏輯器件(FPGA)研發與設計的國產FPGA高科技公司,致力于向客戶提供從芯片、EDA開發軟件、IP、開發板到整體系統解決方案的一站式服務。高云半導體在FPGA芯片架構

2024-01-28 17:35:49

陣列邏輯)、GAL(通用陣列邏輯)等可編程器件的基礎上發展起來的產物,屬于一種半定制電路。

它誕生于1985年,發明者是Xilinx公司(賽靈思)。后來,Altera(阿爾特拉)、Lattice(萊迪

2024-01-23 19:08:55

proFPGA是mentor的FPGA原型驗證平臺,當然mentor被西門子收購之后,現在叫西門子EDA。

2024-01-22 09:21:01 546

546

芯片電路圖方案

2024-01-12 18:19:16

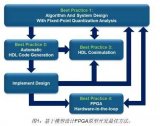

FPGA原型設計是一種成熟的技術,用于通過將RTL移植到現場可編程門陣列(FPGA)來驗證專門應用的集成電路(ASIC),專用標準產品(ASSP)和片上系統(SoC)的功能和性能。

2024-01-12 16:13:01 220

220 高精度低功耗授時模塊衛星板卡,賽思是一家為萬物互聯同頻的時頻科技企業,基于業界的時頻科研與方案能力,賽思打造出軟硬一體化的時頻產品體系,面向電力、交通、通信、智能樓宇、數據中心、前沿領域等核心場景

2024-01-09 13:25:01

,最主流的FPGA開發軟件有兩個,就是賽靈思/AMD的Vivado,還有英特爾的Quartus。這里又來一個二選一,大家要根據自身情況去選擇,比如你們學校教的是誰家的FPGA,或者你用誰家的開發板,或者

2024-01-02 23:03:31

芯片原子鐘賽思是一家為萬物互聯同頻的時頻科技企業,基于業界的時頻科研與方案能力,賽思打造出軟硬一體化的時頻產品體系,面向電力、交通、通信、智能樓宇、數據中心、前沿領域等核心場景提供解決方案,持續為

2023-12-25 14:31:21

模數轉換器AD9625的評估板AD-FMCADC3-EBZ能不能和賽靈思的Virtex7系列FPGA開發板連接,我看到他們都具備JESD204B接口,物理接口上能直接連嗎?還是說需要在使用轉換接口來連接?

2023-12-08 08:25:12

國產有哪些FPGA入門?萊迪思半導體?高云半導體?

2023-12-05 16:05:38

11月23日,中國RISC-V軟硬件生態領導者賽昉科技正式發布自主研發的片上一致性互聯IP——昉·星鏈-700(StarLink-700),并推出基于StarLink-700和昉·天樞-90

2023-11-29 13:37:35

分享易靈思FPGA

2023-11-19 16:13:03

賽昉新聞速遞

11月14日,賽昉科技宣布,其自主研發的RISC-V處理器內核昉·天樞-90(Dubhe-90)獲思朗科技(SmartLogic)采用,用于打造業界性能最強的采用RISC-V內核

2023-11-15 17:03:46

級 FPGA 的推出。目前, 賽靈思最先進的 FPGA 產品是 19 年推出的 Versal (7nm),而賽靈思在 21 年初就推出了宇航級的 Versal XQR,做到了和商業級 同代際

2023-11-09 14:09:46

概念和特點比較簡單,沒有完全形成氣候。

賽靈思:重點布局深耕中國市場

賽靈思公司目前在中國內地設有6家辦事處,公司很多項重要的區域性業務均以中國為基地。例如,亞太區技術支持中心設在上海。另外,針對

2023-11-08 17:19:01

請問下飛思卡爾SC120529VLL6 讀寫能用什么設備讀寫?求助芯片的針腳定義圖?

2023-11-07 07:00:50

2023年10月19日, 思爾芯(S2C) 宣布 北京開源芯片研究院(簡稱“開芯院”) 在其歷代“香山” RISC-V 處理器開發中采用了思爾芯的 芯神瞳 VU19P 原型驗證系統

2023-10-24 16:28:17 317

317 超聲波時靈使不靈,怎么辦呢??

2023-10-19 06:22:18

題。賽昉作為RISC-V硬件和解決方案供應商,一直致力于持續為RISC-V貢獻創新力量,并開啟高端應用體驗的大門。點擊查看更多詳細信息

賽昉團隊宣布推出自產品發布以來關于昉·星光 2的生態月報和生態

2023-10-16 17:46:56

量化

七、Vitis AI 通過遷移學習訓練自定義模型

八、Vitis AI 將自定義模型編譯并部署到KV260中

鋪墊

Vitis AI 是什么?

Vitis AI 是賽靈思公司推出的一款綜合 AI

2023-10-14 15:34:26

所有形式的原型都為驗證硬件設計和驗證軟件提供了強大的方法,模型或多或少地模仿了目標環境。基于FPGA的原型設計在項目的關鍵后期階段尤其有益。用戶有幾個原型設計選項根據他們的主要需求,可以選擇各種基于軟件和硬件的技術來原型他們的設計。

2023-10-11 12:39:41 273

273

多芯粒設計周轉時間 中國上海,2023 年 10 月 8 日——楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布推出新的系統原型驗證流程,該流程基于 Cade

2023-10-08 15:55:01 249

249 可編程器件的領先供應商,今日宣布推出萊迪思CrossLinkU?-NX FPGA產品系列,這是業界首款同級產品中集成USB器件功能的FPGA。CrossLinkU-NX FPGA通過硬核USB控制器

2023-10-08 14:39:07 573

573 SDK 是一種構建在開源且被廣泛采用的 GStreamer 框架上的應用框架。這種SDK 設計上支持跨

所有賽靈思平臺的無縫開發,包括賽靈思 FPGA、SoC、Alveo 卡,當然還有 Kria

2023-09-26 15:17:29

作為集創賽(全國大學生集成電路創新創業大賽)和全國大學生FPGA競賽紫光同創賽道官方定制FPGA開發板,紫光同創大學計劃協同育人高校推薦開發板,盤古50K開發板已在100+所高校推廣使用。這款

2023-09-20 17:34:13

2023年8月,微雪電子(Waveshare Electronics)宣布推出旗下最新產品——基于賽昉科技VisionFive 2的嵌入式一體機外殼。這款外殼不僅融合了創新設計,內置散熱風扇和散熱口

2023-09-08 15:07:15

在 Hot Chips 2023 上,我們獲得了有關 AMD Versal Premium VP1902 FPGA 的更多信息。我們之前在文章《世界上最大的FPGA發布》中說到,這是一個巨大的芯片,專為制作更大芯片的原型而設計。

2023-09-05 11:17:11 719

719

描述 Artix?-7 器件在單個成本優化的 FPGA 中提供了最高性能功耗比結構、 收發器線速、DSP 處理能力以及 AMS 集成。包含 MicroBlaze? 軟處理器和 1,066

2023-09-01 10:47:25

描述 Virtex?-7 FPGA 針對 28nm 系統性能與集成進行了優化,可為您的設計帶來業界最佳的功耗性能比架構、DSP 性能以及 I/O 帶寬。 該系列可用于 10G 至 100G

2023-09-01 10:41:54

描述 Kintex? UltraScale? 器件在 20nm 節點提供最佳成本/性能/功耗比,包括在中端器件、下一代收發器和低成本封裝中的最高信號處理帶寬,實現性能與成本效益的最佳組合。此系列適合 100G 網絡和數據中心應用的包處理,以及下一代醫療成像、 8k4k 視頻和異構無線基礎設施所需的 DSP 密集型處理。特性 可編程系統集成

2023-09-01 10:24:44

MPS2和MPS2+FPGA原型板是ARM Cortex-M評估和開發的開發平臺。

MPS2和MPS2+FPGA原型板提供以下功能:

Altera Cyclone FPGA和主板上電和配置MPS2

2023-08-18 07:25:28

Arm MPS3 FPGA原型板配有SO-DIMM存儲模塊。該模塊未在工廠安裝,以減少其在運輸過程中損壞的可能性。要安裝內存模塊,首先將其以一定角度滑入插槽(如圖2所示),使模塊邊緣連接器中的插槽

2023-08-10 07:10:30

描述 Spartan?-6 器件可提供各種業界領先的連接特性,如高邏輯引腳比、小型封裝、MicroBlaze? 軟處理器、800Mb/s DDR3 支持以及各種多樣化支持性 I/O 協議等

2023-08-08 11:55:55

芯片設計和驗證工程師通常要為在硅片上實現的每一行RTL代碼寫出多達10行測試平臺代碼。驗證任務在設計周期內可能會占用50%或更多的時間。盡管如此辛 苦,仍有接近60%的芯片存在功能瑕疵,需要返工。由于HDL仿真不足以發現系統級錯誤,芯片設計人員正利用FPGA來加速算法創建和原型設計。

2023-08-06 10:49:09 971

971

存在功能瑕疵,需要返工。由于HDL 仿真 不足以發現系統級錯誤,芯片設計人員正利用 FPGA 來加速算法創建和原型設計。 利用FPGA處理大型測試數據集可以使工程師快速評估算法和架構并迅速做出權衡。工程師也可以在實際環境下測試設計,避免因使用HD

2023-08-06 10:45:02 335

335

而在今年,Meta將展示兩款原型頭顯:Butterscotch Varifocal將展示近視網膜分辨率和變焦光學器件,而 Flamera則驗證了一種新穎的無重投影的真實世界透視方法。

2023-08-04 11:05:30 520

520 我是大二的電子信息工程在讀生,目前沒有接觸過32方向的任何東西,只學習了一個學期的FPGA并參加了集創賽,感覺FPGA的學習難度還是很大的。但是我在網上搜索FPGA時,感覺大家對它的前景并不看好,在

2023-07-26 11:04:06

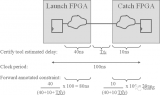

當SoC系統的規模很大的時候,單片FPGA驗證平臺已經無法容納這么多容量,我們將采取將SoC設計劃分為多個FPGA的映射。

2023-06-19 15:42:08 543

543 FPGA做IC的原型驗證,速度大概跑多少?很多ASIC運行主頻遠遠高于FPGA,仿真能cover住嗎?

2023-06-19 09:49:00 542

542

綜合工具的任務是將SoC設計映射到可用的FPGA資源中。自動化程度越高,構建基于FPGA的原型的過程就越容易、越快。

2023-06-13 09:27:06 277

277

【視頻】紫光同創Logos系列PGL50H關鍵特性評估板@盤古50K開發板#小眼睛FPGA盤古系列開發板@集創賽官方定制 基于紫光同創40nm工藝的FPGA(Logos系列:PGL50H-6IFBG484)關鍵特性評估板~

2023-06-12 18:07:15

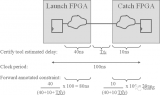

多片FPGA之間的互連,經常提到多路復用的概念,也經常提到TDM的概念,正確理解多路復用在多片FPGA原型驗證系統中的機理,尤其是時序機制,對于我們正確看待和理解多片FPGA原型系統的性能有很好的促進作用。下圖是一個使用多路復用器后接采樣FF的多路復用解決方案的示例。

2023-06-06 10:04:35 577

577

設計中的1/9)要求一個基于多個FPGA的原型開發板。 在不太遙遠的過去,對ASIC設計團隊而言,在這類情況下主要的解決方案就是在內部建立他們自己的定制多個FPGA的原型開發板。然而,今天,使用現成的多個FPGA原型開發板——例如,由Synplicity公司的原型開發伙伴生產的開發板——與合適

2023-06-04 16:50:01 699

699 大家好,我的需求是將FPGA(賽靈思K7)采集的數據發送至工控機(Linux),數據量為每秒5M字節,并解析工控機發送的控制指令(50字節/秒),有同個問題如下:

1.ARM選什么型號比較好

2023-06-02 18:25:04

在現代SoC芯片驗證過程中,不可避免的都會使用FPGA原型驗證,或許原型驗證一詞對你而言非常新鮮,但是FPGA上板驗證應該是非常熟悉的場景了。

2023-05-30 15:04:06 905

905

我們當然希望在項目中盡快準備好基于FPGA原型驗證的代碼,以便最大限度地為軟件團隊和RTL驗證人員帶來更客觀的收益。

2023-05-30 11:10:27 769

769

多片FPGA的原型驗證系統的性能和容量通常受到FPGA間連接的限制。FPGA中有大量的資源,但IO引腳的數量受封裝技術的限制,通常只有1000個左右的用戶IO引腳。

2023-05-23 17:12:35 1149

1149

FPGA原型驗證系統要盡可能多的復用SoC相關的模塊,這樣才是復刻SoC原型的意義所在。

2023-05-23 16:50:34 381

381

如果SoC設計規模小,在單個FPGA內可以容納,那么只要系統中的FPGA具有所SoC所設計需要時鐘的數量

2023-05-23 15:46:24 481

481

當SoC的規模在一片FPGA中裝不下的時候,我們通常選擇多片FPGA原型驗證的平臺來承載整個SoC系統。

2023-05-23 15:31:10 319

319 假如給定FPGA內的時鐘沒有正確運行,那么我們多片FPGA系統的整體將不能同時啟動,這將有可能是致命的。

2023-05-22 09:21:24 133

133

FPGA原型驗證的原理是將芯片RTL代碼綜合到FPGA上來驗證芯片的功能。對于目前主流行業應用而言,芯片規模通常達到上億門甚至數十億門,一顆FPGA的容量難以容納下芯片的所有邏輯功能。

2023-05-18 12:52:52 381

381

SoC的頂層的約束適用于FPGA到其各自時鐘域中的各個Flip_Flop,如果定義了跨時鐘域,也適用于FPGA之間。當我們可以確保每個FPGA邊界都有一個IOFF,它與SoC中相應的元素對齊時,這一點對于性能而言非常重要。

2023-05-13 09:38:09 1351

1351

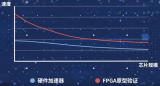

FPGA原型在數字芯片設計中非常重要,因為相比用仿真器,或者加速器等來跑仿真,FPGA的運行速度,更接近真實芯片,可以配合軟件開發者來進行底層軟件的開發。這一流片前的軟硬件的協同開發,是其最不可替代的地方。

2023-05-10 10:44:00 4775

4775

當SoC的規模在一片FPGA中裝不下的時候,我們通常選擇多片FPGA原型驗證的平臺來承載整個SoC系統。

2023-05-10 10:15:16 187

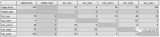

187 多片FPGA原型驗證系統的拓撲連接方式各不相同,理想的多片FPGA原型驗證系統應該可以靈活配置,可以使用其相應的EDA工具

2023-05-08 11:51:40 326

326

在進行FPGA原型驗證的過程中,當要把大型的SoC進行FPGA原型驗證時,有時候會遇到一種情況,同樣的接口分兩組出去到不同的模塊,而這兩個模塊規模較大,又需要分割在兩片FPGA中,這時候就會像下圖一樣。

2023-05-04 16:21:34 426

426

對SoC芯片要進行FPGA原型驗證,假如設計較大,要將SoC中不同功能模塊或者邏輯模塊分別分配到特定的FPGA,那么對SoC的分割策略尤為重要

2023-04-27 15:17:06 627

627

盡管對于工程師而言目標始終是以原始形式對SoC源RTL進行原型化,但在原型化工作的早期,SoC設計必須進行必要的修改,以適應FPGA原型系統。

2023-04-26 09:48:13 747

747 在進行FPGA原型驗證的過程中,當要把大型的SoC進行FPGA原型驗證時,有時候會遇到一種情況,同樣的接口分兩組出去到不同的模塊,而這兩個模塊規模較大,又需要分割在兩片FPGA中,這時候就會像下圖一樣:

2023-04-25 11:15:20 1629

1629

-------------------------------------------------------------------為了讓電子發燒友社區開發者們定期體驗試用不同的開發板,現不定期推出免費試用活動。

第二十期試用的樣品為 FPB-RA6E1快速原型板:開發板簡介:RA6E1 快速原型

2023-04-24 10:15:53

FPGA原型驗證系統要盡可能多的復用SoC相關的模塊,這樣才是復刻SoC原型的意義所在。

2023-04-19 09:08:15 848

848 FPGA與FPGA之間互連對信號延遲的影響,兩片FPGA的IO之間每一個額外的過渡,例如連接器、焊點甚至板內通孔,都會增加一些阻抗,從而降低信號質量,并增加信號之間串擾的概率。然而,經過仔細分析,發現這并不是一個想象中的大問題。主要矛盾是FPGA互連線的影響。

2023-04-16 10:21:51 513

513 可以達到200Mbps,同時接收延時小于6ns,滿足時鐘敏感應用的要求。NLC530x從設計、制造到封裝測試實現全流程國產化,穩定確保了供應的安全與可靠,以更好地滿足客戶的交付需求。NLC530x系列

2023-04-13 15:22:28

多片FPGA的原型驗證系統的性能和容量通常受到FPGA間連接的限制。FPGA中有大量的資源,但IO引腳的數量受封裝技術的限制

2023-04-12 10:14:42 673

673 FPGA原型驗證平臺系統靈活性主要體現在其外部連接表現形式,由單片FPGA平臺或者2片的FPGA,抑或是4片的FPGA組成一個子系統。

2023-04-11 09:50:37 442

442 FPGA原型驗證平臺系統靈活性主要體現在其外部連接表現形式,由單片FPGA平臺或者2片的FPGA,抑或是4片的FPGA組成一個子系統。

2023-04-11 09:50:03 626

626 FPGA原型設計是一種成熟的技術,用于通過將RTL移植到現場可編程門陣列(FPGA)來驗證專門應用的集成電路(ASIC),專用標準產品(ASSP)和片上系統(SoC)的功能和性能。

2023-04-10 09:23:29 947

947 如果SoC設計規模小,在單個FPGA內可以容納,那么只要系統中的FPGA具有所SoC所設計需要時鐘的數量

2023-04-07 09:42:57 594

594 MODULE USB-TO-FPGA TRAINING TOOL

2023-04-06 11:27:13

MODULE USB-TO-FPGA SPARTAN3

2023-04-06 11:27:13

MODULE USB-TO-FPGA SPARTAN 3A

2023-04-06 11:27:11

當SoC系統的規模很大的時候,單片FPGA驗證平臺已經無法容納這么多容量,我們將采取將SoC設計劃分為多個FPGA的映射。

2023-04-06 11:20:48 602

602 FPGA原型平臺的性能估計與應用過程的資源利用率以及FPGA性能參數密切相關,甚至FPGA的制程也是一個因素。

2023-04-04 09:49:04 1474

1474 FPGA原型驗證在數字SoC系統項目當中已經非常普遍且非常重要,但對于一個SoC的項目而言,選擇合適的FPGA原型驗證系統顯的格外重要

2023-04-03 09:46:45 924

924 、通信、醫療、安防等工業領域,與6大主流工業處理器原廠強強聯合,包括德州儀器(TI)、恩智浦(NXP)、賽靈思(Xilinx)、全志科技、瑞芯微、紫光同創,產品架構涵蓋ARM、FPGA、DSP

2023-03-31 16:19:06

BOARD EVAL FOR ORCA OR4E6 FPGA

2023-03-30 11:49:36

我們當然希望在項目中盡快準備好基于FPGA原型驗證的代碼,以便最大限度地為軟件團隊和RTL驗證人員帶來更客觀的收益。

2023-03-28 14:11:15 768

768 那個商業行為背后的動機,只是想以此為契機從技術的角度,略略討論下這次收購背后的關鍵因素——FPGA和ASIC的在AI計算中銜接關系。因為并不是專家,所以如有錯誤理解請指出。 從FPGA到ASIC

2023-03-28 11:14:04

在現代SoC芯片驗證過程中,不可避免的都會使用FPGA原型驗證,或許原型驗證一詞對你而言非常新鮮,但是FPGA上板驗證應該是非常熟悉的場景了。

2023-03-28 09:33:16 854

854

電子發燒友App

電子發燒友App

評論