在幾十年前,片上系統(tǒng)(SOC)這個(gè)術(shù)語(yǔ)還只是一個(gè)流行詞。如今,它是繼續(xù)推動(dòng)電子領(lǐng)域發(fā)展的一項(xiàng)重要技術(shù)。SoC的增加是集成和嵌入式計(jì)算日益增長(zhǎng)的主流趨勢(shì)的一部分,這使得計(jì)算設(shè)備變得更小、更便宜、更快

2024-03-19 08:26:28 71

71

ARM? Cortex?-M4 嵌入式 - 片上系統(tǒng) (SoC) IC G30 .NET 84MHz 64-LQFP(10x10)

2024-03-14 20:16:59

片上系統(tǒng)(簡(jiǎn)稱SoC)是半導(dǎo)體工業(yè)中常用的一個(gè)術(shù)語(yǔ)。它指的是將計(jì)算機(jī)或其他電子系統(tǒng)的所有必要組件集成到單個(gè)芯片上的一種微芯片。

2024-03-08 10:29:26 762

762

三星電子近日宣布,公司成功研發(fā)并發(fā)布了其首款12層堆疊HBM3E DRAM,即HBM3E 12H,該產(chǎn)品在帶寬和容量上均實(shí)現(xiàn)了顯著的提升,這也意味著三星已開(kāi)發(fā)出業(yè)界迄今為止容量最大的新型高帶寬存儲(chǔ)器(HBM)。

2024-03-08 10:10:51 158

158 Cx3開(kāi)發(fā)板(s)I2C最大速率可以設(shè)置到1MHz嗎?當(dāng)前接口CyU3PMipicsiInitializeI2c 最大只能400K,有沒(méi)有其他接口實(shí)現(xiàn)提速的?

2024-02-28 06:10:09

擴(kuò)展性較好,可以通過(guò)增加芯片數(shù)量或使用更大容量的芯片來(lái)滿足更高的性能需求。而ASIC的可擴(kuò)展性相對(duì)較差,需要重新設(shè)計(jì)和制造。

驗(yàn)證和調(diào)試 :FPGA的驗(yàn)證和調(diào)試過(guò)程相對(duì)簡(jiǎn)單,可以在系統(tǒng)級(jí)進(jìn)行仿真和測(cè)試。而

2024-02-22 09:54:36

(128UL)Buffer1緩存最大僅是(128UL)嗎?

uint8_t buffer[BUFFER_SIZE];

(void) Cy_SCB_EZI2C_Init(EZI2C

2024-02-02 06:18:04

EDA全流程的重大專項(xiàng),開(kāi)啟國(guó)產(chǎn)EDA研發(fā)新篇章。S2C的內(nèi)涵1=SiliconvalleytoChina(硅谷到中國(guó))S2C的內(nèi)涵2=SystemtoChip(系統(tǒng)

2024-01-26 08:23:04 360

360

Circuit,專用集成電路),就是一種專用于特定任務(wù)的芯片。

ASIC的官方定義,是指:應(yīng)特定用戶的要求,或特定電子系統(tǒng)的需要,專門設(shè)計(jì)、制造的集成電路。

ASIC起步于上世紀(jì)70-80年代

2024-01-23 19:08:55

干式變壓器最大容量是指能夠安全、穩(wěn)定地運(yùn)行的干式變壓器的最大功率容量。干式變壓器是一種常用的電力設(shè)備,其主要功能是將高壓電能轉(zhuǎn)變?yōu)榈蛪弘娔埽蛘邔⒌蛪弘娔苻D(zhuǎn)變?yōu)楦邏弘娔堋8墒阶儔浩饔捎诓捎酶墒嚼@組

2024-01-15 11:47:36 330

330 FPGA原型設(shè)計(jì)是一種成熟的技術(shù),用于通過(guò)將RTL移植到現(xiàn)場(chǎng)可編程門陣列(FPGA)來(lái)驗(yàn)證專門應(yīng)用的集成電路(ASIC),專用標(biāo)準(zhǔn)產(chǎn)品(ASSP)和片上系統(tǒng)(SoC)的功能和性能。

2024-01-12 16:13:01 220

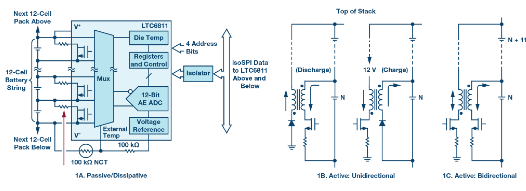

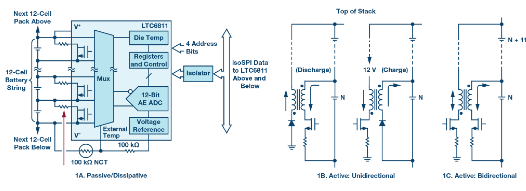

220 把LTC6811的C文件和頭文件添加到工程里后,編譯顯示cell_asic沒(méi)有定義,啥意思?

void LTC6811_init_cfg(uint8_t total_ic, //!<

2024-01-05 11:53:52

ASIC設(shè)計(jì)服務(wù)暨IP研發(fā)銷售廠商智原科技(Faraday Technology Corporation,TWSE:3035)提供完整的FinFET 14納米ASIC整合設(shè)計(jì)開(kāi)發(fā)服務(wù),搭配SoC驗(yàn)證平臺(tái)與高速傳輸IP解決方案

2023-12-26 18:20:56 356

356 什么是短路容量?什么是遮斷容量? 短路容量和遮斷容量是電力系統(tǒng)中兩個(gè)重要的概念。在這篇文章中,我們將詳細(xì)解釋這兩個(gè)概念,并探討它們?cè)陔娏?b class="flag-6" style="color: red">系統(tǒng)中的作用和關(guān)鍵作用。 首先,讓我們來(lái)了解短路容量。短路容量

2023-12-25 14:37:11 573

573 了最大閾值嗎? 問(wèn)題二: 最大SOC閾值是根據(jù)SAlrtTh寄存器(芯片手冊(cè)Figure 61. SAlrtTh (003h)/nSAlrtTh (1C2h) Format)設(shè)置的,我的至是FF00,轉(zhuǎn)換成10進(jìn)制是多少? 問(wèn)題三: Status(6c:00)寄存器變?yōu)?X4080為什么會(huì)有假電流?

2023-12-25 08:21:49

請(qǐng)問(wèn)AD2S1210串行通訊的最大波特率是多少?

2023-12-18 08:10:54

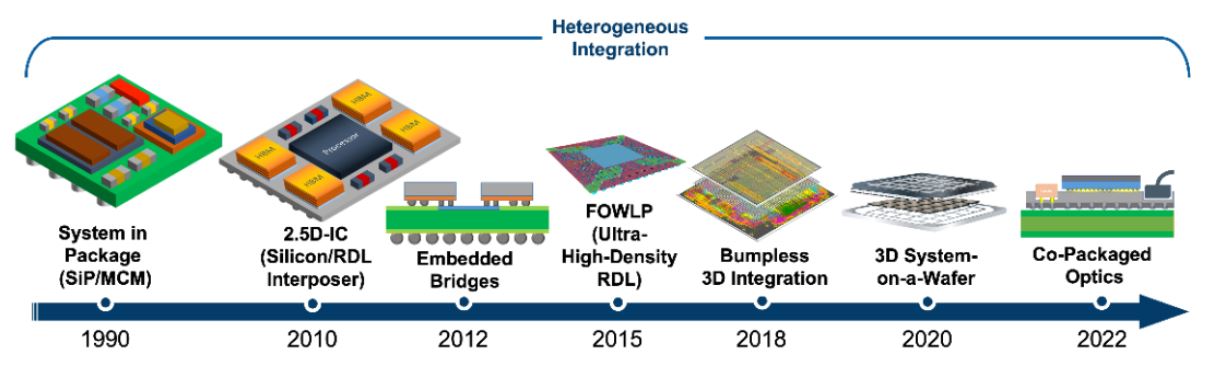

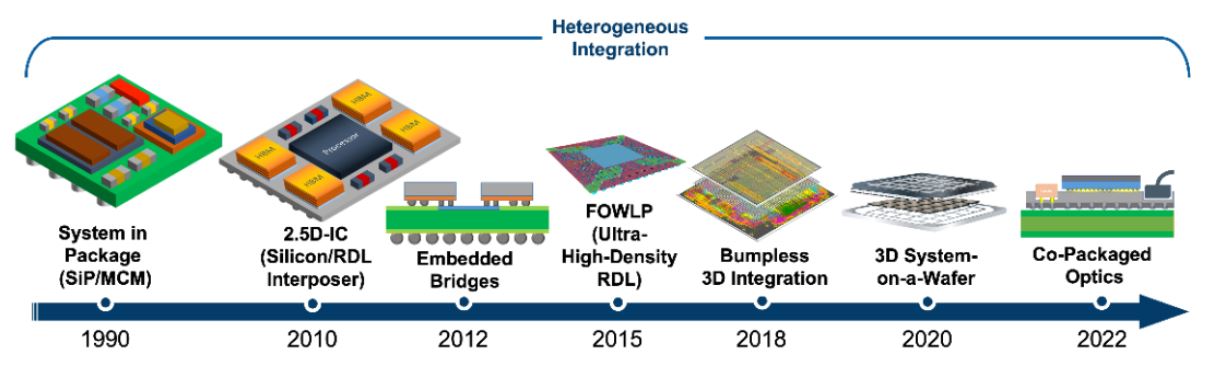

異構(gòu)集成 (HI) 與系統(tǒng)級(jí)芯片 (SoC) 有何區(qū)別?

2023-11-29 15:39:38 439

439

等參數(shù)進(jìn)行監(jiān)控和分析,通過(guò)一系列計(jì)算得出電池的剩余容量。 為什么要進(jìn)行SOC估算? SOC估算的主要作用是提高電池使用的安全性、準(zhǔn)確性和可靠性。在電動(dòng)汽車、混合動(dòng)力汽車、儲(chǔ)能系統(tǒng)等領(lǐng)域,電池狀態(tài)的估算非常重要,因?yàn)檫@些應(yīng)用對(duì)電池的容量和剩余電量的準(zhǔn)確度有非常

2023-10-26 11:38:30 1503

1503 2023年10月19日,思爾芯(S2C)宣布北京開(kāi)源芯片研究院(簡(jiǎn)稱“開(kāi)芯院”)在其歷代“香山”RISC-V處理器開(kāi)發(fā)中采用了思爾芯的芯神瞳VU19P原型驗(yàn)證系統(tǒng),不僅加速了產(chǎn)品迭代,還助力多家企業(yè)

2023-10-25 08:24:04 302

302

2023年10月19日, 思爾芯(S2C) 宣布 北京開(kāi)源芯片研究院(簡(jiǎn)稱“開(kāi)芯院”) 在其歷代“香山” RISC-V 處理器開(kāi)發(fā)中采用了思爾芯的 芯神瞳 VU19P 原型驗(yàn)證系統(tǒng)

2023-10-24 16:28:17 317

317 電子發(fā)燒友網(wǎng)站提供《汽車系統(tǒng)ASIC、ASSP和EMC設(shè)計(jì).pdf》資料免費(fèi)下載

2023-10-19 10:55:40 0

0 所有形式的原型都為驗(yàn)證硬件設(shè)計(jì)和驗(yàn)證軟件提供了強(qiáng)大的方法,模型或多或少地模仿了目標(biāo)環(huán)境。基于FPGA的原型設(shè)計(jì)在項(xiàng)目的關(guān)鍵后期階段尤其有益。用戶有幾個(gè)原型設(shè)計(jì)選項(xiàng)根據(jù)他們的主要需求,可以選擇各種基于軟件和硬件的技術(shù)來(lái)原型他們的設(shè)計(jì)。

2023-10-11 12:39:41 273

273

我國(guó)單體裝機(jī)規(guī)模最大的露天礦排土場(chǎng)光儲(chǔ)電站——國(guó)能北電勝利能源露天排土場(chǎng)200MWp光伏項(xiàng)目成功實(shí)現(xiàn)全容量并網(wǎng)發(fā)電。

2023-10-09 10:38:46 184

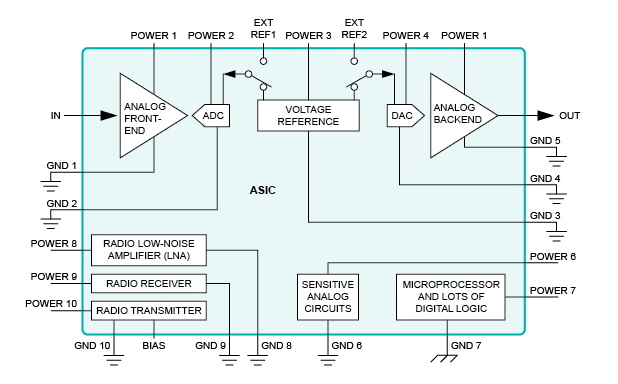

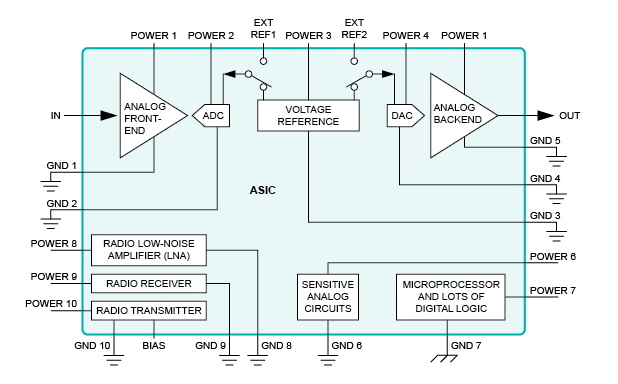

184 噪聲是混合信號(hào) ASIC 中的一個(gè)常見(jiàn)問(wèn)題,會(huì)降低性能并危及產(chǎn)品的完成度。本應(yīng)用筆記提供了添加外部電路的提示和技巧,使許多 ASIC 可用于原型設(shè)計(jì)或作為終產(chǎn)品進(jìn)行交付。討論了通過(guò)校正模擬電路中的噪聲、進(jìn)行調(diào)整、校準(zhǔn)增益和偏移以及清潔電源來(lái)優(yōu)化 ASIC 的方法。

2023-10-04 17:30:00 70

70

在一個(gè)SoC的系統(tǒng)結(jié)構(gòu)設(shè)計(jì)中,除了硬件結(jié)構(gòu)以外,軟件結(jié)構(gòu)的設(shè)計(jì)對(duì)整個(gè)SoC的性能有很大的影響。

2023-09-25 15:14:31 547

547 驗(yàn)證SoC困難的部分原因是它的狀態(tài)依賴于許多變量,包括它以前的狀態(tài)、輸入序列和SoC輸出的更廣泛的系統(tǒng)效應(yīng)(和可能的反饋)。

以實(shí)時(shí)連接到系統(tǒng)其他部分的速度運(yùn)行SoC設(shè)計(jì),可以讓我們能夠看到實(shí)時(shí)條件、輸入和系統(tǒng)反饋發(fā)生變化時(shí)的即時(shí)影響。

2023-09-25 12:22:40 454

454

如何檢測(cè)24c存儲(chǔ)器容量

2023-09-25 06:48:32

請(qǐng)問(wèn)K210支持的最大FLASH容量是多少?SPI-FLASH訪問(wèn)的地址長(zhǎng)度是多少?數(shù)據(jù)長(zhǎng)度是多少?

2023-09-14 08:57:16

我想請(qǐng)問(wèn)一下:

1、NVMe SSD的最大規(guī)格支持到 多大容量?500GB?1TB?2TB?以及PCIe版本和通道數(shù),3.0[i]4或者4.04的版本可以嗎?還是?

2、所支持的TF存儲(chǔ)卡的最大規(guī)格,是多大容量?

3、板子背面eMMC的空位如果要用起來(lái)的話,有什么型號(hào)推薦嗎,怎么用?

非常感謝!

2023-09-12 07:44:25

ASIC和SOC芯片是電子設(shè)備中常用的兩種芯片類型,它們?cè)谠O(shè)計(jì)上有一些相同點(diǎn)和不同點(diǎn)。本文將通過(guò)舉例說(shuō)明這些特點(diǎn),以便更好地理解它們的設(shè)計(jì)差異和應(yīng)用場(chǎng)景。

2023-09-04 09:45:09 860

860 FPGA原型板提供Altera Cyclone 5CEA7 FPGA,MPS2+FPGA原型板提供Altera Cyclone 5CEA9 FPGA,速度均為C8級(jí)。

這兩個(gè)主板都支持ARM

2023-08-18 07:25:28

在現(xiàn)代電力系統(tǒng)中,電容器被廣泛用于提高系統(tǒng)的功率因數(shù)和穩(wěn)定電壓。而在低壓電力電容器中,選取單支電容器的最大容量是至關(guān)重要的。如何確保單支低壓電力電容器的最大容量,更是重中之重!那么,該如何保障呢?

2023-08-16 16:36:02 353

353 請(qǐng)問(wèn)蜂鳥E203的代碼可以做asic綜合嗎? 如果需要的話需要把那些文件加進(jìn)去呢?是要把rtl文件里的 core,debug,fab,general,mems,periphs,soc,subsys

2023-08-16 07:09:47

如題,我們嘗試在Nexys Video上移植開(kāi)源蜂鳥E203 Soc.但是開(kāi)發(fā)板上flash的型號(hào)與官方板不同,Nexys Video上的flash型號(hào)是S25FL256,與官方的容量不同,請(qǐng)問(wèn)移植時(shí)是否兼容呢?需要在工程或者NucleiStudio中修改哪些地方呢

2023-08-12 07:41:51

Morello系統(tǒng)開(kāi)發(fā)平臺(tái)(SDP)是一個(gè)開(kāi)發(fā)平臺(tái),用于硬件原型、軟件開(kāi)發(fā)、系統(tǒng)驗(yàn)證和性能剖析或調(diào)試。它由SDP原型開(kāi)發(fā)板組成,由Morello Syste-Chip(SOC)運(yùn)行一個(gè)開(kāi)放源軟件堆

2023-08-12 07:25:49

耦合SRAM、寫緩沖器和AMBA AHB總線接口。提供這個(gè)完整的高頻子系統(tǒng)使SoC設(shè)計(jì)者能夠?qū)W⒂谄?b class="flag-6" style="color: red">系統(tǒng)特有的設(shè)計(jì)問(wèn)題。該設(shè)備的可合成特性便于集成到ASIC技術(shù)中。

ARM966E-S宏單元內(nèi)的緊密

2023-08-02 07:46:42

隨著現(xiàn)代微控制器和SoC變得越來(lái)越復(fù)雜,設(shè)計(jì)者面臨著最大化能源效率,同時(shí)實(shí)現(xiàn)更高水平的集成。最大限度地提高能量在低功耗SoC市場(chǎng)中,多個(gè)功率域的使用被廣泛采用。在

同時(shí),為了解決更高級(jí)別的集成,許多

2023-08-02 06:34:14

、請(qǐng)?jiān)谑盏綍?b class="flag-6" style="color: red">2個(gè)星期內(nèi)提交不少于一篇試讀報(bào)告要求300字以上圖文并茂。4、試讀報(bào)告發(fā)表在電子發(fā)燒友論壇>> 社區(qū)活動(dòng)專版標(biāo)題名稱必須包含《SoC底層軟件低功耗系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

2023-07-28 11:09:40

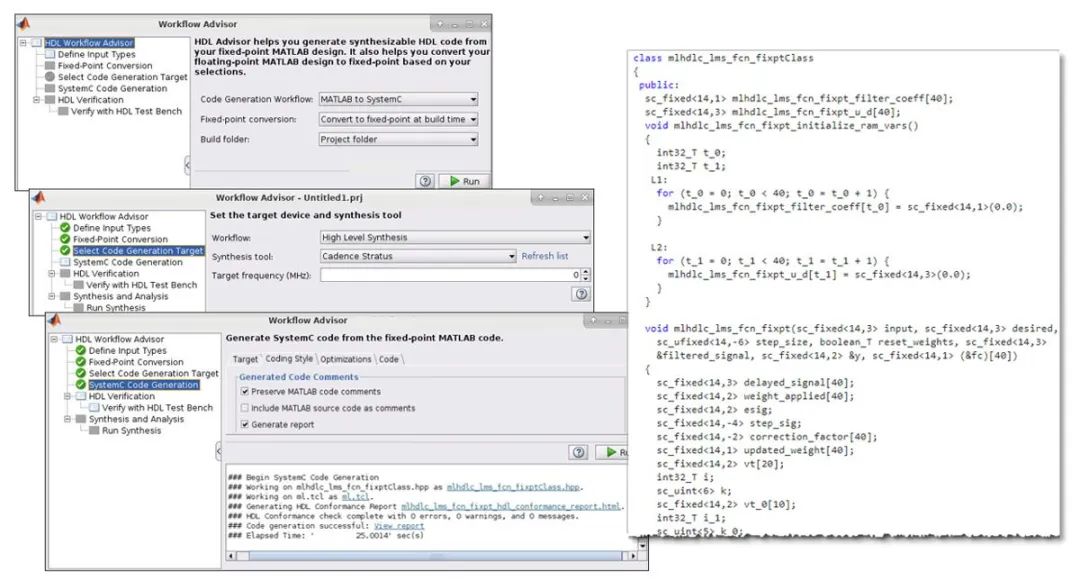

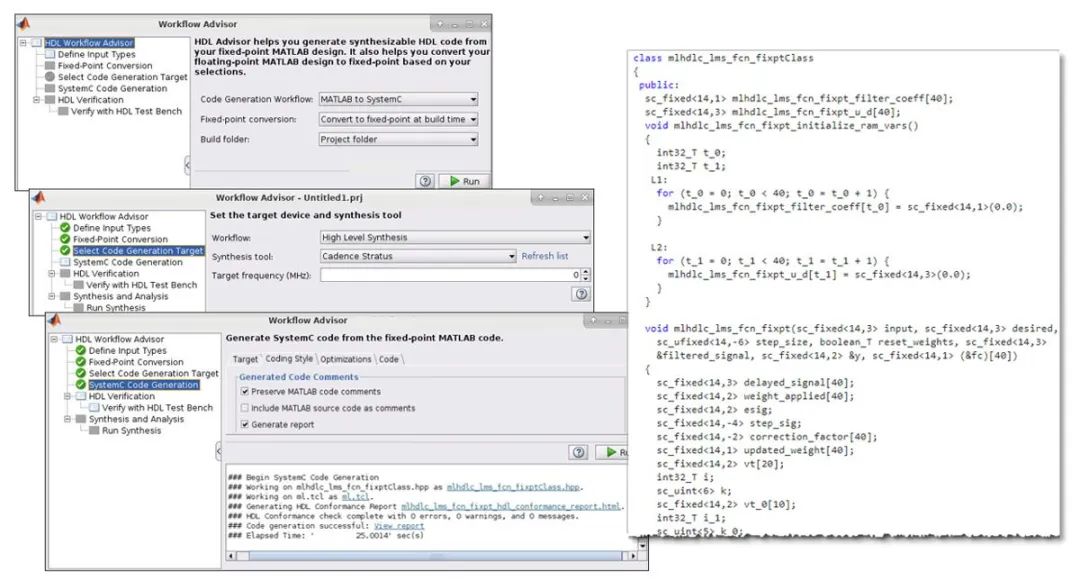

ASIC 設(shè)計(jì)是開(kāi)發(fā)復(fù)雜電子系統(tǒng)的過(guò)程。該系統(tǒng)可制造成特殊用途的半導(dǎo)體設(shè)備,通常用于大批量應(yīng)用或具有嚴(yán)格的功耗、性能和尺寸限制的應(yīng)用。ASIC 系統(tǒng)設(shè)計(jì)人員使用高級(jí)語(yǔ)言并通過(guò)仿真和可視化來(lái)開(kāi)發(fā)和評(píng)估算法。

2023-07-20 10:29:04 528

528

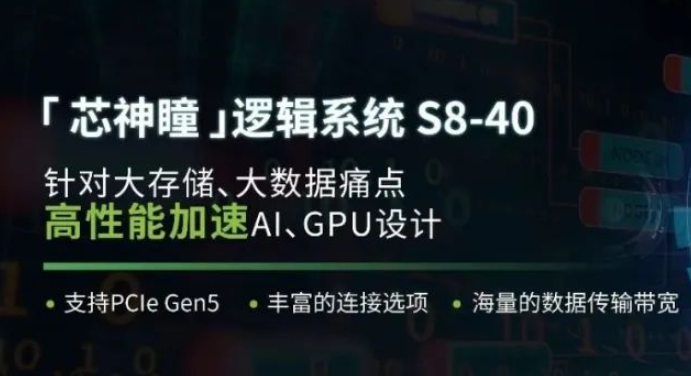

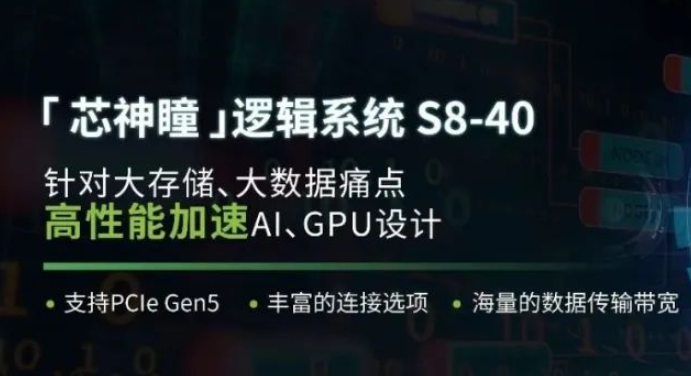

業(yè)內(nèi)知名的數(shù)字前端EDA供應(yīng)商思爾芯(S2C)發(fā)布了最新一代原型驗(yàn)證解決方案“芯神瞳邏輯系統(tǒng)S8-40”。據(jù)悉,S8-40適用于處理復(fù)雜的邏輯電路和大規(guī)模數(shù)據(jù),可支持諸多高帶寬協(xié)議。

2023-07-06 14:56:29 367

367

2023年7月4日,業(yè)內(nèi)知名的數(shù)字前端EDA供應(yīng)商思爾芯(S2C),發(fā)布了最新一代原型驗(yàn)證解決方案——芯神瞳邏輯系統(tǒng)S8-40。新產(chǎn)品除了支持PCIeGen5,還擁有豐富的連接選項(xiàng),海量的數(shù)據(jù)傳輸

2023-07-05 10:08:19 335

335

在看新唐IIC例程時(shí),這行不明白什么意思,特請(qǐng)教一下,這是函數(shù)調(diào)用嗎? s_I2C0HandlerFn = (I2C_FUNC)I2C_MasterTx;怎么不用寫參數(shù)嗎?

/* I2C

2023-06-25 07:18:46

當(dāng)SoC系統(tǒng)的規(guī)模很大的時(shí)候,單片F(xiàn)PGA驗(yàn)證平臺(tái)已經(jīng)無(wú)法容納這么多容量,我們將采取將SoC設(shè)計(jì)劃分為多個(gè)FPGA的映射。

2023-06-19 15:42:08 543

543 在集成電路界ASIC被認(rèn)為是一種為專門目的而設(shè)計(jì)的集成電路,是指應(yīng)特定用戶要求和特定電子系統(tǒng)的需要而設(shè)計(jì)、制造的集成電路。ASIC的特點(diǎn)是面向特定用戶的需求,ASIC在批量生產(chǎn)時(shí)與通用集成電路相比具有體積更小、功耗更低、可靠性提高、性能提高、保密性增強(qiáng)、成本降低等優(yōu)點(diǎn)。

2023-06-19 11:07:31 3404

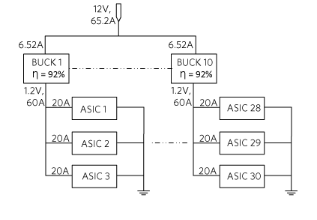

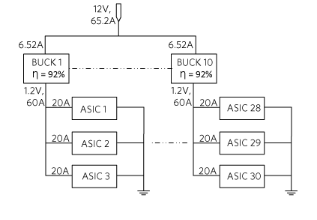

3404 加密貨幣和其他區(qū)塊鏈技術(shù)是計(jì)算密集型的。目前的區(qū)塊鏈采礦設(shè)備依賴于數(shù)百個(gè)專用ASIC,這些ASIC消耗千瓦的功率進(jìn)行計(jì)算。用于為ASIC供電的轉(zhuǎn)換器必須節(jié)省空間和功耗,以最大限度地提高密度并最大

2023-06-16 10:13:20 620

620

沒(méi)有關(guān)于 ASIC 確切含義的官方聲明,而且許多電子專業(yè)人士可能并不總是就 ASIC 到底是什么或特定組件是否應(yīng)歸類為 ASIC 達(dá)成一致。

2023-06-15 09:41:51 306

306

綜合工具的任務(wù)是將SoC設(shè)計(jì)映射到可用的FPGA資源中。自動(dòng)化程度越高,構(gòu)建基于FPGA的原型的過(guò)程就越容易、越快。

2023-06-13 09:27:06 277

277

您好,我正在嘗試將 Xee S2C 與 ESP8266-01 模塊一起使用。我將分別通過(guò) Xbee 和 ESP 的 TX RX 引腳將數(shù)據(jù)從我的 Xbee 直接發(fā)送到 ESP8266。我如何才能

2023-06-06 07:48:48

ASIC設(shè)計(jì)在尺寸和復(fù)雜性上不斷增加,現(xiàn)代FPGA的容量和性能的新進(jìn)展意味著這些設(shè)計(jì)中的2/3能夠使用單個(gè)FPGA進(jìn)行建模。然而,這些設(shè)計(jì)中仍然保留有1/3(那就是說(shuō),所有ASIC

2023-06-04 16:50:01 699

699 S32G2 聚四氟乙烯

S32G2是ip核還是外設(shè)?

如果是ip核,是否可以集成到其他SoC中?

謝謝

2023-06-02 08:04:53

思爾芯(S2C)近日宣布,公司的系統(tǒng)級(jí)驗(yàn)證原型驗(yàn)證解決方案獲得了較為全面的正向市場(chǎng)反饋,成功協(xié)助多家設(shè)計(jì)企業(yè)完成低功耗藍(lán)牙音頻(BLE Audio)領(lǐng)域的IP/藍(lán)牙SoC定制方案設(shè)計(jì)。

2023-05-30 15:52:52 401

401 在現(xiàn)代SoC芯片驗(yàn)證過(guò)程中,不可避免的都會(huì)使用FPGA原型驗(yàn)證,或許原型驗(yàn)證一詞對(duì)你而言非常新鮮,但是FPGA上板驗(yàn)證應(yīng)該是非常熟悉的場(chǎng)景了。

2023-05-30 15:04:06 905

905

我們當(dāng)然希望在項(xiàng)目中盡快準(zhǔn)備好基于FPGA原型驗(yàn)證的代碼,以便最大限度地為軟件團(tuán)隊(duì)和RTL驗(yàn)證人員帶來(lái)更客觀的收益。

2023-05-30 11:10:27 769

769

以標(biāo)記2^8 = 256個(gè)存儲(chǔ)單元,若每個(gè)存儲(chǔ)單元的字長(zhǎng)為8 bit,則最大可以接入系統(tǒng)的存儲(chǔ)空間為256kB。

4) 控制總線:用來(lái)傳送自CPU發(fā)出的控制信息或外設(shè)送到CPU的狀態(tài)信息,雙向通信

2023-05-26 17:07:52

請(qǐng)問(wèn)使用eMMC時(shí), HPM6750支持的最大容量 和速率是多少? 謝謝!

2023-05-26 08:12:55

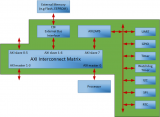

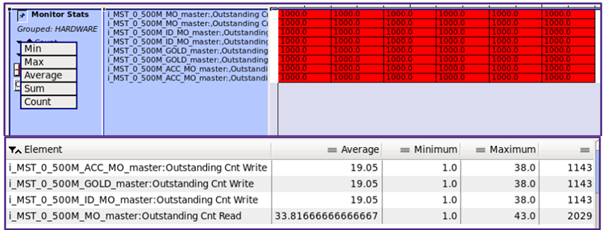

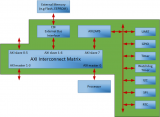

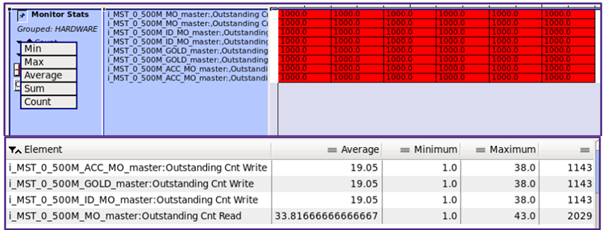

在使用 AXI 總線移動(dòng)大量數(shù)據(jù)的 SoC 中,AXI 總線的性能可能會(huì)成為整體系統(tǒng)性能的瓶頸。SoC 中日益增加的復(fù)雜性和軟件內(nèi)容,因此需要使用實(shí)際數(shù)據(jù)有效載荷在硅前進(jìn)行左移性能驗(yàn)證。硬件輔助驗(yàn)證

2023-05-25 15:37:52 543

543

多片F(xiàn)PGA的原型驗(yàn)證系統(tǒng)的性能和容量通常受到FPGA間連接的限制。FPGA中有大量的資源,但I(xiàn)O引腳的數(shù)量受封裝技術(shù)的限制,通常只有1000個(gè)左右的用戶IO引腳。

2023-05-23 17:12:35 1149

1149

FPGA原型驗(yàn)證系統(tǒng)要盡可能多的復(fù)用SoC相關(guān)的模塊,這樣才是復(fù)刻SoC原型的意義所在。

2023-05-23 16:50:34 381

381

如果SoC設(shè)計(jì)規(guī)模小,在單個(gè)FPGA內(nèi)可以容納,那么只要系統(tǒng)中的FPGA具有所SoC所設(shè)計(jì)需要時(shí)鐘的數(shù)量

2023-05-23 15:46:24 481

481

當(dāng)SoC的規(guī)模在一片F(xiàn)PGA中裝不下的時(shí)候,我們通常選擇多片F(xiàn)PGA原型驗(yàn)證的平臺(tái)來(lái)承載整個(gè)SoC系統(tǒng)。

2023-05-23 15:31:10 319

319 儲(chǔ)能系統(tǒng)應(yīng)盡量避免對(duì)用戶基本電費(fèi)的影響,這是指儲(chǔ)能系統(tǒng)在充電時(shí),實(shí)際上相當(dāng)于負(fù)荷,而原有負(fù)荷也正在運(yùn)行工作。對(duì)于整個(gè)系統(tǒng),相當(dāng)于用戶負(fù)荷增加了,如果造成了用戶的最大負(fù)荷變大,那么就需要考慮用戶與供電公司的契約容量的增加,

2023-05-11 16:49:35 5195

5195 FPGA原型在數(shù)字芯片設(shè)計(jì)中非常重要,因?yàn)橄啾扔梅抡嫫鳎蛘呒铀倨鞯葋?lái)跑仿真,F(xiàn)PGA的運(yùn)行速度,更接近真實(shí)芯片,可以配合軟件開(kāi)發(fā)者來(lái)進(jìn)行底層軟件的開(kāi)發(fā)。這一流片前的軟硬件的協(xié)同開(kāi)發(fā),是其最不可替代的地方。

2023-05-10 10:44:00 4775

4775

當(dāng)SoC的規(guī)模在一片F(xiàn)PGA中裝不下的時(shí)候,我們通常選擇多片F(xiàn)PGA原型驗(yàn)證的平臺(tái)來(lái)承載整個(gè)SoC系統(tǒng)。

2023-05-10 10:15:16 187

187 多片F(xiàn)PGA原型驗(yàn)證系統(tǒng)的拓?fù)溥B接方式各不相同,理想的多片F(xiàn)PGA原型驗(yàn)證系統(tǒng)應(yīng)該可以靈活配置,可以使用其相應(yīng)的EDA工具

2023-05-08 11:51:40 326

326

思爾芯(S2C)近日宣布,公司的系統(tǒng)級(jí)驗(yàn)證原型驗(yàn)證解決方案獲得了較為全面的正向市場(chǎng)反饋,成功協(xié)助多家設(shè)計(jì)企業(yè)完成低功耗藍(lán)牙音頻(BLEAudio)領(lǐng)域的IP/藍(lán)牙SoC定制方案設(shè)計(jì)。萬(wàn)物互聯(lián)時(shí)代開(kāi)啟

2023-05-08 09:29:37 274

274

這是另一個(gè)應(yīng)該是微不足道的問(wèn)題,但可能會(huì)變成一個(gè)為期一周的任務(wù),就像 S32G2 中的其他問(wèn)題一樣:如何[i]啟用 A53 的系統(tǒng)計(jì)數(shù)器?這是一個(gè)關(guān)鍵的 64 位時(shí)鐘,由 S32G2 分配給所有四個(gè)

2023-05-05 13:43:10

在進(jìn)行FPGA原型驗(yàn)證的過(guò)程中,當(dāng)要把大型的SoC進(jìn)行FPGA原型驗(yàn)證時(shí),有時(shí)候會(huì)遇到一種情況,同樣的接口分兩組出去到不同的模塊,而這兩個(gè)模塊規(guī)模較大,又需要分割在兩片F(xiàn)PGA中,這時(shí)候就會(huì)像下圖一樣。

2023-05-04 16:21:34 426

426

當(dāng)電池組中的每個(gè)電池都具有相同的充電狀態(tài) (SoC) 時(shí),電池組中的電池單元將保持平衡。SoC 是指單個(gè)電池在充電和放電時(shí)相對(duì)于其最大容量的當(dāng)前剩余容量。例如,剩余容量為 10 A/小時(shí)

2023-05-01 14:22:00 650

650

對(duì)SoC芯片要進(jìn)行FPGA原型驗(yàn)證,假如設(shè)計(jì)較大,要將SoC中不同功能模塊或者邏輯模塊分別分配到特定的FPGA,那么對(duì)SoC的分割策略尤為重要

2023-04-27 15:17:06 627

627

盡管對(duì)于工程師而言目標(biāo)始終是以原始形式對(duì)SoC源RTL進(jìn)行原型化,但在原型化工作的早期,SoC設(shè)計(jì)必須進(jìn)行必要的修改,以適應(yīng)FPGA原型系統(tǒng)。

2023-04-26 09:48:13 747

747 在進(jìn)行FPGA原型驗(yàn)證的過(guò)程中,當(dāng)要把大型的SoC進(jìn)行FPGA原型驗(yàn)證時(shí),有時(shí)候會(huì)遇到一種情況,同樣的接口分兩組出去到不同的模塊,而這兩個(gè)模塊規(guī)模較大,又需要分割在兩片F(xiàn)PGA中,這時(shí)候就會(huì)像下圖一樣:

2023-04-25 11:15:20 1629

1629

先生關(guān)于S32K312 DCMDEB寄存器中APPDBG_STAT_SOC位的具體含義

2023-04-21 06:02:25

51單片機(jī)外擴(kuò)數(shù)據(jù)存儲(chǔ)器最大的容量是多少?可以達(dá)到50MB嗎?用的是什么芯片?

2023-04-19 16:34:36

FPGA原型驗(yàn)證系統(tǒng)要盡可能多的復(fù)用SoC相關(guān)的模塊,這樣才是復(fù)刻SoC原型的意義所在。

2023-04-19 09:08:15 848

848 儲(chǔ)能系統(tǒng)的儲(chǔ)能容量與最大輸出功率的比值就是持續(xù)時(shí)間,以小時(shí)為單位——這是儲(chǔ)能系統(tǒng)從充滿電開(kāi)始提供最大功率的時(shí)間長(zhǎng)度。目前大多數(shù)部署的電池儲(chǔ)能的持續(xù)時(shí)間為4小時(shí)或更短。

2023-04-10 15:28:47 20128

20128 FPGA原型設(shè)計(jì)是一種成熟的技術(shù),用于通過(guò)將RTL移植到現(xiàn)場(chǎng)可編程門陣列(FPGA)來(lái)驗(yàn)證專門應(yīng)用的集成電路(ASIC),專用標(biāo)準(zhǔn)產(chǎn)品(ASSP)和片上系統(tǒng)(SoC)的功能和性能。

2023-04-10 09:23:29 947

947 如果SoC設(shè)計(jì)規(guī)模小,在單個(gè)FPGA內(nèi)可以容納,那么只要系統(tǒng)中的FPGA具有所SoC所設(shè)計(jì)需要時(shí)鐘的數(shù)量

2023-04-07 09:42:57 594

594 當(dāng)SoC系統(tǒng)的規(guī)模很大的時(shí)候,單片F(xiàn)PGA驗(yàn)證平臺(tái)已經(jīng)無(wú)法容納這么多容量,我們將采取將SoC設(shè)計(jì)劃分為多個(gè)FPGA的映射。

2023-04-06 11:20:48 602

602 SOC是在同一塊芯片中集成了CPU、各種存儲(chǔ)器、總線系統(tǒng)、專用模塊以及多種I/O接口的系統(tǒng)級(jí)超大規(guī)模集成電路。ASIC是專用于某一方面的芯片,與SOC芯片相比較為簡(jiǎn)單。

2023-04-03 16:04:16 4038

4038 FPGA原型驗(yàn)證在數(shù)字SoC系統(tǒng)項(xiàng)目當(dāng)中已經(jīng)非常普遍且非常重要,但對(duì)于一個(gè)SoC的項(xiàng)目而言,選擇合適的FPGA原型驗(yàn)證系統(tǒng)顯的格外重要

2023-04-03 09:46:45 924

924 在集成電路界ASIC被認(rèn)為是一種為專門目的而設(shè)計(jì)的集成電路,是指應(yīng)特定用戶要求和特定電子系統(tǒng)的需要而設(shè)計(jì)、制造的集成電路。ASIC的特點(diǎn)是面向特定用戶的需求,ASIC在批量生產(chǎn)時(shí)與通用集成電路相比具有體積更小、功耗更低、可靠性提高、性能提高、保密性增強(qiáng)、成本降低等優(yōu)點(diǎn)。

2023-03-31 14:36:04 1717

1717 BOARD BATTERY FOR SOC'S

2023-03-29 19:51:22

我們當(dāng)然希望在項(xiàng)目中盡快準(zhǔn)備好基于FPGA原型驗(yàn)證的代碼,以便最大限度地為軟件團(tuán)隊(duì)和RTL驗(yàn)證人員帶來(lái)更客觀的收益。

2023-03-28 14:11:15 768

768 DK-SOC-10AS066S-A

2023-03-28 13:19:47

和系統(tǒng)接口著手,那也是白白浪費(fèi)時(shí)間。原型驗(yàn)證的一大優(yōu)勢(shì)就是盡早地從系統(tǒng)和集成的角度,以硬件原型著手進(jìn)行軟件與嵌入式的開(kāi)發(fā)。而于此同時(shí)后端以及流片的ASIC研發(fā)時(shí)間可以同步進(jìn)行。 但和RTL

2023-03-28 11:14:04

”。超級(jí)電容實(shí)物圖二、為什么超級(jí)電容的容量能夠這么大?首先搞明白電容容量是由什么決定?電容中儲(chǔ)存的電能來(lái)源于兩塊極板上積累的電荷,電容容量的大小與兩極板的正對(duì)面積和距離有關(guān)。計(jì)算電容容量的公式為:C

2023-03-28 10:21:44

在現(xiàn)代SoC芯片驗(yàn)證過(guò)程中,不可避免的都會(huì)使用FPGA原型驗(yàn)證,或許原型驗(yàn)證一詞對(duì)你而言非常新鮮,但是FPGA上板驗(yàn)證應(yīng)該是非常熟悉的場(chǎng)景了。

2023-03-28 09:33:16 854

854 、S32K144EVB-Q100和S32K142EVB-Q100有什么區(qū)別嗎,我查了兩塊板子的datasheet,兩塊板子的特性沒(méi)有區(qū)別。(只有芯片)2. 我可以通過(guò) MC33771C/772C 評(píng)估 GUI 下載 S32K142EVB-Q100 的 SREC 3. FRDM33771CSPEVB 是否有示例代碼?

2023-03-27 06:52:10

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論