保護等功能。當檢測到異常情況時,芯片會關閉開關管,以防止損壞。

H6392升壓恒壓DC3.7V升5V 3.7V升9V 3.7V升12V電源芯片

產品描述

H6392是一款外圍簡單的電流模式升壓

2024-03-12 10:04:27

顏色識別出現這種樣的左右邊框可能是什么原因?我感覺代碼好像沒有問題上下邊界能畫出來左右邊界就畫不出來

2024-03-08 17:29:05

ADMV4530BCCZADMV4530BCCZ 特性RF 輸出頻率范圍:27 GHz 至 31 GHz兩種升頻轉換模式從差分基帶 I/Q 直接進行升頻轉換(I/Q 模式)單上邊帶升頻轉換

2024-02-28 20:35:35

邊界矢量數據是一種用于描述地理空間邊界的格式。它包含了一系列的數據點,這些點按照一定的順序連接起來,形成了一條封閉的線,來表示地理區域的邊界。 邊界矢量數據通常以矢量文件的形式存在,矢量文件是由許多

2024-02-25 15:16:57 206

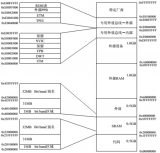

206 。時鐘發生器芯片廠家可輸出差分100MHz,125MHz,156.25MHz和單端33.33MHz CPU時鐘,同時輸出6路25MHz緩沖參考時鐘。? 主要特性l 7路單

2024-02-04 11:41:14

芯片為什么要時鐘信號 時鐘芯片的作用是什么? 時鐘信號在芯片中起著非常重要的作用。它是芯片的“心臟”,相當于人體的心臟,用于同步和控制芯片中的各個功能模塊之間的操作。時鐘信號可以提供一個穩定的時間

2024-01-29 18:11:31 621

621 時鐘Buffer芯片是什么?其作用是啥?它被用在什么地方? 時鐘Buffer芯片是一種用于管理和增強電子設備中的時鐘信號的集成電路。時鐘信號在數字電子設備中非常重要,它用于同步各個模塊的工作,確保

2024-01-16 15:10:16 810

810 時鐘芯片是一種微型電子器件,其作用是在電子設備中提供精確的時間基準。它能夠產生穩定的電子脈沖,用于同步和控制設備中的各種操作和功能。

2024-01-11 18:20:03 640

640 時鐘芯片是一種集成電路,用于產生和控制電子產品的時鐘信號。它是電子產品中的關鍵部件,用來確保各個組件和子系統之間的同步和順序操作。時鐘芯片的原理是利用晶體振蕩器產生穩定的頻率信號,并通過分頻和倍頻

2024-01-10 14:16:47

描述:AT32F403A引腳比較緊張,XMC(類似于STM32 FSMC)只支持復用模式,就是A0-A15和D0-D15都用一個引腳,如果要用,只能用鎖存器將地址鎖存,實現地址線和數據線的分離,目前

2024-01-04 10:46:19

高精度時鐘同步芯片高精度時鐘芯片典型應用場景:·核心網路由器、交換機·同步以太網設備·電信級邊界時鐘(T-BCS)和從時鐘設備(TimeSlave)·高速以太網端口設備·時鐘時間源設備BITS、時間

2023-12-29 09:37:02

。時鐘發生器芯片廠家可輸出差分100MHz,125MHz,156.25MHz和單端33.33MHz CPU時鐘,同時輸出6路25MHz緩沖參考時鐘。? 主要特性l 7路單

2023-12-29 09:29:50

請問在使用16488A時,通過DIO4引入外部時鐘,時鐘頻率為100Hz,會對最終傳感器的輸出有什么影響?對數據就緒信號DRY有什么影響呢?

手冊中看到了可能會造成角度變化的寄存器值溢出,但我用不到這個量。謝謝了!

2023-12-29 06:19:30

100MHz,125MHz,156.25MHz和單端33.33MHz CPU時鐘,同時輸出6路25MHz緩沖參考時鐘。時鐘緩沖器芯片? 主要特性l 7路單端LVCM

2023-12-28 13:46:09

最近在使用AD9640進行硬件設計

差分時鐘部分:

疑問1:datasheet在差分時鐘部分提供的參數芯片是95xx系列,這些芯片是不是對輸入的時鐘信號質量要求也很高?在時鐘次系列芯片的時候需要

2023-12-22 08:19:31

問題1:AD9705在只使用單端時鐘時,14引腳CLKCOM是否需要接地,數據手冊中只說明單端時鐘應用時需要將15引腳和14引腳連接;

問題2:請幫忙查看一下在PIN模式下外圍電路是否有錯誤。

2023-12-20 06:15:02

我想用AD9235-65芯片,我的輸入信號頻率50K左右,輸入信號經過濾波后,離AD9235的距離很近,是不是就不需要單端轉差分輸入了?我的信號本來是單端的。或者更進一步,在什么情況下才需要單端轉差分信號?謝謝!

2023-12-14 07:57:13

AD7790數據手冊15頁中單次轉換模式中描述”AD7790上電,執行單次轉換,然后返回關斷模式。轉換需要的時間長度為2*tADC。”這里更新速率采用16.6Hz,正常工作模式不分頻單次轉換的時間

2023-12-11 06:39:28

的問題。所以我就直接用信號發生器,按照單端1.8 V CMOS輸入時鐘的接法,輸入了一個40Mhz的正弦波。但是還是同樣的現象。

有沒有人能幫我看看是不是硬件上哪里接錯了,還是我的引腳配置有問題。

這個是芯片的原理圖:

這是我的測試程序:

2023-12-08 07:14:56

大家好!最近在用AD7768-4采集數據,用的引腳控制,當配置在單次轉換模式的時候,SYNC_IN腳由單片機提供周期信號,然后DOUT和DRDY腳沒有輸出,DCLK腳有時鐘信號輸出。請問大家在用單次模式的時候是怎么配置的,有哪些注意事項?非常感謝了!

2023-12-07 07:20:38

您好,我利用NXP K10芯片(M4內核)硬件SPI 從機模式與AD7779 主機模式進行通訊讀取AD7779 DOUT模式下第0,1兩個通道的數據。

AD7779配置為:dclk: 1米 抽取率

2023-12-07 06:30:31

今天想來聊一聊芯片設計中的一個非常基礎的概念——時鐘。對于外行來說聽到這個詞可能會感覺迷茫,猜一個大概意思吧可能也不太準。

2023-12-06 14:41:00 303

303 近期在使用AD9162時,配置的模式不成功,測試時鐘CLK發現,CLK±單端信號共模電壓接近0V,手冊上是0.6V,但測試9162-FMC-EZB參考板上的CLK也是共模電壓為0V,請問這個會有什么影響嗎?

我們現在測試配置JESD204B接口模式不正確,不確定是否CLK的影響?

2023-12-05 06:14:24

將詳細介紹Zookeeper引入的機制,包括分布式數據結構、ZAB協議、事務處理、選舉算法、觀察機制以及ACL安全機制。 分布式數據結構: Zookeeper引入了一些分布式數據結構來支持分布式系統的協調和管理。其中最重要的是Zookeeper的核心數據結構ZooKeeper數據樹(Z

2023-12-03 16:38:11 518

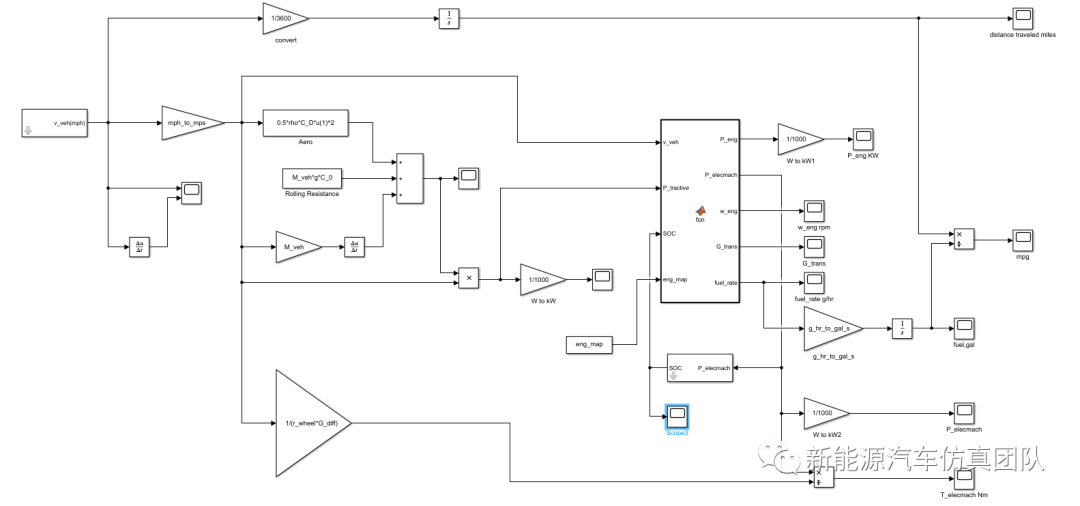

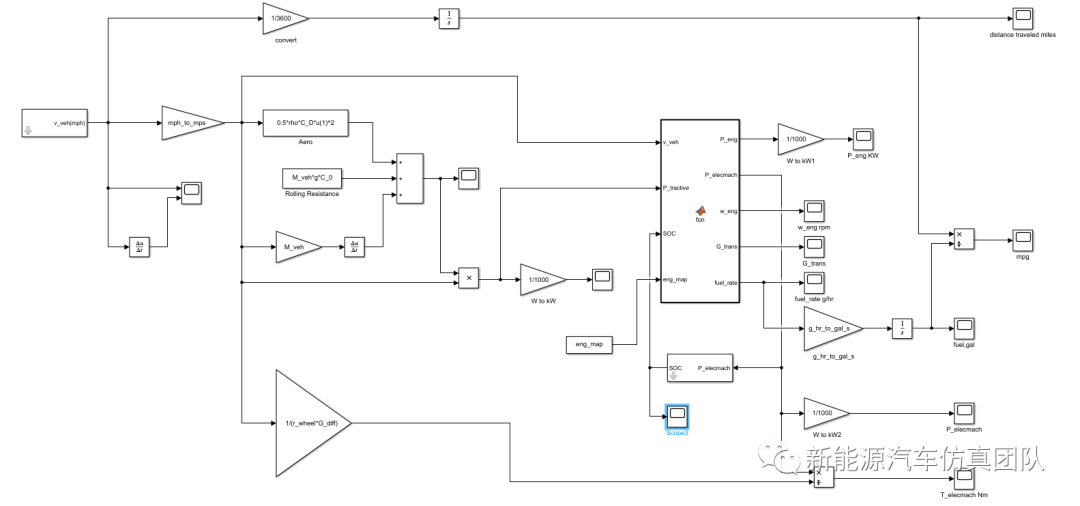

518 寶馬530e 車型和寶馬550e xDrive車型采用了最新的寶馬eDrive電驅系統,其中專門為混合動力車型驅動系統開發的電機與其功率元器件被集成到8速Steptronic Sport運動型手自一體變速器中

2023-11-30 16:38:48 360

360 為了像51單片機一樣能夠對某個管腳單獨操作,引入了位帶操作這樣的操作機制。

2023-11-29 14:36:00 389

389

6-8.4V升9V 12V升24V 1A-2A內置MOS升壓芯片DC-DC內置MOS管升壓芯片是將較低的電壓轉換為較高的電壓的電子元件,通常用于電源電路中。其中,6-8.4V升9V、12V升24V

2023-11-27 20:21:48

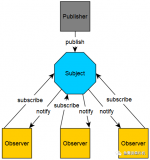

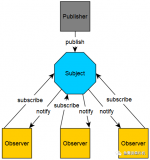

nRF5 SDK從版本14開始,對事件回調機制做了更新,引入了觀察者模式,以解耦不同BLE Layer對BLE事件的回調函數。

2023-11-27 10:07:17 258

258

一、引言在電子工程中,B628是一款經典的升壓芯片,廣泛應用于各種電源管理系統中。本文將對B628升壓芯片的參數進行詳細解析,幫助讀者更好地理解和應用這款芯片。二、B628升壓芯片的主要參數1.

2023-11-24 23:56:43

人工智能涵蓋了從訓練算法到推理的方方面面。它包括大量的訓練計劃,以及可以適應微型物聯網設備的tinyML算法。此外,它越來越多地用于芯片設計的許多方面,以及在晶圓廠中,以關聯來自這些芯片的制造、檢查、計量和測試的數據。它甚至在現場用于識別故障模式,這些模式可以反饋到未來的設計和制造過程中。

2023-11-23 15:27:25 116

116

華芯微特SWM166D8U6 是一顆主要應用于屏幕驅動的32位MCU,內嵌 ARM? Cortex?-M0 內核,憑借其出色的性能以及高可靠性、低功耗、代碼密度大等突出特點,可應用于工業控制、電機

2023-11-20 16:52:25

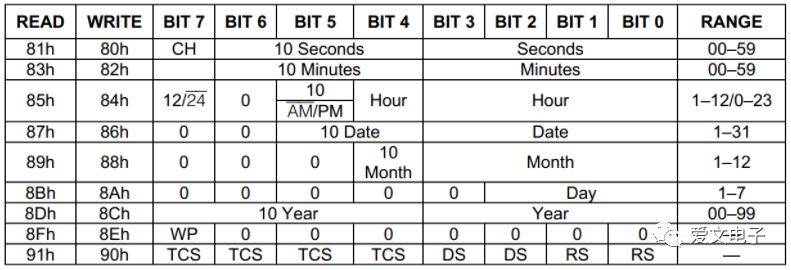

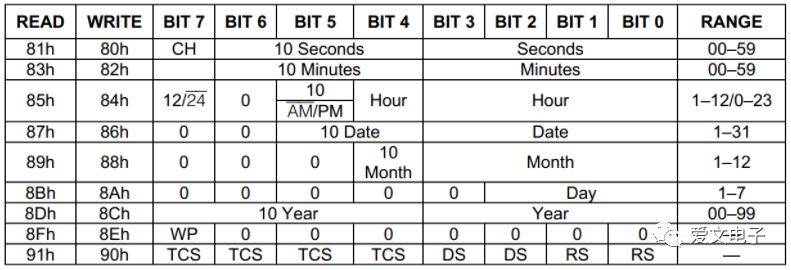

DS1302時鐘芯片內部的時鐘電路原理是基于晶振的振蕩原理。晶振是一種利用晶體的共振特性產生穩定的振蕩信號的元件。在DS1302中,晶振的頻率為32.768kHz,這是一個非常穩定的頻率,適合用于實時時鐘應用。

2023-11-18 09:40:41 893

893 DS1302時鐘芯片是一種實時時鐘芯片,采用三線串行接口與微處理器相連,可以提供年、月、日、時、分、秒等時間信息。

2023-11-18 09:39:40 1187

1187 現在要為da芯片提供1000M的轉換時鐘信號,原始信號是單端的,但DA芯片是差分輸入,所以要加一個單端轉差分的差分放大器。問下這個芯片怎么選啊,是不是只要帶寬大于1000M就可以了,LMH6552芯片可以嗎?

2023-11-17 16:18:09

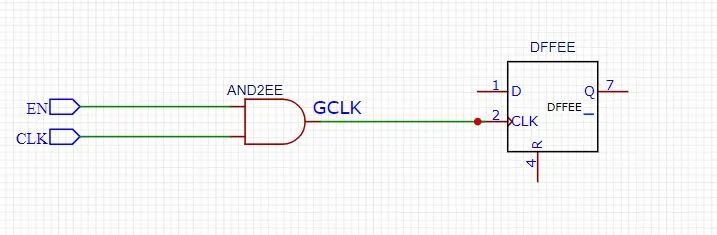

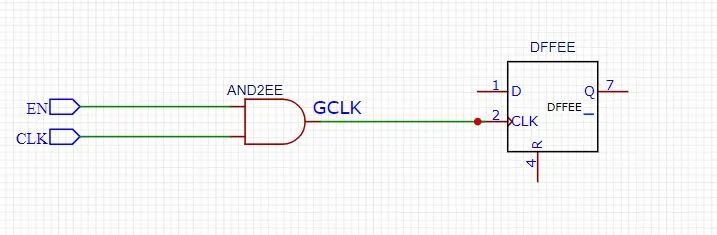

高密度數字CMOS工藝提供的低晶圓成本使其成為混合信號ASIC的首選,特別是對于片上系統設計。能夠在對芯片面積影響最小的情況下添加大量亞微米邏輯門,這意味著時鐘邏輯覆蓋了典型混合信號內核不斷增加

2023-11-10 15:41:32 188

188 小規模測試來提供的。這種方法不需要大型實驗室設施;然而,它在試樣中引入了理想化的應力和應變狀態,因此沒有考慮復雜應力狀態下的材料行為以及整個結構中不同材料與接頭、軸承和其他關鍵細節之間的相互作用

2023-11-06 19:34:14

、高可靠性等特點。但嵌入式Flash的邊界主要包括以下幾個方面。 首先,嵌入式Flash的物理存儲空間是有限的,這個邊界可以根據存儲芯片的型號和容量來確定。通常,嵌入式Flash的存儲容量不如普通閃存存儲器,一般在數百兆到幾個G之間,因此需要謹

2023-10-29 17:29:44 250

250 AT32F系列單周期模式演示AT32F系列TMR單周期模式的使用方法。

2023-10-27 06:58:38

AT32F4xx SPI使用單工模式通訊演示AT32F403Axx SPI使用單工模式通訊,其余系列使用方式與此類似。

2023-10-27 06:14:26

FPGA為什么有時候還需要一個時鐘配置芯片提供時鐘呢? FPGA(Field Programmable Gate Array)是一種可編程邏輯器件,可以根據不同需要編程,實現不同的功能。在FPGA

2023-10-25 15:14:20 1037

1037 芯片的操作。如果芯片時鐘不穩定,設備可能會出現各種問題,甚至在某些情況下,芯片可能根本無法正常工作。在本文中,我們將探討芯片時鐘不穩定的原因以及其影響。 芯片內部時鐘紊亂的原因 芯片內部時鐘可能會出現不穩定的原

2023-10-25 15:07:59 1145

1145 什么是時鐘芯片?時鐘芯片的工作原理 時鐘芯片的作用 時鐘芯片是一種用于計算機或其他電子設備中的集成電路,它提供精準的時鐘信號。時鐘信號是計算機進行各種操作的基礎,比如數據傳輸、運算等等,所以時鐘芯片

2023-10-25 15:02:33 2309

2309 AT32定時器外部時鐘模式B+掛起模式本示例代碼基于AT32F403A,展示了如何使用AT32 的外部時鐘模式B和掛起模式。

2023-10-19 06:20:13

請問下各位大佬,凌力爾特LTC4020芯片CSOUT無輸出是什么原因,能充電,且CSP/CSN有差值,之前出現過小電流充電,后來確認受到干擾,增加電容濾波后能大電流充電。

2023-10-08 11:42:45

在芯片設計中,時鐘作為一種關鍵元素,發揮著重要作用。

2023-10-07 16:44:29 1099

1099 時鐘芯片的應用非常廣泛,例如時鐘電路、數據傳輸和同步,以及計算機、手機和手表等很多電子設備。對這些設備日益增長的需求,推動了時鐘芯片市場的增長,預計到2026年,市場規模將增長至約115億美元。

2023-09-28 14:27:58 1598

1598

一般均內置了可編程的實時日歷時鐘,用于設定以及保存時間。其采用備份電池供電,在系統斷電時仍可以工作,因此時間值不會丟失。另外,實時時鐘芯片一般內置閏年補償系統,計時很準確。實時時鐘芯片的這些優點,使得其

2023-09-26 08:27:51

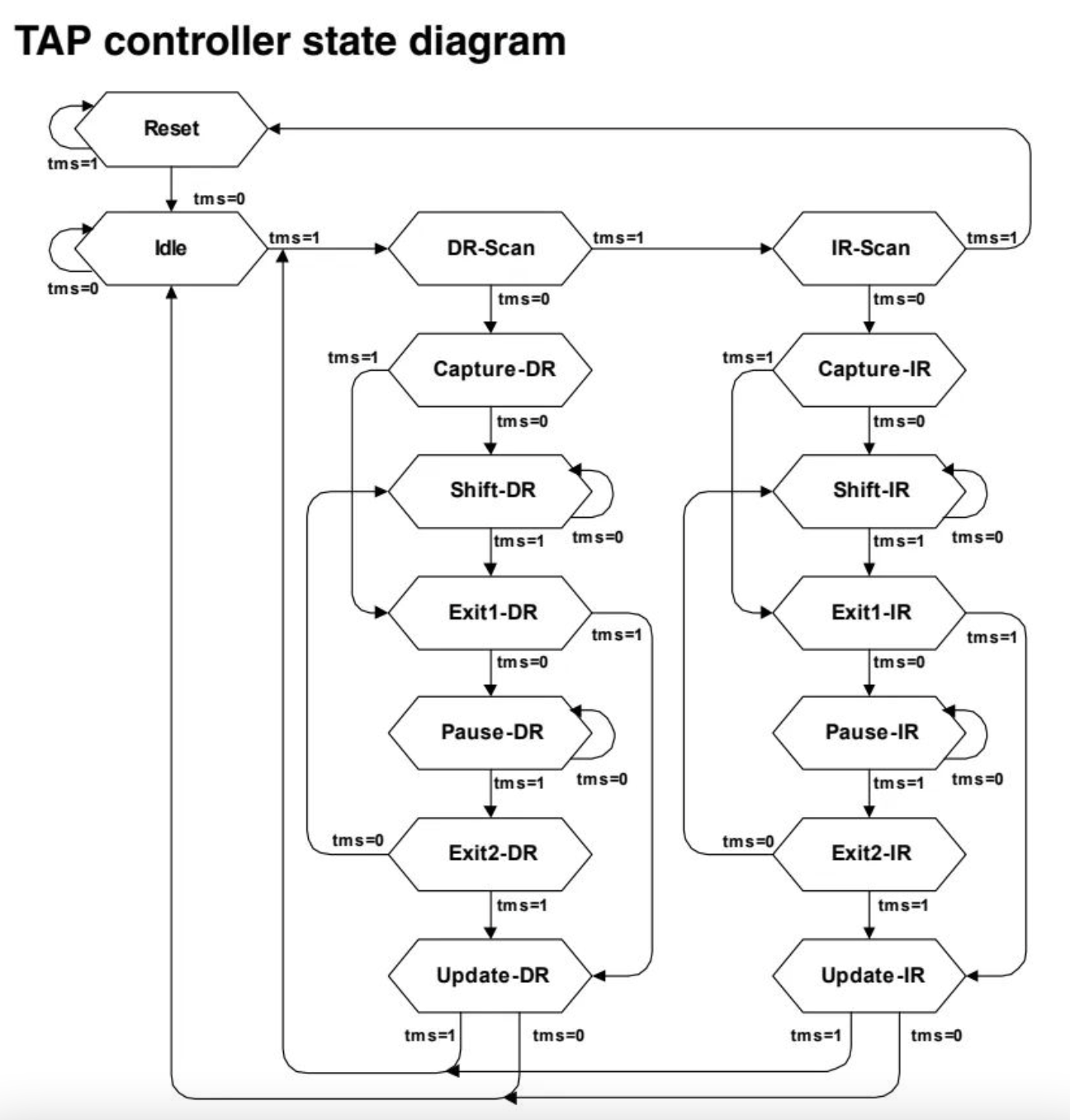

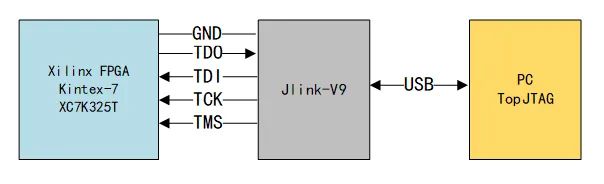

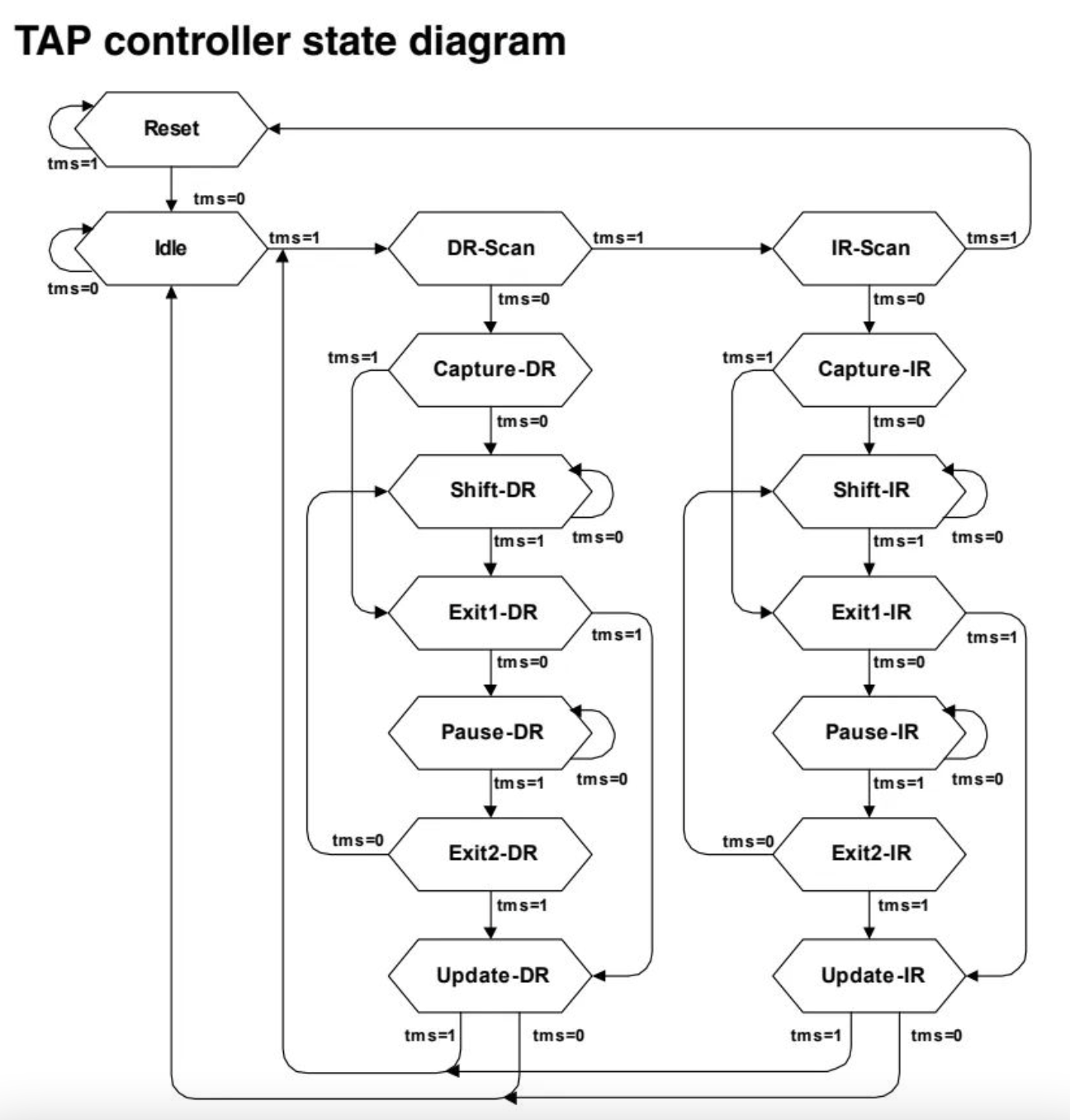

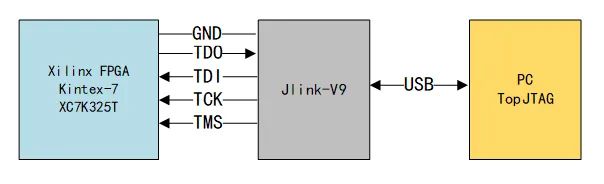

提到邊界掃描,就不得不提JTAG,因為邊界掃描是JTAG接口的功能之一。

2023-09-22 14:12:17 1495

1495

EG1252是一款高性價比電流模式PWM控制器,適合于中、大等功率反激電源方案以及正激電源方案。EG1252內置抖頻功能,具有優良的EMI特性。芯片采用綠色節能模式和打嗝模式控制輕負載和零負載

2023-09-20 17:35:21 1360

1360

中,我們將詳細介紹時鐘芯片和晶振的區別以及它們在電子設備中的作用和應用。 一、時鐘芯片和晶振的定義 時鐘芯片是一種集成電路,它能夠在電子設備中生成準確的時間信號,可以用來控制電子設備中各個組件的運作時間。它通常

2023-09-15 16:28:20 2859

2859 芯片為什么需要時鐘信號? 在我們日常生活中,我們所使用的各種電子設備都需要一個時鐘信號來進行計時和同步,例如:手機、電腦、電視、汽車、機器人、智能家居等設備都需要時鐘信號。對于各種這些電子設備

2023-09-15 16:28:14 1366

1366 本文主要介紹Xilinx FPGA的GTx的參考時鐘。下面就從參考時鐘的模式、參考時鐘的選擇等方面進行介紹。

2023-09-15 09:14:26 1941

1941

上一篇文章,介紹了基于STM32F103的JTAG邊界掃描應用,演示了TopJTAG Probe軟件的應用,以及邊界掃描的基本功能。本文介紹基于Xilinx FPGA的邊界掃描應用,兩者幾乎是一樣。

2023-09-13 12:29:37 654

654

前面兩篇文章介紹了邊界掃描的基本原理和BSDL文件,本文文章介紹邊界掃描測試實際使用的兩款軟件工具,在后面的實戰應用部分,會演示基于STM32和FPGA的邊界掃描測試應用。

2023-09-11 14:34:56 1278

1278

景下的時序要求。尤其對于需要高速數據傳輸、信號采集處理等場景的數字信號處理系統而言,FPGA PLL的應用更是至關重要。本文將介紹FPGA鎖相環PLL的基本原理、設計流程、常見問題及解決方法,以及該技術在外圍芯片時鐘提供方面的應用實例。 一、FPGA鎖相環PLL基本原理 1.時鐘頻率的調

2023-09-02 15:12:34 1319

1319 芯片為什么要時鐘信號 芯片是現代電子設備的核心組成部分,廣泛應用于計算機、手機、電視等各個領域。芯片內部有著復雜的電子元件和電路結構,這些元件和電路結構需要進行同步操作,以實現正確的工作。因此,芯片

2023-09-01 15:38:11 1374

1374 本篇將詳細介紹如何使用RA6T2 16位ADC在混合模式(Hybrid mode)下應用采樣保持功能進行AD采樣,以及后臺功能(background)的具體應用。本篇使用FSP建立應用工程,詳細講解

2023-09-01 12:24:01 493

493

如果差分對做單端時鐘輸出,如P端作為時鐘輸出,另一端應該如何使用。

2023-08-11 07:26:13

,

程序重啟初始化后,自動又進入了中斷,經過Debug調試推測是,再由外部中斷喚醒的時候定時器掃描又識別了按鍵按下,又一次進入了STOP模式,那么問題了來,我明明已經關閉了時鐘,關閉了定時器,為什么還能

2023-08-05 07:50:57

在 SPI 中,主機可以選擇時鐘極性和時鐘相位。在空閑狀態期間,CPOL 為設置時鐘信號的極性。空閑狀態是指傳輸開始時 CS 為高電平且在向低電平轉變的期間,以及傳輸結束時 CS 為低電平

2023-07-21 10:08:55 2920

2920

混合器芯片是一種常見的電子元件,用于將不同頻率的信號進行混合或分離。在電子設備維修或研發過程中,了解混合器芯片的型號是非常重要的。本文將介紹幾種常見的方法,幫助您查看混合器芯片的型號。

2023-07-20 09:47:54 292

292 我覺得稱時鐘樹為芯片的大動脈一點也不夸張,因為所有flipflop 翻轉都要受到它的控制。而時鐘樹的設計到實現是一個很復雜的過程,從流程上說,它牽扯到使用的工具,流程,flow等。從人的角度

2023-07-15 09:28:09 2709

2709

“以芯格物,立諾微行”。隨著創新能力和研發能力的不斷提高,在國內高性能數模混合信號芯片領域中,芯格諾將以其產品特點、團隊建設以及技術優勢等差異化特性在以始為終的強大信念下占據一席之位。

2023-07-11 13:37:39 373

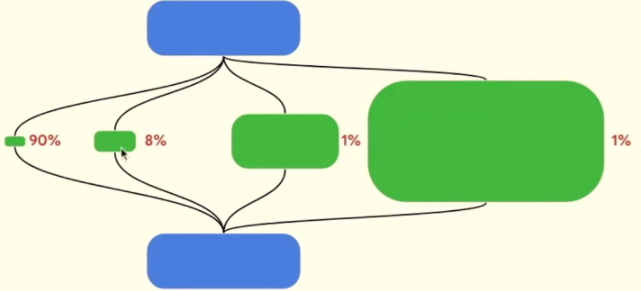

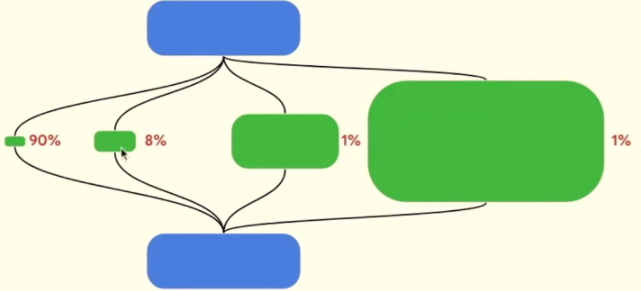

373 芯片功耗組成中,有高達40%甚至更多是由時鐘樹消耗掉的。這個結果的原因也很直觀,因為這些時鐘樹在系統中具有最高的切換頻率,而且有很多時鐘buffer,而且為了最小化時鐘延時,它們通常具有很高的驅動強度。

2023-06-29 15:33:18 1510

1510

并聯混合動力汽車的工作模式可以分為六種。純電動模式、純發動機模式、混合驅動模式、充電模式、再生制動模式、怠速停車模式。

2023-06-28 11:21:27 789

789

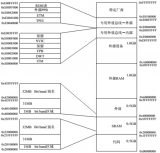

,內嵌512KB FLASH 128KB ROM以及138KB SRAM,以串口為燒錄接口。外國電路簡單,射頻電路是內嵌在芯片里的,擁有前沿射頻電路的設計理念。

512KB系統Flash

128KB

2023-06-27 17:30:17

定時器控制器提供單周期模式、周期模式、雙態模式與連續計數模式,還提供由外部腳位來對事件計數功能,以及用來捕捉或重置定時器的輸入捕捉功能。

2023-06-26 08:05:00

現在打算使用新唐M451LG6AE芯片設計產品,因為在產品生產后需要經過ICT測試,ICT又需要使用芯片的邊界掃描功能。但是在手冊中沒有找到關于邊界掃描的描述,也不知道應該預留哪幾個引腳來支持邊界掃描。

2023-06-26 06:15:37

M261芯片如何進入睡眠和深度睡眠模式,以及如何退出來?有沒有C語言參考?

2023-06-20 07:19:33

電子發燒友網站提供《如何控制IoT ONE Nixie時鐘背光—開/關以及顏色和亮度.zip》資料免費下載

2023-06-14 14:26:27 0

0 DS1302是DALLAS公司推出的一款時鐘芯片,內部包括時鐘/日歷寄存器和31字節的數據暫存寄存器,數據通信只需要一根串行輸入輸出口。

2023-06-13 17:25:59 1376

1376

它有兩種操作模式:時鐘和設置。時鐘模式是標準模式,在此模式下,當前時間顯示在數碼管上。

2023-06-12 09:01:51 552

552

當為已安裝的桌面 Web 應用程序啟用無邊界模式之后,Web 應用的整個窗口會擴展到覆蓋整個瀏覽器 —— 包括瀏覽器的標題欄區域和窗口控制按鈕(關閉、最大化、最小化)。Web 應用程序開發人員負責整個窗口的繪制和輸入處理。

2023-06-05 16:04:42 318

318

,但它導致了目前價值數十億美元的FPGA產業。由于其重要性,XC2064被列入芯片名人堂。在這篇文章中,我們對Xilinx的XC2064進行了逆向工程,解釋了它的內部電路(上圖)以及 "比特流

2023-06-02 14:03:57

“在同步下一代電子產品方面,使用傳統時鐘架構的技術擴展遇到了瓶頸。Stathera的技術引入了一種集成和制造時鐘器件的新方法。”Stathera首席執行官(CEO)兼聯合創始人George Xereas表示,“我們很高興成為唯一一家擁有最先進DualMode頻率技術的公司

2023-05-22 15:17:25 506

506

1.基本介紹MS1861 單顆芯片集成了HDMI、LVDS 和數字視頻信號輸入; 輸出端可以驅動MIPI(DSI-2)、 LVDS 、Mini-LVDS 以及 TTL 類型 TFT-LCD

2023-05-20 11:51:15

SoC的頂層的約束適用于FPGA到其各自時鐘域中的各個Flip_Flop,如果定義了跨時鐘域,也適用于FPGA之間。當我們可以確保每個FPGA邊界都有一個IOFF,它與SoC中相應的元素對齊時,這一點對于性能而言非常重要。

2023-05-13 09:38:09 1352

1352

時鐘同步的組網

有了時鐘源,還需要一個網絡,把時鐘分發下去。根據組網的不同,可分為集中式和分布式這兩種方式。

集中式時鐘同步的代表為基于分組網絡的同步以太網(SyncE),1588v2等技術

2023-05-10 17:09:50

在Fluent分析中邊界條件的設定是非常重要的,可對Fluent中的邊界條件進行簡易分類為進出口邊界條件、壁面條件、內部單元邊界、內部表面邊界等;

2023-05-02 15:20:00 3167

3167

本章教程主要在SPI單工通信方式下進行1條時鐘線和1條單向數據線配置,并進行主機接收從機發送。 1、SPI簡介及相關函數介紹關于SPI單工通信模式下1條時鐘線和1條單向數據線配置介紹,在第46章已經

2023-04-25 16:50:41

本章教程主要在SPI單工通信方式下進行1條時鐘線和1條雙向數據線配置,并進行主機接收從機發送。 1、SPI簡介及相關函數介紹關于SPI單工通信模式下1條時鐘線和1條雙向數據線配置介紹,在第46章已經

2023-04-25 16:48:14

本章教程主要在SPI單工通信方式下進行1條時鐘線和1條雙向數據線配置,并進行主機發送從機接收。 1、SPI簡介及相關函數介紹SPI支持以三線同步串行模式進行數據交互,加上片選線支持硬件切換主從模式

2023-04-25 16:47:06

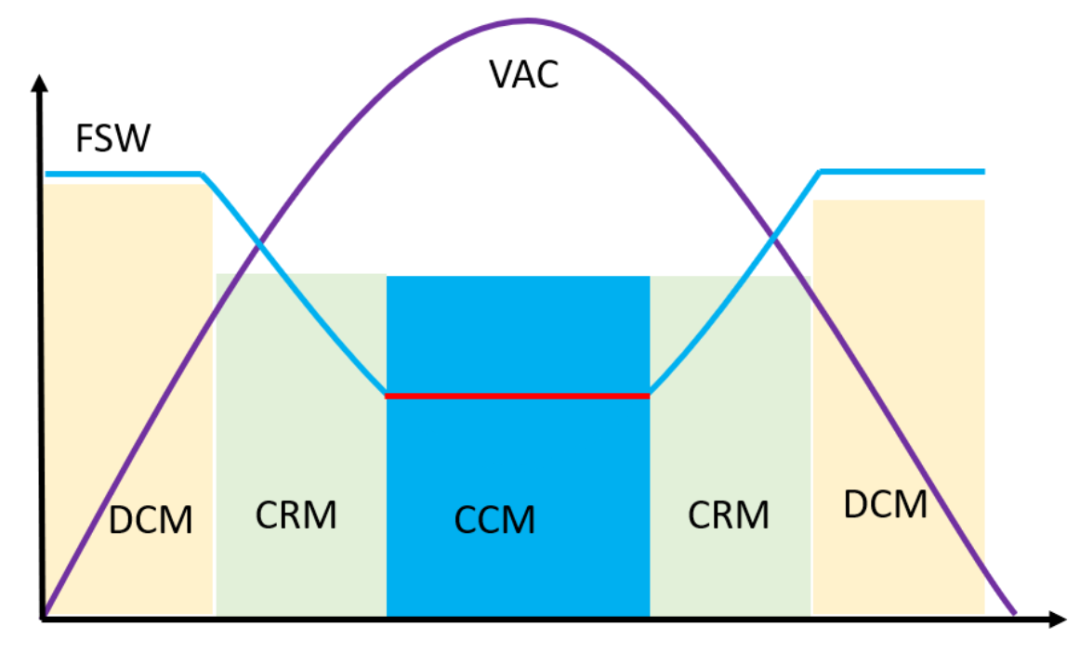

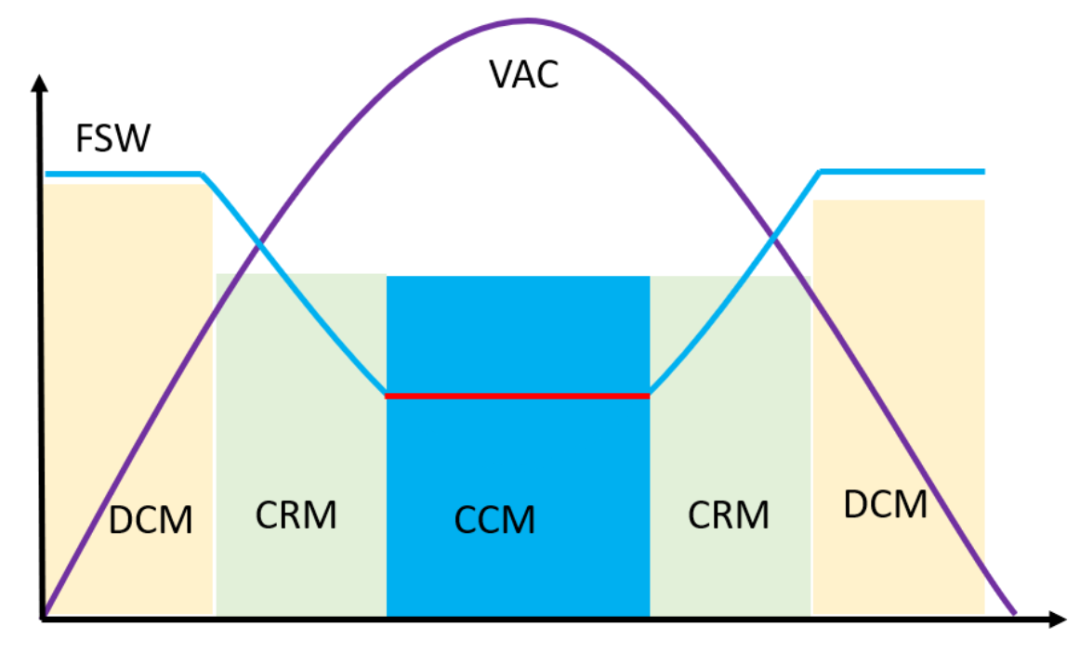

簡單地說,混合PFC的控制策略就是操縱開關頻率在正弦電壓內進行變化來進行跨越多個區域,難點是多模式區域的增益不會統一,實現多模式優秀的電流控制效果就是難題

2023-04-25 14:20:29 1013

1013

JLINK調試雅特力AT32F403Avc的問題,無法發現芯片(在keil下可以),如何解決?我把芯片型號切換城STM32F103vc就可以

2023-04-17 17:43:42

??近日,數模混合信號鏈和時鐘芯片設計公司核芯互聯,宣布完成數億元B輪融資,本輪融資由招商資本,華強創投和老股東東方富海聯合投資。 核芯互聯成立于2018年,在北京、青島、上海、成都設有研發中心

2023-04-04 17:20:06 1427

1427 的 2000 個虛擬時鐘。我唯一沒有做的是在 IOCONFIG 寄存器中設置 TDR 數據,因為應用筆記(在 BSDL 文件中提到)不可用!有人可以發布 TDR 模式嗎?我嘗試使用 NXP 的 LS1028 評估板設置邊界掃描。結果是一樣的。還有其他建議嗎?

2023-03-31 06:52:45

我正在使用 IMX8m Plus 構建定制板,我想使用邊界掃描來測試板的連接。為此,我正在 (8MPLUSLPD4-EVK) 上進行試驗,以檢查 JTAG 連接以及進入邊界掃描模式需要執行的操作。我

2023-03-29 06:05:21

電子發燒友App

電子發燒友App

評論