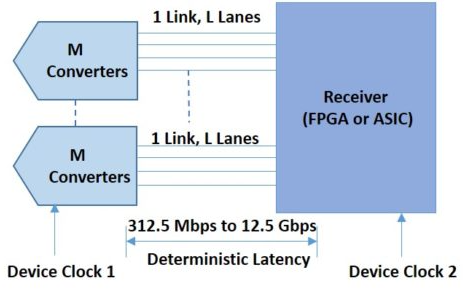

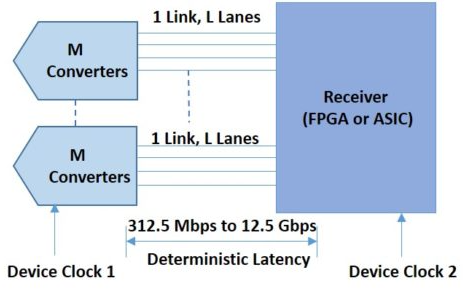

JESD204B標準提供一種將一個或多個數(shù)據(jù)轉(zhuǎn)換器與數(shù)字信號處理器件接口的方法(通常是ADC或DAC與FPGA接口),相比于通常的并行數(shù)據(jù)傳輸,這是一種更高速度的串行接口。

2024-03-20 11:33:34 32

32

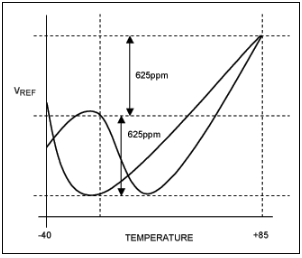

描述AD5541A是一款單通道、16位、串行輸入、無緩沖電壓輸出數(shù)模轉(zhuǎn)換器(DAC),采用2.7 V至5.5 V單電源供電。DAC輸出范圍為0 V至VREF,保證單調(diào)性,提供±1 LSB INL精度

2024-03-14 10:15:14

轉(zhuǎn)換誤差率(CER)的時域應(yīng)用。AD9213具有16通道JESD204B接口,以支持最大帶寬能力。AD9213實現(xiàn)了動態(tài)范圍和線性度性能,同時功耗小于4.6 W(

2024-03-07 15:54:36

AD9172BBPZ AD9172BBPZ AD9172BBPZ 是一款支持 12.6 GSPS 的 DAC 采樣速率的高性能雙通道 16 位數(shù)模轉(zhuǎn)換器 (DAC

2024-02-27 19:19:55

AD9689BBPZ-2600 是一款雙通道、14位、2.0 GSPS/2.6 GSPS模數(shù)轉(zhuǎn)換器(ADC)。該器件內(nèi)置片內(nèi)緩沖器和采樣保持電路,專門針對低功耗、小尺寸和易用性而設(shè)計。該

2024-02-27 19:13:27

ADS54J69 是一款低功耗、高帶寬 16 位、500MSPS 雙通道模數(shù)轉(zhuǎn)換器 (ADC)。該器件經(jīng)設(shè)計具有高信噪比 (SNR),可提供 -159dBFS/Hz 的噪底,從而 協(xié)助應(yīng)用在寬瞬時

2024-02-27 17:56:07

AD9166BBPZ是高性能、寬帶、片內(nèi)矢量信號發(fā)生器,由高速 JESD204B 串行器/解串器(SERDES)接口、靈活的 16 位數(shù)字數(shù)據(jù)路徑、正交 (IQ) 數(shù)模轉(zhuǎn)換器 (DAC) 內(nèi)核以及一

2024-02-26 18:25:03

國芯思辰SC6301是高性能時鐘調(diào)節(jié)器,支持JEDEC JESD204B。當使用設(shè)備和SYSREF時鐘時,PLL2的14個時鐘輸出可配置去驅(qū)動7個JESD204B轉(zhuǎn)換器或其他邏輯設(shè)備。SYSREF

2024-02-19 09:41:40

AD9177BBPZ是一款高度集成的套件,具有四個 16 位、12 GSPS 最大采樣率、RF 數(shù)模轉(zhuǎn)換器 (DAC) 內(nèi)核,支持多達八個基帶通道。該套件非常適合需要寬帶 DAC 來處理寬瞬時帶寬

2024-02-16 17:16:40

/10b 模式兼容 JESD204B

可選數(shù)字下變頻器 (DDC):

4 倍、8 倍、16 倍和 32 倍復(fù)雜抽取

每個 DDC 均具有四個獨立的 32 位 NCO

峰值射頻輸入功率 (Diff

2024-01-31 15:22:55

描述AD9175 是一款支持高達 12.6 GSPS 的 DAC 采樣速率的高性能雙通道 16 位數(shù)模轉(zhuǎn)換器 (DAC)。該套件采用 8 線 15.4 Gbps JESD204B 數(shù)據(jù)輸入

2024-01-26 11:24:33

描述AD9174是一款高性能、雙通道、16位數(shù)模轉(zhuǎn)換器(DAC),支持高達12.6 GSPS的DAC采樣速率。該器件具有8通道、15.4 Gbps JESD204B數(shù)據(jù)輸入端口、高性能片內(nèi)DAC時鐘

2024-01-26 11:20:37

描述AD91661 是高性能、寬帶、片內(nèi)矢量信號發(fā)生器,由高速 JESD204B 串行器/解串器(SERDES)接口、靈活的 16 位數(shù)字數(shù)據(jù)路徑、正交 (IQ) 數(shù)模轉(zhuǎn)換器 (DAC) 內(nèi)核以及一

2024-01-26 11:17:50

描述AD9173是一款高性能、雙通道、16位數(shù)模轉(zhuǎn)換器(DAC),支持高達12.6 GSPS的DAC采樣速率。該器件具有8通道、15.4 Gbps JESD204B數(shù)據(jù)輸入端口、高性能片內(nèi)DAC時鐘

2024-01-26 11:13:59

AD9177BBPZ一款高度集成的套件,具有四個 16 位、12 GSPS 最大采樣率、RF 數(shù)模轉(zhuǎn)換器 (DAC) 內(nèi)核,支持多達八個基帶通道。該套件非常適合需要寬帶 DAC 來處理寬瞬時帶寬信號

2024-01-04 20:01:43

CS43198 音頻數(shù)模轉(zhuǎn)換器HIFICS43198 是下一代低功耗音頻數(shù)模轉(zhuǎn)換器 (DAC),可提供卓越的系統(tǒng)級音頻性能,而不會縮短電池壽命。該IC最大程度降低了電路板空間要求,同時支持推動

2024-01-03 15:45:10 1

1 ,使用JESD204B的雙通道ADC。大部分情況下,雙通道ADC針對兩個轉(zhuǎn)換器提供單個時鐘輸入。它將迫使ADC以同樣的頻率進行模擬采樣。但對于某些特定的應(yīng)用而言,這類器件也可能采用兩個獨立的輸入時鐘,每個時鐘可

2024-01-03 06:35:04

數(shù)模轉(zhuǎn)換器和模數(shù)轉(zhuǎn)換器是兩種相反的功能,它們分別是將數(shù)字信號轉(zhuǎn)換為模擬信號和將模擬信號轉(zhuǎn)換為數(shù)字信號。

2023-12-27 18:18:29 655

655 我想知道AD5541數(shù)模轉(zhuǎn)換器能夠轉(zhuǎn)換的信號帶寬是多少,為什么芯片手冊上沒有,我用這款芯片對10kHz的信號可以進行轉(zhuǎn)換,而換成25kHz左右的信號卻不能正常轉(zhuǎn)換,這是怎么回事?

2023-12-20 06:00:32

目前,我在設(shè)計中想使用ZYNQ 7015系列的FPGA,利用JESD204 IP核接收A/D轉(zhuǎn)換器AD9683轉(zhuǎn)換完成后的數(shù)據(jù)。但是JESD204 IP核的端口很多,我不知道應(yīng)該如何將AD9683

2023-12-15 07:14:52

描述AD7528是一款單芯片、雙通道、8位數(shù)模轉(zhuǎn)換器,具有出色的DAC間匹配特性,提供0.3"寬、20引腳超小型DIP和20引腳表面貼裝兩種封裝。 各DAC均配有單獨的片內(nèi)鎖存器,可以與微處理器輕松

2023-12-14 09:49:29

數(shù)模轉(zhuǎn)換器AD9161能否穩(wěn)定的長時間工作在2xNRZ模式下即轉(zhuǎn)換率為12Gsps ?

2023-12-14 07:34:35

使用AD9680時遇到一個問題,AD9680采樣率為1Gsps,JESD204B IP核的GTX參考時鐘為250MHz,參數(shù)L=4,F(xiàn)=2,K=32,線速率為10Gbps,使用的為SYSREF

2023-12-12 08:03:49

我使用的是KC705板卡,調(diào)用了里面JESD204B的IP核,使用模式為interpolation值為4,4條鏈路,DAC頻率為2.5GHZ,通道速度為6.25GHZ,出現(xiàn)的問題是:

幀同步過程

2023-12-12 07:28:25

用單片AD9690采集數(shù)據(jù)給FPGA,不要求確定延遲,因此想要把AD9690配置在JESD204B sublcass 0 模式下。但是這種模式下,對于AD9690的SYSREF±的輸入管腳怎么處理?以及AD9690工作在subclass 0 模式下還有沒有其他要注意的地方?

2023-12-12 06:16:08

描述 AD7528是一款單芯片、雙通道、8位數(shù)模轉(zhuǎn)換器,具有出色的DAC間匹配特性,提供0.3"寬、20引腳超小型DIP和20引腳表面貼裝兩種封裝。各DAC均配有單獨的片內(nèi)鎖存器,可以

2023-12-11 10:47:49

模數(shù)轉(zhuǎn)換器AD9625的評估板AD-FMCADC3-EBZ能不能和賽靈思的Virtex7系列FPGA開發(fā)板連接,我看到他們都具備JESD204B接口,物理接口上能直接連嗎?還是說需要在使用轉(zhuǎn)換接口來連接?

2023-12-08 08:25:12

FPGA,使用了xilinx提供的JESD204B core,可以發(fā)送正弦波數(shù)據(jù)到DAC芯片。

目前的調(diào)試情況:根據(jù)手冊提供的配置流程配置AD9144,查詢相關(guān)寄存器,DAC PLL和Serdes PLL

2023-12-08 06:00:25

描述 AD9164是一款高性能16位數(shù)模轉(zhuǎn)換器(DAC)和直接數(shù)字頻率合成器(DDS),支持高達6 GSPS的更新速率。DAC內(nèi)核基于一個四通道開關(guān)結(jié)構(gòu),配合2倍插值濾波器,使DAC的有效

2023-12-06 10:51:37

8路時鐘用于產(chǎn)生JESD204B接口使用的時鐘,寄存器配置參考了AD9523-1開發(fā)板軟件,調(diào)試了好久沒有輸出,spi寄存器配置的時候使用了三點式和四線式,三點式的時候SDIO一直為低,他作為雙極

2023-12-06 07:48:32

使用內(nèi)部PLL,輸入?yún)⒖碱l率為100MHz。在采樣率時鐘設(shè)置為1GHz時,DAC的JESD204B鏈路能建立,但是當頻率改為1.5GHz時,SYNC一直為低。其他相關(guān)寄存器都已經(jīng)修改,serdes

2023-12-05 08:17:30

9680測試評估中遇到問題:

按照數(shù)據(jù)手冊中的配置步驟,關(guān)斷鏈路,通過0x570和0X56E寄存器快速配置JESD204B,鏈路上電后,電路鎖相環(huán)無法鎖定,204B無法正常輸出數(shù)據(jù)。

2023-12-05 08:04:26

決。

我配置基本參數(shù)為DAC速率6G,6倍插值,JESD204B線速率5G。L=8,M=2,F=1,S=2.SYSREF=3.90625MHz.

2023-12-04 07:30:17

AD9164 JESD204B接口的傳輸層是如何對I/Q數(shù)據(jù)進行映射的

2023-12-04 07:27:34

直接輸出4G給DAC的clk的,內(nèi)部[size=200%]PLL關(guān)閉,nco旁路,所有內(nèi)插均為1,jesd204B選擇模式20。

2023-12-04 06:56:33

描述 AD7628是一款單芯片、雙通道、8位數(shù)模轉(zhuǎn)換器,具有出色的DAC間匹配特性,提供0.3"寬、20引腳小型DIP和20引腳表面貼裝兩種封裝。 各DAC均配有單獨的片內(nèi)鎖存器,可以

2023-12-01 17:11:45

在AD9680和AD9690數(shù)據(jù)手冊上,寫著它們[size=200%]支持的最小通道線率是3125Mbps,但是在JESD204B標準手冊寫著最小通道線率是312.5Mbps。

我疑惑這是數(shù)據(jù)手冊的錯誤,還是AD9680和AD9690這兩款芯片支持的最低通道線率確實時3125Mbps

2023-12-01 07:57:58

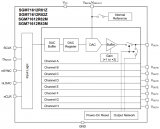

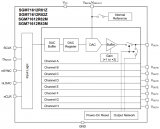

圣邦微電子推出 SGM71612R81/SGM71612R82/SGM71612R83 系列,8 通道、16 位、SPI 接口、具有 10ppm/℃ 片上基準的電壓輸出型數(shù)模轉(zhuǎn)換器(DAC)。該器件可應(yīng)用于過程控制和 DCS 系統(tǒng)、數(shù)據(jù)采集系統(tǒng),以及實驗室儀器。

2023-11-29 10:19:18 388

388

作者:Ian Beavers,ADI公司應(yīng)用工程師 JESD204B串行數(shù)據(jù)鏈路接口針對支持更高速轉(zhuǎn)換器不斷增長的帶寬需求而開發(fā)。作為第三代標準,它提供更高的通道速率最大值(每通道高達12.5

2023-11-28 14:24:47 0

0 數(shù)模轉(zhuǎn)換器(DAC)將數(shù)字(用于計算機,如微控制器)轉(zhuǎn)換為模擬電壓。它們與模數(shù)轉(zhuǎn)換器(ADC)相反。

2023-11-28 10:57:33 409

409

電子發(fā)燒友網(wǎng)站提供《JESD204B規(guī)范的傳輸層介紹.pdf》資料免費下載

2023-11-28 10:43:31 0

0 數(shù)模轉(zhuǎn)換器的分辨率是指其能夠表示和轉(zhuǎn)換的數(shù)字信號的精度和粒度。

2023-11-28 09:20:56 377

377 數(shù)模轉(zhuǎn)換器(ADC)是將模擬信號轉(zhuǎn)換為數(shù)字信號的設(shè)備,而模數(shù)轉(zhuǎn)換器(DAC)則是將數(shù)字信號轉(zhuǎn)換為模擬信號的設(shè)備。

2023-11-27 18:23:51 698

698 電子發(fā)燒友網(wǎng)站提供《乘法數(shù)模轉(zhuǎn)換器 (DAC) 與常規(guī)固定參考信號 DAC 的區(qū)別.pdf》資料免費下載

2023-11-27 09:48:58 0

0 電子發(fā)燒友網(wǎng)站提供《高速轉(zhuǎn)換器組表征高速數(shù)模轉(zhuǎn)換器(DAC)的性能測試方法.pdf》資料免費下載

2023-11-27 09:45:37 0

0 前言TSW14J57EVM數(shù)據(jù)采集/圖形發(fā)生器:具有 16 個 JESD204B 通道 (1.6-15Gbps) 的數(shù)據(jù)轉(zhuǎn)換器 EVM提示:以下是本篇文章正文內(nèi)容,下面案例可供參考一

2023-11-21 15:05:23

描述 DAC38RF82 和 DAC38RF89 是高性能的寬帶寬型射頻采樣數(shù)模轉(zhuǎn)換器 (DAC),能夠?qū)崿F(xiàn)高達 3.33GSPS 的雙通道輸入數(shù)據(jù)速率或高達 9GSPS 的 8 位單通道

2023-11-10 14:03:59

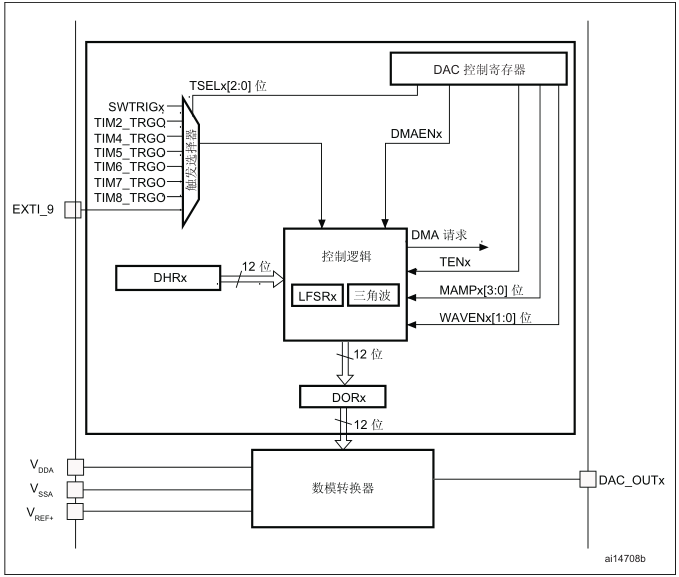

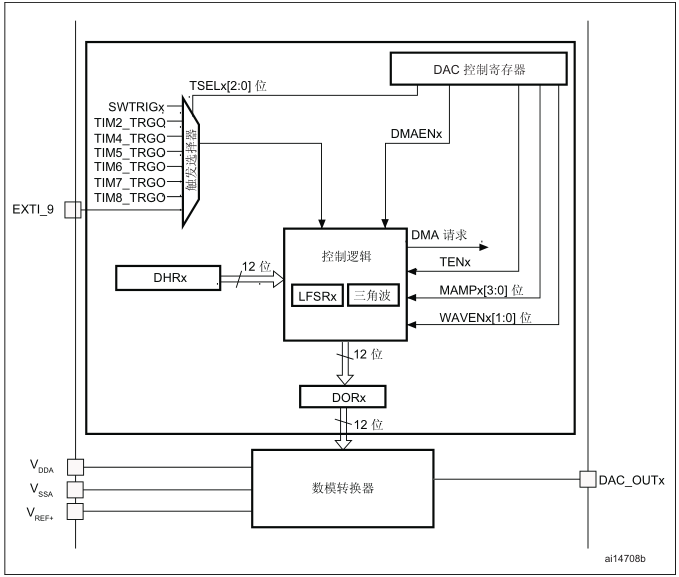

的模擬輸出。數(shù)字部分可以配置為 8 位或者 12 位模式,支持單/雙 DAC 的左對齊或者右對齊,同時可以與 DMA 配合使用。下表 AT32 型號均支持兩路 DAC,DAC1/DAC2 各有一個數(shù)模轉(zhuǎn)換器

2023-10-25 06:31:37

電子發(fā)燒友網(wǎng)為你提供ADI(ADI)AD9094: 8-Bit, 1 GSPS, JESD204B, Quad Analog-to-Digital Converter Data Sheet相關(guān)產(chǎn)品

2023-10-17 19:13:59

電子發(fā)燒友網(wǎng)為你提供ADI(ADI)AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊,更有AD9207

2023-10-16 19:02:55

LogiCORE IP JESD204內(nèi)核實現(xiàn)了一個JESD204B接口,使用GTX、GTH、GTP或GTY(僅限UltraScale和UltraScale+)收發(fā)器在1至8個通道上支持1至12.5

2023-10-16 10:57:17 358

358

本應(yīng)用說明給出了使用Digital toSTM32F10xx微控制器系列中嵌入的模擬轉(zhuǎn)換器(DAC)外圍設(shè)備。

數(shù)模轉(zhuǎn)換器(DAC)是一種功能與模數(shù)轉(zhuǎn)換器相反的設(shè)備數(shù)字轉(zhuǎn)換器,它將數(shù)字字轉(zhuǎn)換為相應(yīng)

2023-10-10 07:32:07

電子發(fā)燒友網(wǎng)為你提供ADI(ADI)AD9694-EP: 14比特、500 MSPS、JESD204B、“四向數(shù)字轉(zhuǎn)換器”強化產(chǎn)品數(shù)據(jù)表相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊,更有AD9694-EP: 14比特

2023-10-09 19:12:15

電子發(fā)燒友網(wǎng)為你提供ADI(ADI)AD9694S: 14-Bit, 500 MSPS, JESD 204B, 二次對數(shù)字轉(zhuǎn)換器數(shù)據(jù)表相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊,更有AD9694S: 14-Bit

2023-10-08 16:48:36

電子發(fā)燒友網(wǎng)站提供《5位數(shù)模轉(zhuǎn)換器.pdf》資料免費下載

2023-09-20 14:55:05 0

0 電子發(fā)燒友網(wǎng)站提供《一種基于JESD204B的射頻信號高速采集系統(tǒng).pdf》資料免費下載

2023-09-14 11:14:07 1

1 AD9144是一款支持jesd204b協(xié)議高速DAC芯片。AD9144-FMC-EBZ是基于AD9144的評估板(Evaluation Board),它是主要由AD9144,AD9516,與PIC16F單片機組成的系統(tǒng)。

2023-09-13 09:20:22 996

996

兩個DAC轉(zhuǎn)換器每個對應(yīng)一個輸出通道 支持8位和12位的單一輸出 12位模式下支持數(shù)據(jù)左對齊或右對齊 同步更新功能 產(chǎn)生噪聲波或三角波 雙DAC通道能分別獨立轉(zhuǎn)換或同時轉(zhuǎn)換 每個通道都支持DMA傳輸

2023-09-12 07:00:26

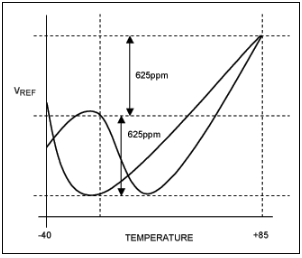

DAC756x-Q1、DAC816x-Q1和DAC 856 x-Q1(DAC x6x-Q1)分別是低功耗、電壓輸出、雙通道、12/14/16位數(shù)模轉(zhuǎn)換器(DAC)。這些器件內(nèi)置一個2.5 V、4

2023-08-31 11:03:09

數(shù)模轉(zhuǎn)換器(DAC)

2023-08-30 18:32:34

和時域應(yīng)用。AD9213具有16通道JESD204B接口,以支持最大帶寬能力。AD921 3實現(xiàn)動態(tài)范圍和線性性能,同時典型功耗

2023-08-29 16:05:55 0

0 LTC?2686是一款8通道、16位、±15 V數(shù)模轉(zhuǎn)換器(DAC),集成了一個精密基準電壓源。The LTC2686保證單調(diào)性,并內(nèi)置軌到軌輸出緩沖器可供應(yīng)或吸收高達 55 mA 的電流

2023-08-14 18:13:35 1

1 AD9144是一款四通道、16位、高動態(tài)范圍數(shù)模轉(zhuǎn)換器(DAC),提供最大采樣速率2.8 GSPS,允許多載波發(fā)電高達奈奎斯特頻率。DAC 輸出經(jīng)過優(yōu)化,可連接與ADRF6720模擬正交調(diào)制器無縫

2023-08-14 18:09:19 0

0

?CMOS低功耗

?高抗噪性

?根據(jù)JESD 78 Class II Level B,閂鎖性能超過100 mA

?異步8位并行負載

?同步串行輸入

?輸入水平:

?對于74HC165:CMOS級別

?對于

2023-08-04 17:39:53

AD9176是一款高性能、雙通道、16位數(shù)模轉(zhuǎn)換器(DAC),支持最高12.6 GSPS的DAC采樣速率。該器件具有一個8通道、15.4 Gbps JESD204B數(shù)據(jù)輸入端口、一個高性能片內(nèi)DAC

2023-07-25 14:41:00

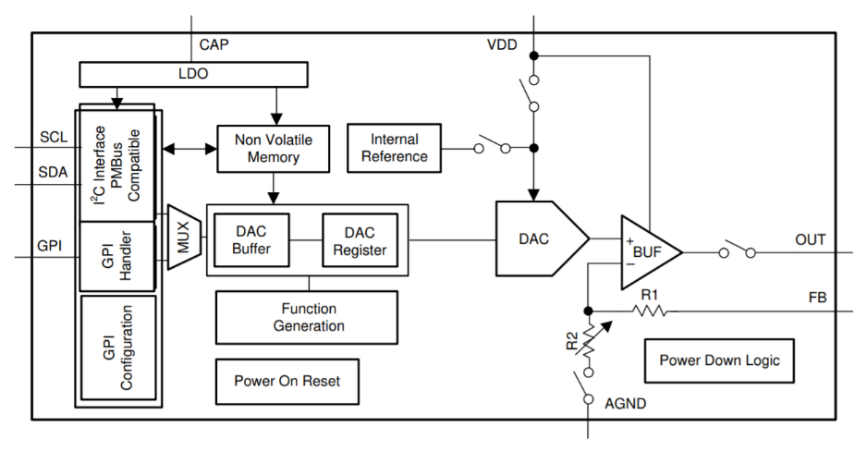

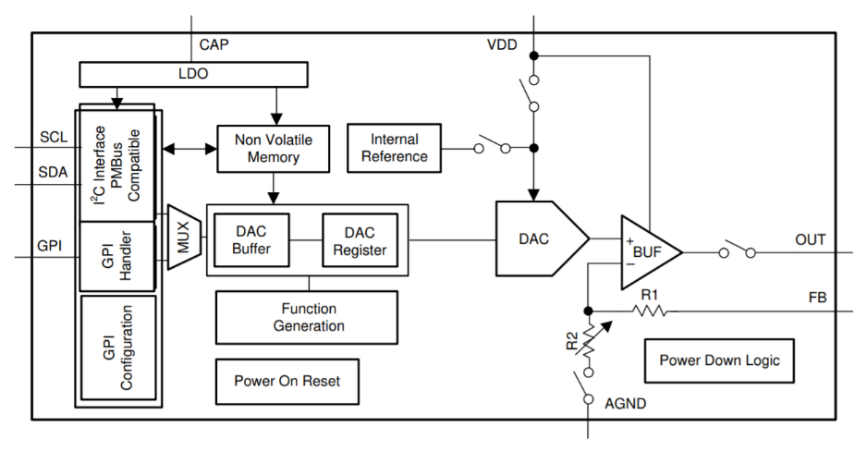

工程師們一直在努力尋找更有效、更高效且成本更低的解決方案。當需要對模擬輸出進行非常精確的控制時,系統(tǒng)設(shè)計人員通常使用精密數(shù)模轉(zhuǎn)換器(DAC)。需要精確控制輔助功能的設(shè)計通常還需要結(jié)合使用分立式模擬元件和微控制器(MCU)來控制DAC的輸出。

2023-07-23 17:20:46 448

448

STM32F4xx系列提供的DAC模塊是12 位電壓輸出數(shù)模轉(zhuǎn)換器。DAC可以按 8 位或 12 位模式進行配置,并且可與DMA控制器配合使用。

2023-07-22 16:43:46 1773

1773

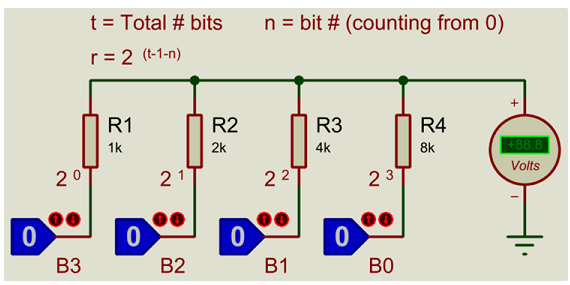

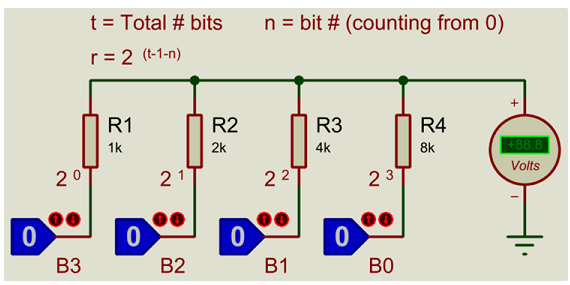

數(shù)模轉(zhuǎn)換器(DAC)將數(shù)字(用于計算機,如微控制器)轉(zhuǎn)換為模擬電壓。它們與模數(shù)轉(zhuǎn)換器(ADC)相反。數(shù)模轉(zhuǎn)換器(DAC)有兩種主要類型:二進制加權(quán)和R-2R

2023-07-19 15:03:31 723

723

數(shù)模轉(zhuǎn)換器是一種電子設(shè)備,用于將數(shù)字信號轉(zhuǎn)換為模擬信號。它可以實現(xiàn)多種功能,其中包括:

2023-07-19 10:29:07 619

619 本文旨在提供發(fā)生 JESD204B 鏈路中斷情況下的調(diào)試技巧簡介

2023-07-10 16:32:03 802

802

該芯片是高性能時鐘調(diào)節(jié)器,支持JEDEC JESD204B。當使用設(shè)備和 SYSREF 時鐘時,PLL2 的 14 個時鐘輸出可配置去驅(qū)動 7 個JESD204B 轉(zhuǎn)換器或其他邏輯設(shè)備。

2023-06-25 10:13:46 848

848 SC6301是高性能時鐘調(diào)節(jié)器,支持JEDEC JESD204B。當使用設(shè)備和SYSREF時鐘時,PLL2的14個時鐘輸出可配置去驅(qū)動7個JESD204B轉(zhuǎn)換器或其他邏輯設(shè)備。

2023-06-21 15:11:14 508

508

SC6301是高性能時鐘調(diào)節(jié)器,支持JEDEC JESD204B。當使用設(shè)備和SYSREF時鐘時,PLL2的14個時鐘輸出可配置去驅(qū)動7個JESD204B轉(zhuǎn)換器或其他邏輯設(shè)備。SYSREF可以使用直流和交流耦合來提供。不僅限于JESD204B應(yīng)用,14個輸出均可單獨配置為傳統(tǒng)高性能時鐘系統(tǒng)輸出。

2023-06-21 15:10:58 608

608

SYSREF計時校準▲樣片標記時間戳■JESD204B串行數(shù)據(jù)接口:▲支持子類0和1▲最大通道速率:12.8Gbps▲多達16個通道可降低通道速率■雙通道模式下的數(shù)字下變頻器:▲實際輸出:DDC旁路或

2023-06-16 14:37:21

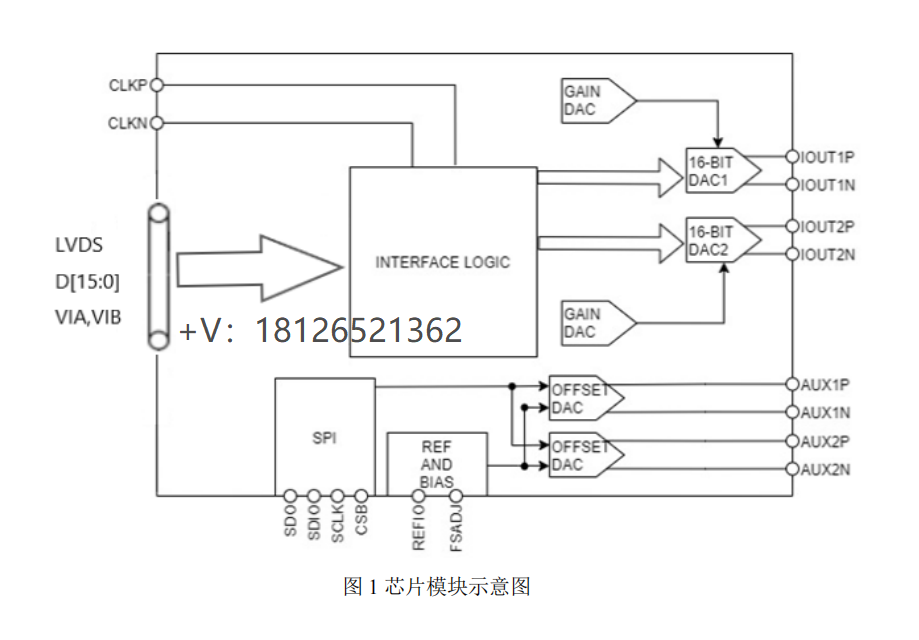

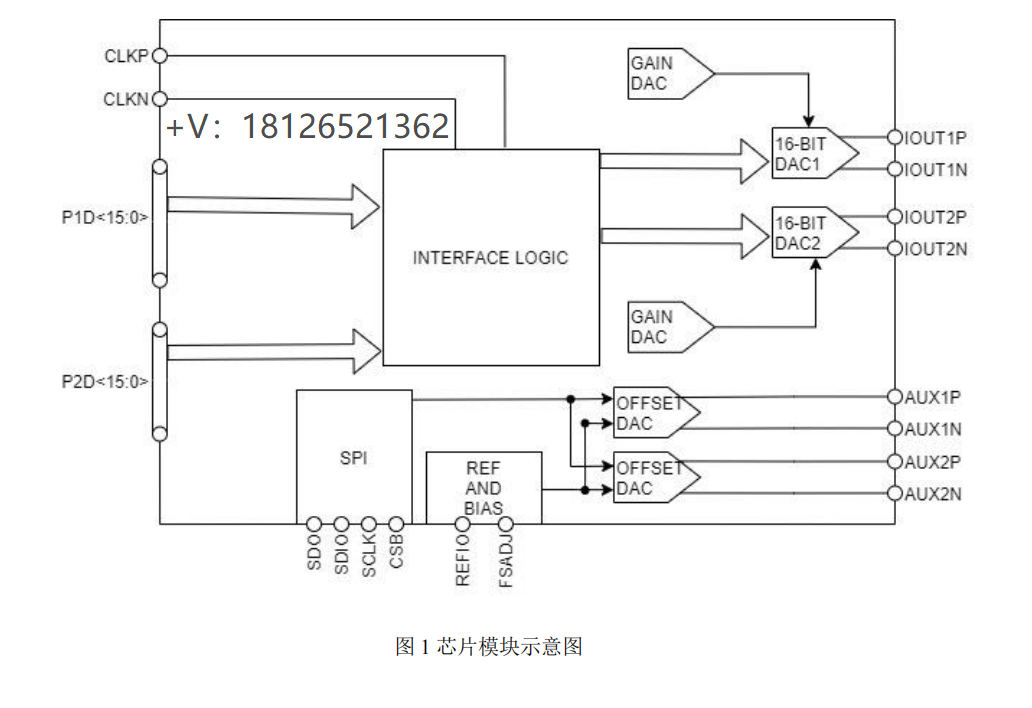

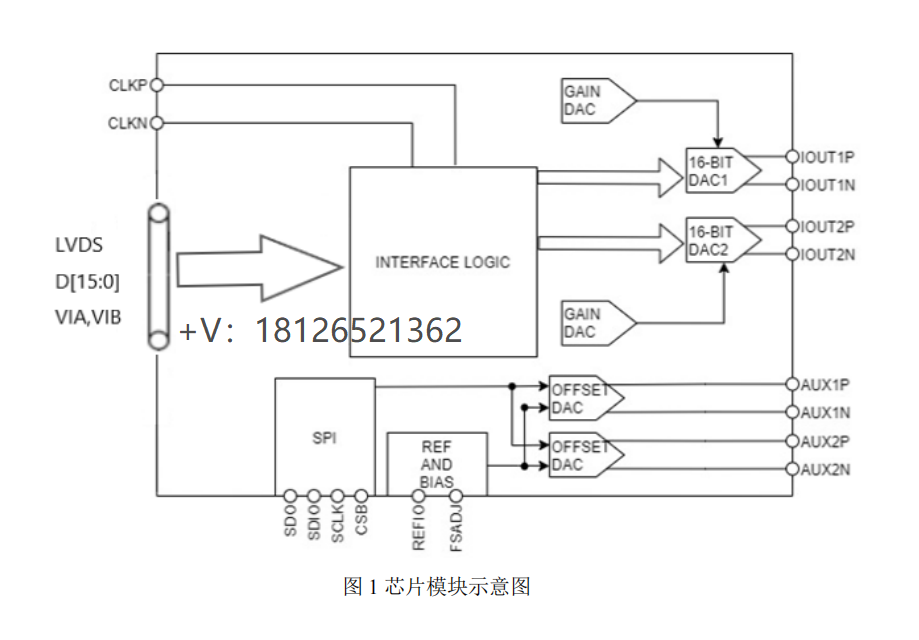

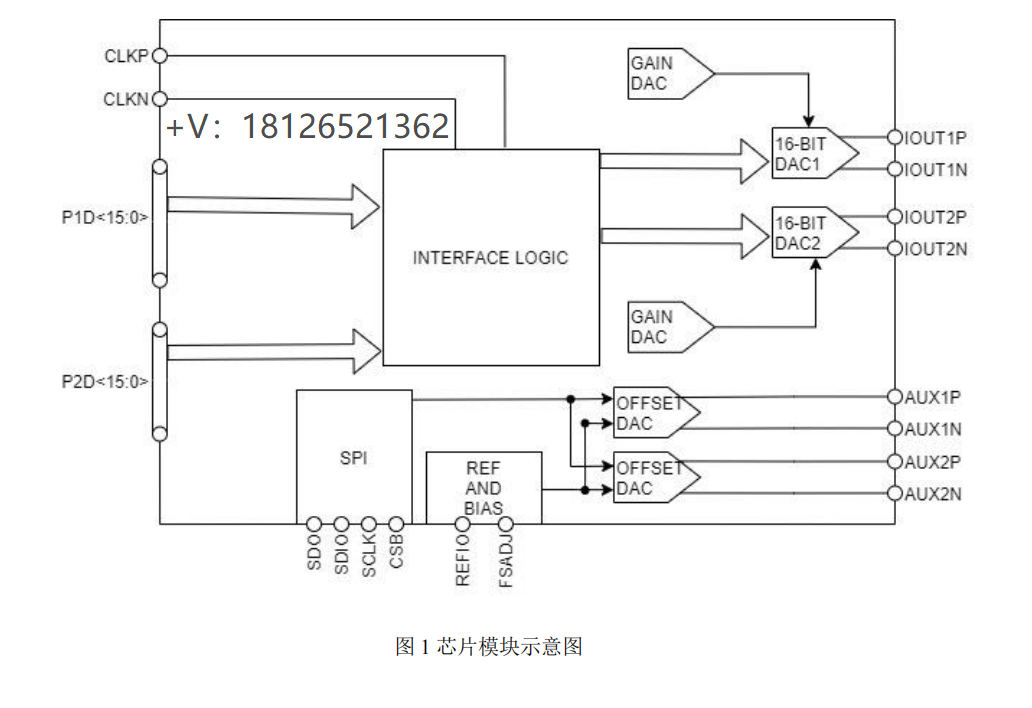

串行外設(shè)接口(SPI),還可以為沒有控制器的應(yīng)用提供一些引腳編程功能。 低噪聲和互調(diào)失真(IMD)可實現(xiàn)寬帶信號的高質(zhì)量合成。 多種輸出模式,可增強動態(tài)性能。 可編程電流輸出和雙輔助 DAC 提供了系統(tǒng)靈活性和功能增強。 主要性能 高動態(tài)范圍、雙通道數(shù)模轉(zhuǎn)換器 (DAC) 低噪聲和互

2023-06-15 09:59:28 496

496

串行外設(shè)接口(SPI),還可以為沒有控制器的應(yīng)用提供一些引腳編程功能。 低噪聲和互調(diào)失真(IMD)可實現(xiàn)寬帶信號的高質(zhì)量合成。 多種輸出模式,可增強動態(tài)性能。 可編程電流輸出和雙輔助 DAC 提供了系統(tǒng)靈活性和功能增強。 主要性能 高動態(tài)范圍、雙通道數(shù)模轉(zhuǎn)換器 (DAC) 低噪聲和互

2023-06-14 14:31:03 317

317

在設(shè)計數(shù)模轉(zhuǎn)換器(DAC)系統(tǒng)時,DAC規(guī)格及其基準電壓源協(xié)同工作,以產(chǎn)生整體系統(tǒng)性能。因此,DAC和參考應(yīng)同時選擇。組件的規(guī)格可以相互權(quán)衡,以確保以最低的成本滿足系統(tǒng)規(guī)格。

2023-06-10 16:06:55 960

960

核芯互聯(lián)發(fā)布8通道12/14/16bit8通道DAC產(chǎn)品CL4258, CL4458, CL4658, 該系列產(chǎn)品是低功耗,8通道,12/14/16位緩沖電壓輸出DAC(數(shù)模轉(zhuǎn)換器),采用4.5 V至5.5 V單電源供電,通過設(shè)計保證單調(diào)性。

2023-06-09 17:01:06 1702

1702

您的PCB可以處理高達12.5Gbps的速度嗎,感到驚訝,對嗎?JESD204B標準為串行接口提供高達12.5Gbps的比特率。這種升級允許設(shè)計人員在FPGA/ASIC上使用更少的收發(fā)器,從而減少

2023-05-26 14:50:57 608

608

JESD204B規(guī)范是JEDEC標準發(fā)布的較新版本,適用于數(shù)據(jù)轉(zhuǎn)換器和邏輯器件。如果您正在使用FPGA進行高速數(shù)據(jù)采集設(shè)計,您會聽到新的流行詞“JESD204B”。與LVDS和CMOS接口相比,這一較新的版本具有顯著的優(yōu)勢,因為它包括更簡單的布局和更少的引腳數(shù)。

2023-05-26 14:49:31 361

361

數(shù)模轉(zhuǎn)換器 (DAC) 的模擬輸出可以是電壓輸出,也可以是電流輸出。輸出阻抗是任何輸出類型的重要參數(shù)之一。對于電壓模式輸出,一般會應(yīng)用二進制加權(quán)電阻網(wǎng)絡(luò)進行數(shù)模轉(zhuǎn)換。

2023-05-11 09:41:42 480

480

大部分的ADC和DAC都支持子類1,JESD204B標準協(xié)議中子類1包括:傳輸層,鏈路層,物理層。在少部分資料中也會介紹含有應(yīng)用層,應(yīng)用層是對JESD204B進行配置的接口,在標準協(xié)議中是不含此層,只是為了便于理解,添加的一個層。

2023-05-10 15:52:55 1369

1369

我們介紹過了 STM32F1 的模數(shù)轉(zhuǎn)換器 ADC,接下來我們學習下STM32F1 的數(shù)模轉(zhuǎn)換器 DAC。要實現(xiàn)的功能是:通過 K_UP 與K_DOWN 按鍵控制 STM32F1 DAC1 輸出電壓

2023-05-04 10:08:30 3152

3152

芯晶圖杭州辦潘子DEMO參考資料聯(lián)系我電話在主頁提供技術(shù)支持DEMO參考資料SC3361雙通道16位250MSPSDAC替代AD9747主要性能:?高動態(tài)范圍、雙通道數(shù)模轉(zhuǎn)換器(DAC)?低噪聲

2023-04-23 14:18:06 3

3 LMK04821系列器件為該話題提供了很好的范例研究素材,因為它們是高性能的雙環(huán)路抖動清除器,可在具有器件和SYSREF時鐘的子類1時鐘方案里驅(qū)動多達七個JESD204B轉(zhuǎn)換器或邏輯器件。圖1是典型JESD204B系統(tǒng)(以LMK04821系列器件作為時鐘解決方案)的高級方框圖。

2023-04-18 09:25:30 915

915

我正在使用 NXP S32k148 工具箱,我想在我想使用數(shù)模轉(zhuǎn)換器(即 DAC)的地方構(gòu)建模型。那么我可以在這里使用哪個工具箱?或者如何在 MBD 中實現(xiàn) DAC(數(shù)模轉(zhuǎn)換器)。

2023-04-07 12:50:57

數(shù)模轉(zhuǎn)換器- DAC Dual, 16-b 2.8Gsps DAC,10.6Gbps JESD204B

2023-04-06 17:44:13

數(shù)模轉(zhuǎn)換器(DAC)?DIP-8

2023-03-24 16:42:59

電子發(fā)燒友App

電子發(fā)燒友App

評論