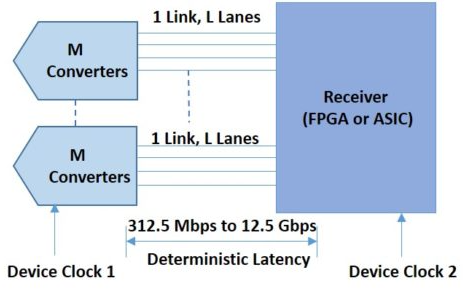

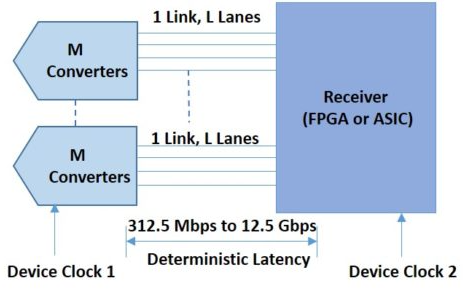

JESD204B標準提供一種將一個或多個數據轉換器與數字信號處理器件接口的方法(通常是ADC或DAC與FPGA接口),相比于通常的并行數據傳輸,這是一種更高速度的串行接口。

2024-03-20 11:33:34 32

32

Holt的八通道ARINC 429線路接收器HI-8456、HI-8457和HI-8458系列包括內部防雷電路,可確保符合RTCA/DO-160G第22節3級引腳注入測試波形集A(3&4)、集B

2024-02-19 19:23:11

HI-8454和HI-8455是四通道ARINC 429線路接收器,每個通道都有內部防雷電路。該保護電路確保符合RTCA/DO-160G第22節3級引腳注入測試波形集A(3&4)、集B

2024-02-19 19:19:58

HI-8448是一款八進制ARINC 429線路接收器IC,采用44針塑料四平面封裝(PQFP)。每個獨立的接收器通道將傳入的ARINC 429數據總線信號轉換為一對相關的互補式金屬氧化物半導體

2024-02-19 15:16:47

國芯思辰SC6301是高性能時鐘調節器,支持JEDEC JESD204B。當使用設備和SYSREF時鐘時,PLL2的14個時鐘輸出可配置去驅動7個JESD204B轉換器或其他邏輯設備。SYSREF

2024-02-19 09:41:40

全集成的時鐘合成器適用于射頻 LO 和基帶時鐘的多芯片相位同步JESD204B 數據路徑接口調諧范圍:75 MHz 至 6000 MHzADRV9009是一款高集

2024-02-17 17:41:30

信號的應用。該套件具有 8 通道、24.75 Gbps JESD204C 或 15.5 Gbps JESD204B 數據接收器 (JRx) 端口、片內時鐘乘法器和數

2024-02-16 17:16:40

15KHZ超聲波模具20KHZ超音波模具

15KHZ超聲波模具20KHZ超音波模具深圳市宏大電子設備有限公司都選用進口鋁鎂合金7075.頻率好硬度高,經久耐用!

超聲波模具的設計與制作相當重要,你

2024-02-16 15:30:54

數進行權衡。支持 8b/10b 和 64b/66b 數據編碼方案。64b/66b 編碼支持前向糾錯 (FEC),可改進誤碼率。此接口向后兼容 JESD204B 接收器。

無噪聲孔徑延遲調節

2024-01-31 15:22:55

描述HI-8444/HI-8445是一款四通道ARINC 429線路接收器ic,采用20引腳小型塑料TSSOP封裝。每個獨立的接收器通道將輸入的ARINC 429數據總線信號轉換為相關的一對CMOS

2024-01-11 11:09:27

描述HI-8450和HI-8451是單通道ARINC 429線路接收器,內置防雷電路。該保護電路確保符合RTCA/DO-160G第22節3級引腳注入測試波形集A (3 & 4)、集B (3 & 5A

2024-01-08 14:05:30

電路參考了手冊,輸入電壓12V,1通道設置輸出為1.2V,2通道設置輸出為3.3V,3通道設置輸出為1.8V,4通道設置輸出為3.3V,結果3、4通道輸出電壓正常,1通道和2通道輸出始終為輸入電壓

2024-01-05 12:25:13

的應用。該套件具有 8 通道、24.75 Gbps JESD204C 或 15.5 Gbps JESD204B 數據接收器 (JRx) 端口、片內時鐘乘法器和數字

2024-01-04 20:01:43

描述HI-8588是一款ARINC 429總線接口接收器,采用SO 8引腳封裝。該技術是模擬/數字CMOS。該電路只需要5伏電源。請參考HI-8588-10,用于需要與ARINC輸入串聯的外部電阻

2024-01-04 11:54:35

描述HI-8591是一款單通道ARINC 429線路接收器,提供8引腳SOIC和12引腳LPCC(芯片級)兩種封裝。該產品采用模擬/數字CMOS技術設計,僅需要3.3V或5V單電源。此外,測試輸入

2024-01-04 10:21:53

小于確定延遲,具體取決于JESD204B通道的路由長度。接收器的緩沖器延遲有助于彌補路由造成的延遲差異。

問:JESD204B如何使用結束位?結束位存在的意義是什么?

答:JESD204B鏈路

2024-01-03 06:35:04

描述 AD6684是一款135 MHz帶寬、四通道中頻(IF)接收機。內置四個14位、500 MSPS ADC和各種數字處理模塊,包括四個寬帶DDC、一個NSR和VDR監控。該器件內置片內

2023-12-29 11:36:15

JESD79-5B DDR5 SDRAM-2022 JEDEC

2023-12-23 09:24:37

目前,我在設計中想使用ZYNQ 7015系列的FPGA,利用JESD204 IP核接收A/D轉換器AD9683轉換完成后的數據。但是JESD204 IP核的端口很多,我不知道應該如何將AD9683

2023-12-15 07:14:52

內。 對于某些接收器邏輯, 不需要這樣做 。

1. 通過外部PDWN針完全停電。

2. 芯片通過外部RESET針重新設置。

3. 通過釋放外部PDWN別針來回電源

用GTX接受測試數據CCAA

2023-12-13 09:17:30

目前我的板子上設計采用6通道AD7606,但是6通道AD7606目前代理商沒貨,查閱手冊發現,6通道實際上就是把8通道的兩個通道接地,所以想問,能否直接把8通道AD7606焊到6通道AD7606焊

2023-12-12 08:31:46

使用AD9680時遇到一個問題,AD9680采樣率為1Gsps,JESD204B IP核的GTX參考時鐘為250MHz,參數L=4,F=2,K=32,線速率為10Gbps,使用的為SYSREF

2023-12-12 08:03:49

我使用的是KC705板卡,調用了里面JESD204B的IP核,使用模式為interpolation值為4,4條鏈路,DAC頻率為2.5GHZ,通道速度為6.25GHZ,出現的問題是:

幀同步過程

2023-12-12 07:28:25

用單片AD9690采集數據給FPGA,不要求確定延遲,因此想要把AD9690配置在JESD204B sublcass 0 模式下。但是這種模式下,對于AD9690的SYSREF±的輸入管腳怎么處理?以及AD9690工作在subclass 0 模式下還有沒有其他要注意的地方?

2023-12-12 06:16:08

模數轉換器AD9625的評估板AD-FMCADC3-EBZ能不能和賽靈思的Virtex7系列FPGA開發板連接,我看到他們都具備JESD204B接口,物理接口上能直接連嗎?還是說需要在使用轉換接口來連接?

2023-12-08 08:25:12

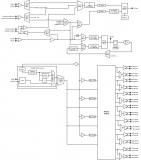

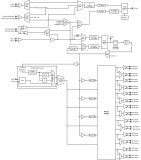

FPGA,使用了xilinx提供的JESD204B core,可以發送正弦波數據到DAC芯片。

目前的調試情況:根據手冊提供的配置流程配置AD9144,查詢相關寄存器,DAC PLL和Serdes PLL

2023-12-08 06:00:25

老是顯示錯誤如下:

root@analog:~# [15.459970] axi-jesd204-rx 84aa0000.axi-jesd204-rx: Lane 0 desynced

2023-12-07 07:09:20

8路時鐘用于產生JESD204B接口使用的時鐘,寄存器配置參考了AD9523-1開發板軟件,調試了好久沒有輸出,spi寄存器配置的時候使用了三點式和四線式,三點式的時候SDIO一直為低,他作為雙極

2023-12-06 07:48:32

的AD9162-FMX-EBZ板子,看到的現象是SYSREF信號一直為高,CGS測試信號不完全拉高,每次重新配置時拉高的lane通道數還不一樣。其界面設置如下圖所示。FPGA的使用是條用的xilinx的JESD204 IP核。

FPGA抓到的SYNC信號與SYSREF信號如下圖所示:

2023-12-05 08:23:30

使用內部PLL,輸入參考頻率為100MHz。在采樣率時鐘設置為1GHz時,DAC的JESD204B鏈路能建立,但是當頻率改為1.5GHz時,SYNC一直為低。其他相關寄存器都已經修改,serdes

2023-12-05 08:17:30

9680測試評估中遇到問題:

按照數據手冊中的配置步驟,關斷鏈路,通過0x570和0X56E寄存器快速配置JESD204B,鏈路上電后,電路鎖相環無法鎖定,204B無法正常輸出數據。

2023-12-05 08:04:26

Jesd 無法連接到的問題已經配置了 AD9173 。模式為 8, 主要的內插是 x12, 通道內插是 x1. DAC PLL 鎖定在 12GHz, 雙鏈接, L=4. 。 Reg0X281 中

2023-12-05 08:04:04

請問AD9625的寄存器需要如何設置才能打開時間戳的功能?

按照數據手冊我將寄存器0x072設置為0x8B,將0x08A設置為0x22.數據經過Xilinx FPGA的JESD204B IP核,但

2023-12-05 07:33:36

,0x00);

(d) sendcmdtoad9689(adcsel,0x1262,0x08);

(d) sendcmdtoad9689(adcsel,0x1262,0x00);

然后對JESD204B接收核

2023-12-05 07:30:47

我在使用AD9163的時候遇到JESD204B的SYNC信號周期性拉低。通過讀寄存器值如圖,發現REG470和REG471都為0xFF,而REG472始終為0.不知有誰知道是什么原因?該如何解

2023-12-04 07:30:17

AD9164 JESD204B接口的傳輸層是如何對I/Q數據進行映射的

2023-12-04 07:27:34

大佬好,小弟最近在調試AD9136芯片,遇到一個問題,如下:

1.我使用的是9136模式11,單鏈路模式,使用一個JESD204+一個JESD204 PHY,我將JESD204的tx_charisk

2023-12-04 07:14:58

廖世宏強調,「Mini LED 將席卷醫療業界,尤其高階手術」,目前友達推出 4 種不同尺寸的 Mini LED 面板,包括 21.5、23.8、27、32 吋,主要用在超音波診斷和手術,「超音波分非常多種類,有普通的、婦女用的,還有更高階的心臟超音波,Mini LED 能符合這些需求」。

2023-12-01 15:57:23 225

225 AD9144,AD9148,AD9177這三款芯片都是四通道輸出的芯片,請問這三款芯片的四通道輸出都可以四路同步輸出嗎?

2023-12-01 12:24:56

在AD9680和AD9690數據手冊上,寫著它們[size=200%]支持的最小通道線率是3125Mbps,但是在JESD204B標準手冊寫著最小通道線率是312.5Mbps。

我疑惑這是數據手冊的錯誤,還是AD9680和AD9690這兩款芯片支持的最低通道線率確實時3125Mbps

2023-12-01 07:57:58

我在使用ad2s1200+接收器(三階巴特沃斯濾波器電路)應用于電機控制時,遇到了如下圖模擬對話的IGBT干擾的幅度失配問題:

如上圖3通道紫色的信號所示,在電機供電電壓達到較高時(160v

2023-12-01 07:51:35

我們用的 AD9690-500,500M采樣速率, 想配置為全帶寬模式,2 Lanes, 為啥 ADC的輸出通道沒反應,K字符都不發送。請問這種配置模式需要寄存器如何配置? 出現這種問題可能的原因? 謝謝!

2023-12-01 07:13:46

前言YFC95066 是一款低功耗、高帶寬、14 位、500MSPS、四通道模數轉換器。YFC95066支持 JESD204B 串行接口,每個通道上具有 1 條信道,數據傳輸速率高達 10Gbps

2023-11-28 15:38:04

作者:Ian Beavers,ADI公司應用工程師 JESD204B串行數據鏈路接口針對支持更高速轉換器不斷增長的帶寬需求而開發。作為第三代標準,它提供更高的通道速率最大值(每通道高達12.5

2023-11-28 14:24:47 0

0 電子發燒友網站提供《JESD204B規范的傳輸層介紹.pdf》資料免費下載

2023-11-28 10:43:31 0

0 · AD9272 · AD9273

· AD9276 · AD9277

· AD9278 · AD9279

· AD9670 · AD9671

需要信號頻率1KHz-500KHz,由于存在高通,可能把需要的信號濾除了。

1可否屏蔽高通濾波器?

2可否調整到1kHz一下?

2023-11-22 07:01:53

前言TSW14J57EVM數據采集/圖形發生器:具有 16 個 JESD204B 通道 (1.6-15Gbps) 的數據轉換器 EVM提示:以下是本篇文章正文內容,下面案例可供參考一

2023-11-21 15:05:23

一、ADS54J66IRMPT 產品描述1.產品特性ADS54J66IRMPT 是一款低功耗、高帶寬、14 位、500MSPS、四通道電信接收器。ADS54J66 支持 JESD204B 串行接口

2023-11-21 14:29:58

描述 HI-8448是一款8通道ARINC 429線路接收器IC,采用44引腳塑料四方扁平封裝(PQFP)。每個獨立的接收器通道將輸入的ARINC 429數據總線信號轉換為相關的一對

2023-11-09 10:23:20

中電云腦企業總經理程龍龍表示,新一代八通道國產腦電采集芯片可與市面上現有的商用八通道采集芯片兼容,今年11月,2024年5月,epc芯片本身的研究,將正式應用于可穿戴便攜式機器,也會用于大規模商業化。

2023-10-30 10:19:10 432

432 飛利浦還改變了購買用于電腦斷層掃描和超音波機器的定制芯片的方式,他喜歡更貴但更新穎的芯片,以便在緊急情況下從多個地方購買。

2023-10-20 09:16:58 237

237 電子發燒友網為你提供ADI(ADI)AD9094: 8-Bit, 1 GSPS, JESD204B, Quad Analog-to-Digital Converter Data Sheet相關產品

2023-10-17 19:13:59

電子發燒友網為你提供ADI(ADI)AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet相關產品參數、數據手冊,更有AD9207

2023-10-16 19:02:55

Gb/s(1)的線路速率。有關支持的最大線路速率,請參閱器件數據表。 每個設備和系列都有不同的通道。JESD204內核可配置為發送或接收,并可使用多個內核來實現需要超過8個通道的鏈路。JESD204

2023-10-16 10:57:17 358

358

電子發燒友網為你提供ADI(ADI)AD9694-EP: 14比特、500 MSPS、JESD204B、“四向數字轉換器”強化產品數據表相關產品參數、數據手冊,更有AD9694-EP: 14比特

2023-10-09 19:12:15

電子發燒友網為你提供ADI(ADI)AD9694S: 14-Bit, 500 MSPS, JESD 204B, 二次對數字轉換器數據表相關產品參數、數據手冊,更有AD9694S: 14-Bit

2023-10-08 16:48:36

概述D74HC138D 是一種三通道輸入、八通道輸出譯碼器,主要應用于消費類電子產品。

2023-09-28 07:56:41

電子發燒友網站提供《74LVC573A八通道D型透明鎖存器手冊.pdf》資料免費下載

2023-09-27 11:25:02 0

0 包含代碼、詳細說明、物料表Diy arduino rc接收器和發射器,六通道強大功能!

2023-09-26 08:08:35

電子發燒友網站提供《一種基于JESD204B的射頻信號高速采集系統.pdf》資料免費下載

2023-09-14 11:14:07 1

1 AD9144是一款支持jesd204b協議高速DAC芯片。AD9144-FMC-EBZ是基于AD9144的評估板(Evaluation Board),它是主要由AD9144,AD9516,與PIC16F單片機組成的系統。

2023-09-13 09:20:22 996

996

該4通道混音器電路項目基于lm381低噪聲雙前置放大器IC。

為了給這個混音器電路電子項目供電,您可以使用直流電源電路(或電池),它將提供9到24伏之間的輸出電壓。

lm381 的兩個放大器中

2023-09-11 16:11:29

測距應用對許多創客而言并不陌生,例如紅外線測距、超音波測距等,但較少人使用雷射(對岸稱為激光)測距。近期有一名創客Hesam Moshiri就示范如何打造一個基本的雷射測距。

2023-08-24 16:10:58 484

484

多個通道采樣,用連續掃描模式,通道切換對采樣結果有影響嗎?

比如我一定時間內,一個個通道采集求平均和八通道輪詢求平均,哪個結果更準確?

2023-08-22 06:57:44

產品概況: SC6301是高性能時鐘調節器,支持JEDEC JESD204B。當使用設備和SYSREF時鐘時,PLL2的14個時鐘輸出可配置去驅動7

2023-07-25 17:06:53

本文旨在提供發生 JESD204B 鏈路中斷情況下的調試技巧簡介

2023-07-10 16:32:03 802

802

車載攝像頭總線(C2B)接收器,能夠通過差分對或單端電纜接收視頻數據和雙向控制數據ADV7382具有移動行業處理器接口(MIPI)攝像頭串行接口2 (CSI-2)變送器支持2通道運行

2023-07-06 15:09:51

MHz的均衡帶寬。AD8128既可以用作獨立的接收器/均衡器,也可以與三通道差分接收器AD8143配合使用,為通過UTP電纜接收RGB信號的應用(例如KVM)提供

2023-07-04 17:51:33

光纖接收器的單模和雙模是指其光纖傳輸模式的類型。下面是單模和雙模光纖接收器之間的主要區別:

2023-07-02 10:57:44 908

908 該芯片是高性能時鐘調節器,支持JEDEC JESD204B。當使用設備和 SYSREF 時鐘時,PLL2 的 14 個時鐘輸出可配置去驅動 7 個JESD204B 轉換器或其他邏輯設備。

2023-06-25 10:13:46 848

848 SC6301是高性能時鐘調節器,支持JEDEC JESD204B。當使用設備和SYSREF時鐘時,PLL2的14個時鐘輸出可配置去驅動7個JESD204B轉換器或其他邏輯設備。

2023-06-21 15:11:14 508

508

SC6301是高性能時鐘調節器,支持JEDEC JESD204B。當使用設備和SYSREF時鐘時,PLL2的14個時鐘輸出可配置去驅動7個JESD204B轉換器或其他邏輯設備。SYSREF可以使用直流和交流耦合來提供。不僅限于JESD204B應用,14個輸出均可單獨配置為傳統高性能時鐘系統輸出。

2023-06-21 15:10:58 608

608

SYSREF計時校準▲樣片標記時間戳■JESD204B串行數據接口:▲支持子類0和1▲最大通道速率:12.8Gbps▲多達16個通道可降低通道速率■雙通道模式下的數字下變頻器:▲實際輸出:DDC旁路或

2023-06-16 14:37:21

您的PCB可以處理高達12.5Gbps的速度嗎,感到驚訝,對嗎?JESD204B標準為串行接口提供高達12.5Gbps的比特率。這種升級允許設計人員在FPGA/ASIC上使用更少的收發器,從而減少

2023-05-26 14:50:57 608

608

JESD204B規范是JEDEC標準發布的較新版本,適用于數據轉換器和邏輯器件。如果您正在使用FPGA進行高速數據采集設計,您會聽到新的流行詞“JESD204B”。與LVDS和CMOS接口相比,這一較新的版本具有顯著的優勢,因為它包括更簡單的布局和更少的引腳數。

2023-05-26 14:49:31 361

361

? RFASK-問答廣場 ? Q: 多通道接收機系統調試通道之間底噪幅度不一致 pxffay提問:?? 一個八通道接收機,系統設計八邊形,每隔45度一個天線,不接天線時候八個通道接收機采樣解析

2023-05-26 09:47:20 440

440

大部分的ADC和DAC都支持子類1,JESD204B標準協議中子類1包括:傳輸層,鏈路層,物理層。在少部分資料中也會介紹含有應用層,應用層是對JESD204B進行配置的接口,在標準協議中是不含此層,只是為了便于理解,添加的一個層。

2023-05-10 15:52:55 1369

1369

一、產品簡介 MS5268 是一款 16bit 八通道輸出的電壓型 DAC,內部集成上電復位電路、可選內部基準、接口采用四線串口模式,最高工作頻率可以到

2023-05-07 18:44:33

可以給有需要的大俠提供一些參考學習作用。第一篇這里放個超鏈接:FPGA項目開發:基于JESD204B的LMK04821芯片項目開發經驗分享以后機會多多,慢慢分享一些項目開發以及學習方面的內容,歡迎各位

2023-04-20 16:59:00

LMK04821系列器件為該話題提供了很好的范例研究素材,因為它們是高性能的雙環路抖動清除器,可在具有器件和SYSREF時鐘的子類1時鐘方案里驅動多達七個JESD204B轉換器或邏輯器件。圖1是典型JESD204B系統(以LMK04821系列器件作為時鐘解決方案)的高級方框圖。

2023-04-18 09:25:30 915

915

4月12日,上海——納芯微電子(以下簡稱“納芯微”,科創板股票代碼688052)今日宣布推出單通道MLVDS收發器NLC530x系列,包括NLC5301/2/3/4共四款器件。其中NLC5301

2023-04-13 15:22:28

局域網 (CAN) 模塊? 三個通用異步/同步接收器/發送器? 兩個內部集成電路 ( I2C?) 總線接口模塊? 排隊串行外設接口 (QSPI) 模塊? 八通道 12 位快速模數轉換器 (ADC),同步

2023-03-31 08:49:25

JESD207 FOR LATTICEECP3

2023-03-30 12:02:10

JESD207 FOR LATTICEECP3

2023-03-30 12:01:20

0。對于單行數據輸出格式:幀可以設置為 256 位 I2S CFG2 寄存器中的 FRAMELEN 正好適用于 8 個通道 x 32 位。或者我們不能像這樣接收這些數據,因為對于每個 32 位數據包,我們需要有 I2S 通道?

2023-03-24 08:07:58

電子發燒友App

電子發燒友App

評論