旁路電容是可將混有高頻電流和低頻電流的交流電中的高頻成分旁路濾掉的電容。 對于同一個電路來說,旁路電容是把輸入信號中的高頻噪聲作為濾除對象,把前級攜帶的高頻雜波濾除,而去耦(也稱退耦)電容是把輸出信號的干擾作為濾除對象。

可將混有高頻電流和低頻電流的交流信號中的高頻成分旁路濾掉的電容,稱做“旁路電容”。旁路電容的主要功能是產生一個交流分路,從而消去進入易感區(qū)的那些不需要的能量,即當混有高頻和低頻的信號經過放大器被放大時,要求通過某一級時只允許低頻信號輸入到下一級,而不需要高頻信號進入,則在該級的輸入端加一個適當大小的接地電容,使較高頻率的信號很容易通過此電容被旁路掉(這是因為電容對高頻阻抗小),而低頻信號由于電容對它的阻抗較大而被輸送到下一級放大。

旁路電容不是理論概念,而是一個經常使用的實用方法,電子管或者晶體管是需要偏置的,就是決定工作點的直流供電條件。例如電子管的柵極相對于陰極往往要求加有負壓,為了在一個直流電源下工作,就在陰極對地串接一個電阻,利用板流形成陰極的對地正電位,而柵極直流接地,這種偏置技術叫做“自偏”,但是對(交流)信號而言,這同時又是一個負反饋,為了消除這個影響,就在這個電阻上并聯(lián)一個足夠大的電容,這就叫旁路電容。

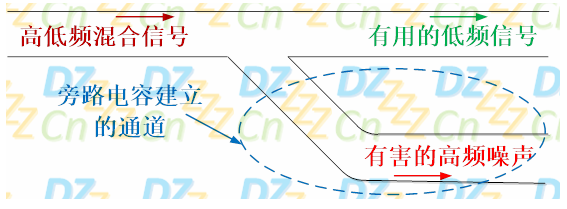

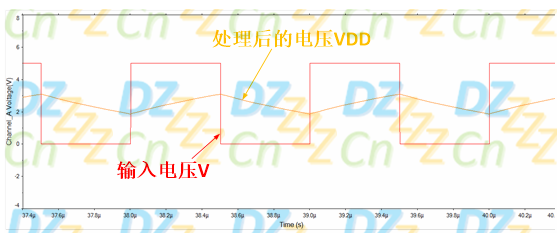

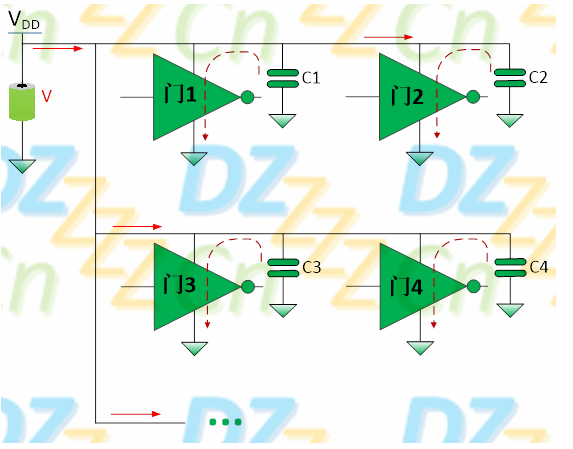

旁路電容(bypass capacitor)在高速數字邏輯電路中尤為常見,它的作用是在正常的通道(信號或電源,本文以電源旁路電容為例)旁邊建立另外一個對高頻噪聲成分阻抗比較低的通路,從而將高頻噪聲成分從有用的信號用濾除,也因此而得名,如下圖所示:

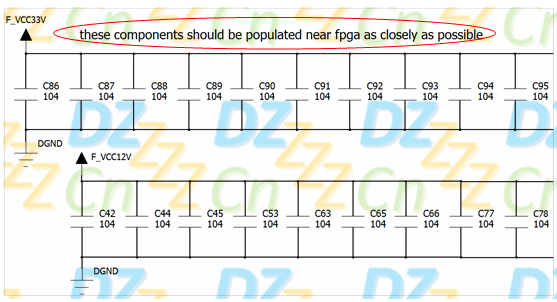

通常我們見到的旁路電容位置如下圖所示:

如果是高密度BGA(Ball Grid Array)封裝芯片,則旁路電容通常會放在PCB底層(芯片的正下方),這些旁路電容會使用過孔扇出(Fanout)后與芯片的電源與地引腳連接,如下圖所示:

更有甚者,很多高速處理器芯片(通常也是BGA封裝)在出廠時,已經將旁路電容貼在芯片上,如下圖所示:

臺式電腦的CPU(Central Processing Unit)一般都是用CPU插槽進行安裝,很多CPU芯片的背面(是芯片的背面,而不是貼芯片的PCB板背面)也會有很多旁路電容,如下圖所示:

總之,旁路電容的位置總是會與主芯片越來越靠近,原理圖設計工程師在進行電路設計時,也通常會將這些旁路電容的PCB LAYOUT要點標記起來,用來指導PCB布局布線工程師,如下圖所示:

那么這里就有兩個問題了:

(1)為什么旁路電容一定要與主芯片盡可能地靠近?

(2)為什么大多數旁路電容的值都是0.1uF(104)?這是巧合嗎?

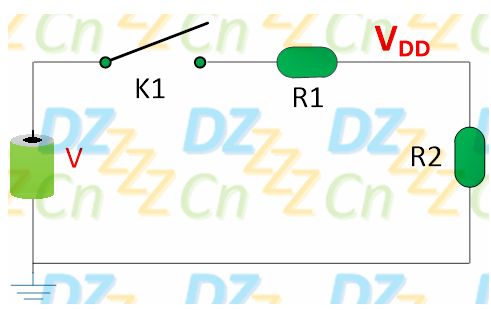

要講清楚這兩個問題,首先我們應該理解旁路電容存在的意義,很多人分不清濾波電容、旁路電容,其實本質上兩者是沒有任何區(qū)別,只不過在細節(jié)上對電容的要求有所不同。無論電容的應用場合名稱叫什么,基本的(也是共同的)一點特性總是不會變的:儲能。電容的這一特性使得外部供電電源有所波動時,與電容并聯(lián)的對象兩端的電壓所受的影響減小,如下圖所示:

上圖中,我們用開關K1來模擬擾動的來源,很明顯,每一次開關K1閉合或斷開時,在電阻R1與R2的分壓下,電阻R2兩端的電壓(VDD)都是會實時跟隨變化的(即波動很大),只不過電壓幅度不一致而已,我們認為開關的切換動作已經產生了電源噪聲。

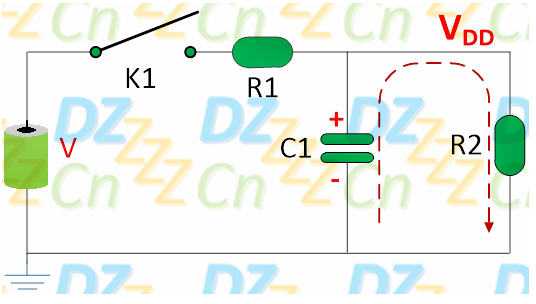

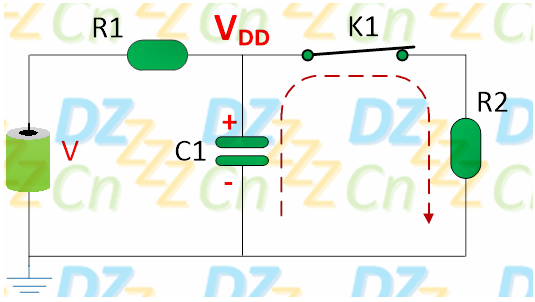

當我們在VDD節(jié)點與公共地之間并聯(lián)一個電容C1后,如下圖所示:

由于電容C1儲能的作用,開關K1在開/關切換時,電容的充放電行為會使VDD更加平緩一些,如下圖所示:

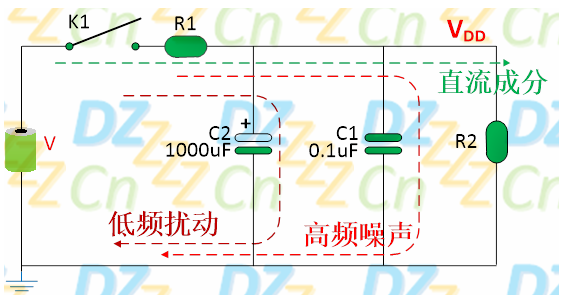

如果這個電容值比較大(一般在10uF以上,也有數千微法),我們就將其稱為濾波電容,它可以將低頻擾動成分濾除掉(但是對高頻成分不管用),如果這個電容值比較小(一般1uF以下),我們稱為旁路電容,它可以將高頻成分濾除掉(對低頻成分不管用),這兩種電容起的都是濾除作用,如下圖所示:

(本文以容值為濾波與旁路的區(qū)分僅限于數字電路,旨在說明兩者區(qū)別,僅供參考,因為在模擬電路中很多容值并不小的電容也算是旁路電容,比如基本放大電路中的發(fā)射極電阻兩端并聯(lián)的電容,但本質都是一樣的)

當然,我們也可以把模擬電源擾動開關K1放在如下圖所示的位置,同樣的道理,電容C1也可以在一定程度上削弱擾動對VDD帶來的影響:

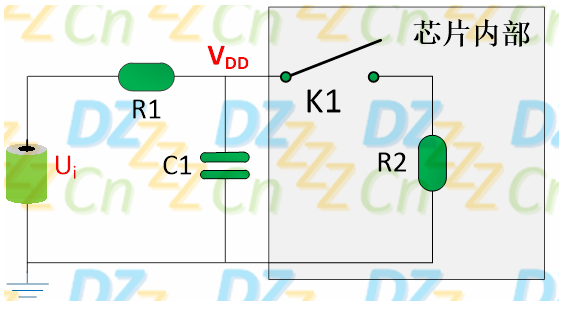

對于旁路電容的應用電路而言,開關K1與電阻R2為干擾的來源,我們可以把它們等效為芯片內部,如下圖所示:

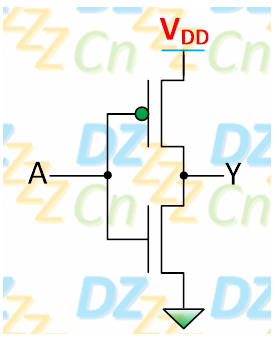

下面我們以74HC04(6反相器)芯片來分析一下,盡管電路規(guī)模很小,但原理都是一樣的。我們在《邏輯門》系列文章有提到過,CMOS反相器的基本結構如下圖所示:

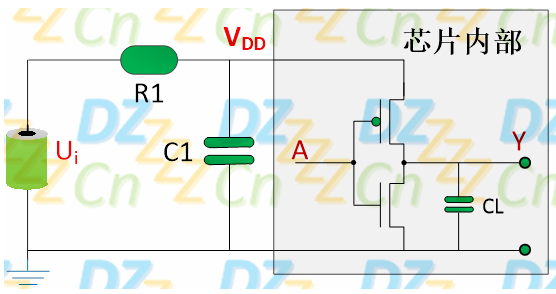

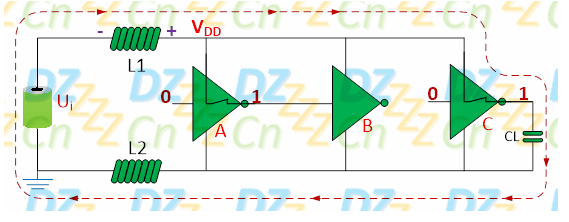

我們將這個反相器安裝到上面的電路中去,則有如下圖所示:

其中,電容CL為芯片內部等效負載電容,一般為幾個pF,是數字集成電路中客觀存在的,就算反相器輸出沒有連接額外的負載,芯片進行開關動作時也會消耗一定的電能(電荷)。

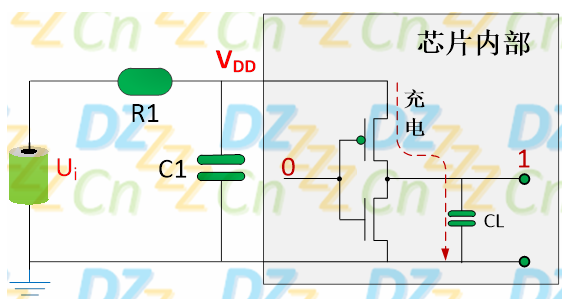

假設芯片邏輯輸入電平由高H至低L變化(由低L至高H變換也是一樣的道,本文不再贅述),PMOS(上側帶圈圈的)導通,NMOS截止,此時電流通路如下圖所示:

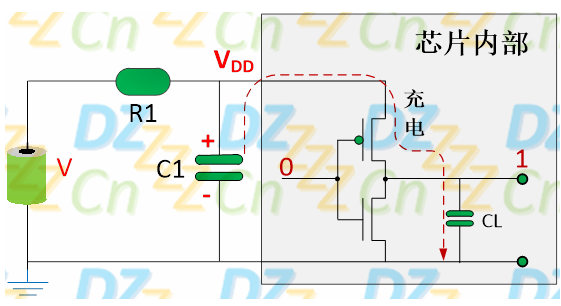

由于電容CL兩端的電壓不能突變,因此瞬間的充電電流(電荷)也不小,這個充電電流即來自于電源VDD,如果附近恰好有旁路電容,則由旁路電容中儲存的電荷提供此消耗,如下圖所示:

有人可能就說:就算旁路電容C1離芯片太遠或沒有,不是還有直流電源V提供VDD嗎?也應該可以承擔提供電能的責任呀?沒錯,當芯片產生的噪聲成分屬于低頻是完全可以的,但是數字電路處于高低電平切換時情況就完全不一樣了,因為開關的切換會產生諧波豐富的高頻成分。

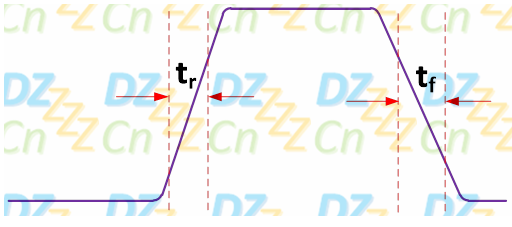

需要注意的是,這個諧波頻率成分的高低不是指信號的切換頻率,而取決于高低電平切換的上升或下降率,即上升時間tr(rising time)與下降時間tf(falling time),如下圖所示:

高低電平變換時間越短,則產生的諧波(高頻)成分越豐富,因此,低速開關并不意味著高頻成分少,信號頻率為1MHz方波存在的高頻諧波成分比同頻率正弦波要高得多,因為方波的高低電平切換時間非常短,而正弦波則相對非常緩慢。

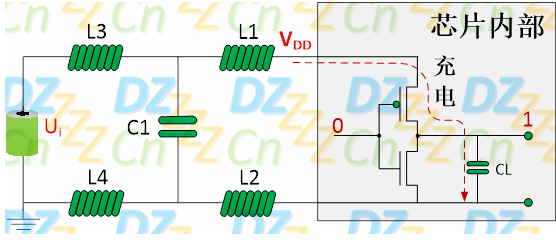

因此數字電路應使用下圖所示的高頻等效電路:

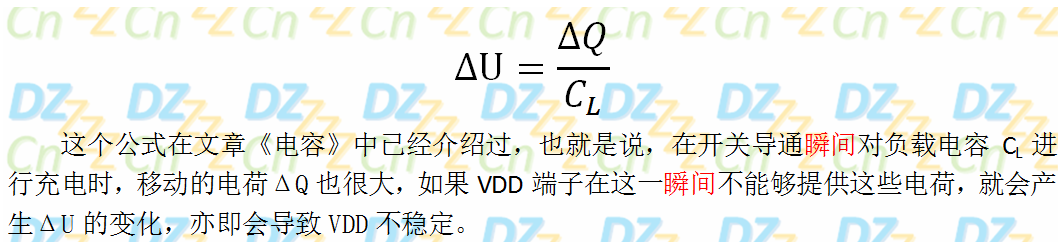

其中,L1、L2、L3、L4就是線路(包括過孔、引腳、走線)在高頻下的等效電感,線路越長則等效電感越大,這些等效電感對高頻信號相當于是高阻抗,這對于前級過來的高頻干擾的抑制是有好處的,但同時對芯片內部(后級)開關切換帶來的干擾也是有抑制作用的,這種抑制作用在旁路電容(或更遠的直流電源V)與芯片之間形成了阻礙,使得VDD供電端子無法及時獲取到足夠電荷繼而導致VDD瞬間下降(即變差),這種電壓變化可以由下式來表達:

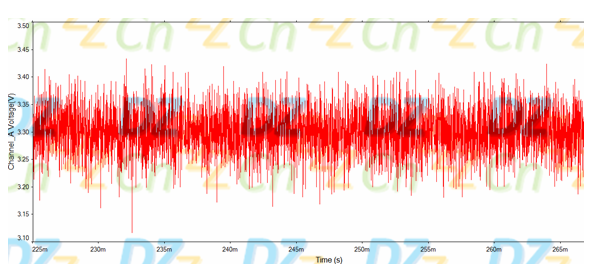

在大規(guī)模數字集成電路中會存在成千上萬個等效開關同時切換,這些切換產生的瞬間電流都將使原本看似平穩(wěn)的電源電壓不再干凈,繼而使得芯片工作不再穩(wěn)定,類似如下圖所示:

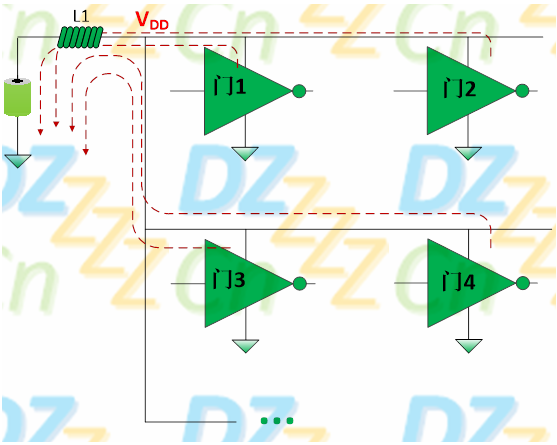

因此,通常我們會將旁路電容盡量地靠近芯片,這樣使得旁路電容與芯片之間的引腳或走線的分布電感越小,從而能保證芯片能夠及時獲取足夠的電荷。電路規(guī)模越大的芯片(如奔騰處理器),同一時間切換的邏輯會更多,因此也需要更多的電荷進行消耗電能的補充,外部需要并接的旁路電容也更多,如下圖所示:

旁路電容所起的作用與現實生活中的撲滅小火災的水龍頭一樣:假設家里出現了小火災(相當于高頻電源擾動),反應最快的肯定是從家里的水源處(相當于旁路電容)取水來撲滅,而不是第一時間拔打119電話。119火警撲滅火災的能力(相當于外部電源V)肯定是最強的,它對于大火災(相當于低頻電源擾動)是最合適的,但是對于頻繁出現的小火災幾乎沒有什么用處,反應時間跟不上,等你趕過來時什么都燒完了(電路工作出現異常),還是家里的水龍頭管用,雖然水源比較小,但對于小火災卻是足夠用了。

有人可能就會說:搞那么麻煩做什么,為什么要并聯(lián)這么多小電容?不就是那么些個儲能電容,我在附近并聯(lián)10 uF或100uF的電容不就都解決了么?以一個抵千百個,PCB布局布線更簡單,么么噠!理想很豐滿,現實很骨感。從單純的儲能角度來講,是沒有什么問題的!但旁路電容還有另外的重要功能:為每個高頻信號提供良好的低阻抗返回路徑,從而控制信號之間的串擾。

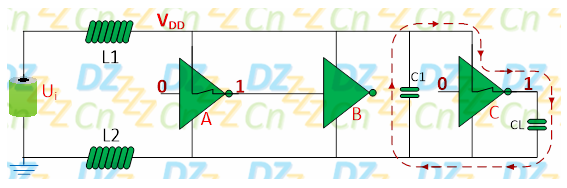

如下圖所示,在門C的輸出切換為高電平時,電池電源V將對負載電容CL充電,這個電流回路將產生瞬間的噪聲電壓(用L1、L2等效),如果同一時間門A的輸出也切換為高電平,則門C產生的噪聲電壓將疊加在VDD上,從而影響到輸出電平。

也就是說,其它門的噪聲電壓(也稱為共路噪聲)被傳遞到門A的輸出端,同一時間邏輯切換越多則產生的共路噪聲越大,一旦疊加在VDD上的共路噪聲超過芯片的噪聲容限,電路因無法有效地判斷高低電平而導致異常,如下圖所示:

為了改善這種共路噪聲帶來的影響,我們可以在每個芯片附近放置合適容值的旁路電容,由旁路電容建立電源與地之間的低阻抗回路,這樣高頻噪聲就不會影響到其它門的正常工作,如下圖所示:

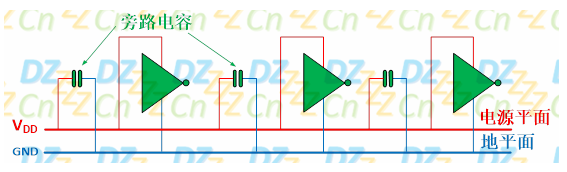

在實際應用中,我們會使用電源平面與地平面(減小分布電感,這些屬于高速PCB設計內容,我們將在系列專欄文章中進行詳細講解),并配合旁路電容來為每一個芯片提供良好的低阻抗回路,如下圖所示:

但我們在文章《電容》已經介紹過,實際的電容都有其自諧振頻率,電容在高于自諧振頻率時等效為一個電感,亦即不再是個電容了。我們也計算過10uF貼片陶瓷電容的自諧振頻率約為1.6MHz,假設我們的芯片工作在10MHz(諧波頻率成分甚至會達100MHz以上),此時并聯(lián)10uF的電容相當于是不存在的(對于高頻噪聲成分相當于是開路的),因此,旁路電容的容量過大將起不到高頻旁路的作用,另外,并聯(lián)多個小電容的也可以在達到前述兩個功能的前提下提升總電容的自諧振頻率,這一點可以參考文章《電容》

作為旁路電容的容值一般不會大于1uF(以文章《電容》中所示1nH ESL計算其自諧振頻率約為5MHZ,同類型電容的容量越小則自諧振頻率越高),那旁路電容應該至少需要多少呢?我們下一節(jié)結合數據手冊定量計算一下0.1uF容值的由來。