集成電路(integrated circuit)是一種微型電子器件或部件。采用一定的工藝,把一個電路中所需的晶體管、電阻、電容和電感等元件及布線互連一起,制作在一小塊或幾小塊半導體晶片或介質基片上,然后封裝在一個管殼內,成為具有所需電路功能的微型結構;其中所有元件在結構上已組成一個整體,使電子元件向著微小型化、低功耗、智能化和高可靠性方面邁進了一大步。它在電路中用字母“IC”表示。集成電路發明者為杰克·基爾比(基于鍺(Ge)的集成電路)和羅伯特·諾伊思(基于硅(Si)的集成電路)。當今半導體工業大多數應用的是基于硅的集成電路。

是20世紀50年代后期一60年代發展起來的一種新型半導體器件。它是經過氧化、光刻、擴散、外延、蒸鋁等半導體制造工藝,把構成具有一定功能的電路所需的半導體、電阻、電容等元件及它們之間的連接導線全部集成在一小塊硅片上,然后焊接封裝在一個管殼內的電子器件。其封裝外殼有圓殼式、扁平式或雙列直插式等多種形式。集成電路技術包括芯片制造技術與設計技術,主要體現在加工設備,加工工藝,封裝測試,批量生產及設計創新的能力上。

怎么降低集成電路的功耗

功耗:功率的損耗。指設備,器件等輸入功率和輸出功率的差額。

功耗一般分為兩種,來自開關的動態功耗(電容充放電),和來自漏電的靜態功耗。

1、使用MOS管門電路,盡量少使用TTL門電路。

2、給電路設置休眠,待機狀態,能夠進入省電模式。

3、將電路設計最簡化。模塊分布合理,減少布線。

4、降低工作頻率。

SOC低功耗設計

動態功耗管理的思想是有選擇的將不被調用的模塊掛起,從而降低功耗。

靜態功耗管理是檢測的整個系統的工作狀態,而不是針對某個模塊,如果系統在一段時間內一直處于空閑狀態,則靜態功耗管理就會把整個芯片掛起,系統進入睡眠狀態,以減少功耗

軟件代碼優化:

使用算法盡量簡單。訪問寄存器比訪問內存用的功耗少,合理利用寄存器較少對內存的訪問。

低功耗設計的主要方法:

1、并行結構,可以降低工作頻率,同時電源電壓可以降低。

2、流水結構,插入寄存器降低組合路徑的長度,達到降低功耗的目的。

3、編碼優化,采用獨熱碼,格雷碼,降低功耗,較少信號的跳變次數。

4、門控時鐘

5、存儲分區訪問,只有被訪問的存儲器工作,其它存儲器不工作

如何最大程度降低未來集成電路的功耗,詳細操作步驟

功耗過高已經成為半導體工藝尺寸進一步微縮的主要障礙,并且嚴重威脅到所有電子領域的一切進展──從推動移動設備更加微型化到開發超級電腦均包含在內。

雖然根本原因在于永恒不變的物理和化學原理,但工程師們已經開發出一系列的創新技術,以用于減輕目前所面臨的問題,并可望對振興未來的芯片產業有所助益。

以下討論五種可用于降低未來IC功耗的技術。這些技術目前已經在開發中,可望共同解決未來十年內將會面臨的功耗問題。

擁抱協同設計

電子設計自動化(EDA)工具可讓設計團隊從一開始就進行協同設計,從而實現最佳化低功耗設計。事實上,業界最低功耗的處理器和系統級芯片開發人員不僅透過最佳化架構和材料來實現優勢,也采用協同設計封裝、電源、射頻電路和軟件來降低功耗,而不至于降低性能或增加成本。

“實現低功耗必須采用覆蓋技術、設計方法、芯片架構和軟件的全面性方法。”德州儀器(TI)公司設計技術與EDA部門總監David Greenhill表示。

TI已經使用了許多先進技術為每個子系統進行最佳化,從而為低功耗元件提升了新標準,例如打造自有的制程技術來平衡關斷模式的漏電流與主動電流性能,或使用電壓與頻率擴展技術來定義各種省電工作模式。

“第一步是從性能和功耗的觀點來確認產品的目標。一旦這些目標確定后,就可以開始采用專用的制程技術,以提供所需的性能,而不至于超出設備的功耗預算。” TI公司28nm平臺經理Randy Hollingsworth指出。

EDA工具一直是實現這些更低功耗目標的關鍵,但有時需要圍繞設計回路進行一些反覆,因為采用傳統EDA工具進行功耗估計只在接近設計周期結束時才比較精確。對于未來的IC來說,必須在設計周期初期便進行精確的功耗估算。

一些專用工具的供應商已經拾起了接力棒。例如美國加州Atrenta公司推出一款名為Spyglass Power的工具,它可采用標準的暫存器傳輸級(RTL)描述來執行功耗估計、功耗降低與驗證。這些RTL描述在較早的設計周期就能從每種主要EDA工具獲得。

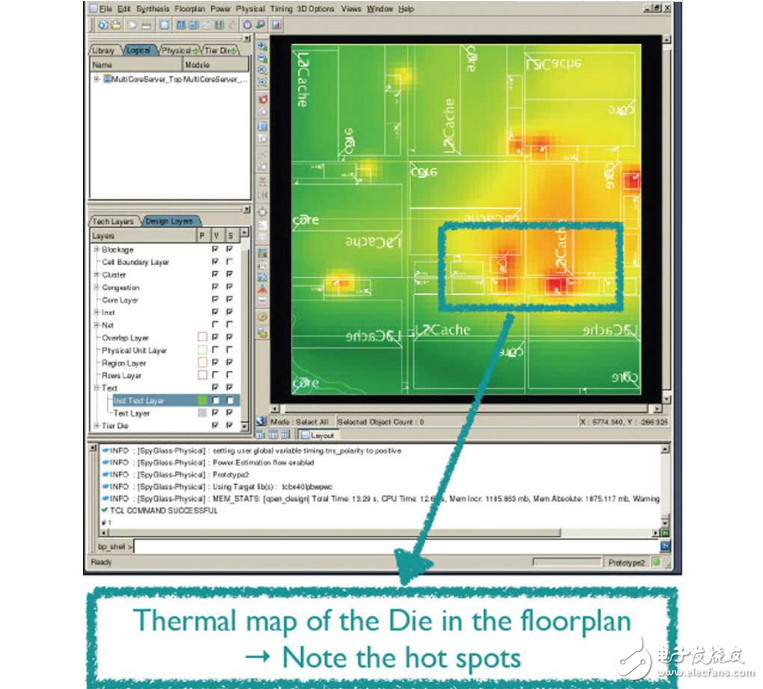

圖1:Atrenta公司的工具可以很早就估計功耗;此處指出設計周期開始之初的潛在熱點。

圖片來源:Atrenta公司

“而今,工程師希望能在較早的設計周期展開功耗估計。”Atrenta公司資深工程總監Peter Suaris表示,“你不能再等到設計臨近結束時才去估計功耗。你必須在RTL級就針對功耗進行協同設計,并為設計進行改動,以便能從一開始就實現節能效果。”

Atrenta公司宣稱,其專用的節能工具能以20%以內的精密度估計最終功耗預算,而功耗降低工具還可使最終設計功耗減少達50%。

降低工作電壓

微縮芯片尺寸通常能夠降低工作電壓,從而實現節能。例如,三星公司(Samsung)最新的20nm‘綠色存儲器’芯片透過將工作電壓從1.5V降低至1.35V,以節省67%的功耗。

處理器和邏輯電路的工作電壓甚至低于存儲器元年,但工作電壓降低至1V以下時就不可避免地必須進一步改善半導體制程。IBM、英特爾(Intel)、三星、TI、臺積電(TSMC)和其他每家半導體制造商均持續改善制程,以便能在更低電壓下作業,不過,過去幾個制程世代以來的進展速度已開始減緩。

其關鍵在于晶體管導通的閾值電壓在使用不同晶圓時是不一致的,因為在更大尺寸時制程的變化可以忽略。而由于在特定電壓下關斷狀態的漏電流在不同閾值時有很大的變化,因此理想芯片實際上要使用根據其特性定制的供電電壓。

英特爾公司聲稱已具有更好的解決方案──這是該公司花費近十年時間進行完善的一種方案。英特爾采用了所謂三柵極(tri-gate)的3D FinFET晶體管架構,這種架構以三維方式在晶體管通道周圍環繞三個金屬柵極,使晶體管處于這些柵極的電場之下。這種技術可以抵銷阻止工作電壓低于1V的制程變化。

“我們已經成功地展示我們的三柵極晶體管結構,可將工作電壓減少到0.7V范圍,而且還能做得更低。”英特爾公司資深工程師Mark Bohr指出,“這些都是具有更陡峭次閾值斜率的完全耗盡型晶體管,可以更小的漏電流更快切斷,同時以更低閾值導通電壓。”

資金雄厚的半導體制造商們專注于模擬英特爾公司的3D架構,但一些新創企業則致力于研發新型平面制程,針對缺乏時間和資金來完善3D架構的半導體制造商重啟電壓調整進程。例如SuVolta公司已經發明出一種用于標準CMOS產品線的超低電壓平面制程。

圖2:透過采用未摻雜晶體管通道(位于中間的白色區域,在淺綠色的輕摻雜閾值區以及深綠色的重摻雜篩選區上方),SuVolta公司的平面CMOS制程可望使半導體電壓進一步降低。

來源:SuVolta公司

SuVolta并未使用3D柵極耗盡型晶體管,改而采用一種未摻雜通道(帶摻雜的閾值和保護帶)以避免摻雜中的變化。深度耗盡型通道制程可在標準的平面CMOS產品線上實現。

“透過使用平面深度耗盡型通道制程,我們已成功展示供電電壓可降低到0.6V,未來還能夠降得更低。”SuVolta公司技術長Scott Thompson透露。

SuVolta還取得了第一個授權協議──富士通半導體,該公司將在今年稍晚進行量產。有關該重要授權交易的進一步聲明可望在2012年稍晚發布。

智能調節功能

一般來說,供電電壓和時脈速度越低,功耗就越低。然而性能也受到影響。因此,最新的微控制器和SoC開始尋求運用智慧電源管理單元,自動調整工作電壓與時脈速度來搭配工作負載。

“電源管理的基本思路是單獨立地調整芯片不同部份的供電電壓和時脈速度,以便在任何特定時間點都能匹配其工作負載,同時關閉未使用的電路。”即將接任Silicon Laboratories公司CEO的Tyson Tuttle表示。

電源管理單元通常以狀態機模組的方式建置,能夠選擇性地降低非關鍵功能的電壓和頻率。但隨著半導體節點變得更先進,芯片中填入更多的晶體管,一種所謂“暗場硅晶”(dark silicon)的概念──大部份的芯片在需要使用以前均處于斷電狀態──這或許會是未來半導體的先驅設計理念。

“在未來更先進的制程節點,如22nm,SoC將整合進更多能同時導通的晶體管。”Rambus公司CTO Ely Tsern表示,“暗硅的概念就是在芯片上制作許多特殊用途的功能,但在任何時刻都只啟動所需的功能,讓其它功能則保持黑暗的斷電狀態,什么事也不做。”

英特爾在芯片電源管理方面處于領先地位,能夠隨時時詳細地監視核心的溫度,允許透過提升頻率(turbo模式)以提高性能或降低速度來節省功耗。

圖3:英特爾的turbo模式可在高負載期間提升時脈以增加速度,并監控核心溫度,在開始過熱時逐漸降低時脈速度。

來源:英特爾

但并不是所有的電源管理功能都能十分經濟地移植到芯片上。事實上,最智慧化的電源管理方案是在芯片上和外部電源管理單元之間劃分任務。“針對外部電源管理存在經常性的需求,因為從功率密度來說,能夠加進芯片上的內容是有限的。”Enpirion公司CTO兼共同創辦人Ashraf Lotfi表示。

Enpirion公司專門生產獨立式電源管理單元,這些電源管理單元能從處理器接收命令,例如當處理器進入睡眠模式時降低處理器的電壓,當處理器被喚醒時再迅速恢復電壓。

采用3D/光學互連

透過縮短互連線的長度并降低其電線,就能支援更小的驅動器晶體管,從而降低IC的功耗。縮短互連線長度的傳統方法是增加金屬層,因此目前有些芯片的金屬層多達10層。

然而,互連層設計最新創新成果是三維過孔硅( TSV ),允許將存儲器芯片堆疊在處理器之上。這種技術將互連長度減少到芯片間的距離,因此不需要大功耗的驅動晶體管和長的印刷電路板互連線。然而,TSV的經濟性比較差,目前大多數芯片制造商的TSV時程都處于延后狀態。

“雖然過孔硅(TSV)確實可透過縮短走線長度來降低功耗,但這是一種成本非常高的解決方案。”TI公司的Greenhill表示,“為了更具經濟性,TSV需要能夠彌補其它不足(如介面性能),才能讓它的成本較為合理。”

賽靈思公司(Xilinx nc.)是一家非常了解如何為TSV成本/性能取得平衡的公司,該公司正提供第一款使用TSV的商用芯片。相較于在PCB板上焊接獨立元件的方式,賽靈思公司采用這種具成本效益的方案不僅能降低芯片功耗,同時也提升了性能。此外,它還可為賽靈思公司的客戶降低BOM成本,賽靈思公司資深總監Ephrem Wu表示。

賽靈思公司透過使用硅中介層(interposer)回避了在PCB板上焊接各個FPGA的問題。這種硅中介層可在單一封裝內互連4個高密度的FPGA。

圖4:賽靈思公司能夠使用臺積電的硅插入器在封裝內互連4個FPGA,從而使功耗從112W降低到19W。

來源:賽靈思

這種技術不僅能提升性能,還能使功耗降低到19W,相形之下,傳統的PCB解決方案功耗還高達112W。另外一種前端技術是使用光學收發器。例如,IBM公司的Power7超級電腦使用從傳統光學元件產生的板載光子互連。未來的芯片很可能使用Kotura公司和其它公司提供的專用光學解決方案,將光子功能轉移到能夠附加處理器與存儲器芯片的微型光學芯片上。

“我們的低功耗硅鍺元件整合了透鏡、濾波器、調制器以及你需要的所有其它光學元件于單顆芯片上。”Kotura公司行銷副總裁Arlon Martin指出。

Kotura公司的硅光子制程使其得以將大約香煙盒大小約1萬美元的傳統光學收發器單元整合進最新款iPhone大小的500美元封裝中,使用的功耗更低4至20倍。Kotura公司還展示該公司的SiGe收發器可透過堆疊式CMOS芯片間的氣隙傳送光學訊號,最終在堆疊芯片之間形成一個高速、低功耗的光學資料通道,適用于代替PCB走線。

試用新材料

采用更高遷移率的材料也能降低功耗。例如在標準CMOS產品線中已經加進了磁性材料,而像碳納米管和石墨烯等‘神奇’的材料也開始浮出臺面。

為了以鐵電RAM(FRAM)制造嵌入式微控制器,TI在CMOS產品線中增加了磁性材料。從Ramtron International公司獲得授權的FRAM比起快閃存儲器更方便,因為它們既具有非揮發性,還支援隨機存取。

“與閃存相較,我們非揮發性的FRAM在讀寫能耗方面更高效。”TI無線事業部CTO Baher Haroun指出。

Enpirion公司也在其CMOS產品線中導入磁性材料,并計劃于2012年開始為其電源管理芯片制造整合型電感與變壓器。目前,電感和變壓器還無法更經濟地整合在必須于高頻作業的芯片上,但Enpirion公司專有的磁性材料已經著眼于解決這方面的問題。

“我們已經整合了不同的金屬合金,使我們的磁性材料可在很高的頻率下執行作業,同時還能保持高能效。”Enpirion公司的Lotfi透露。

圖5:Enpirion公司的芯片上電感是采用專用制程以及獨特的磁合金材料在硅晶圓上制造而成的。

與此同時,Semiconductor Research公司最近資助了IBM和美國哥倫比亞大學共同進行的一項研究計劃──將電感整合于處理器上。該公司聲稱能透過芯片穩壓功能在奈秒級時間內調節供電電壓,實現工作負載匹配,因而使能耗降幅高達20%。

在不遠的將來,CMOS產品線還可能增加的其它近期材料包括砷化銦鎵(InGaAs)。英特爾公司計劃使用InGaAs增強未來三柵極晶體管上的通道,據稱此舉可望使工作電壓降低至0.5V。

然而,長期來看,碳納米管和平面版的石墨烯很可能成為未來超低功耗元件的首選材料。

在喬治亞理工學院(Georgia Tech)的實驗室中,已經證明石墨烯的互連性能超過銅。IBM公司也已經展示使用碳納米管或石墨烯材料,可制造出低功耗、超高速的晶體管。TI最近則展示石墨烯可望在晶圓級制造出來。

英特爾公司針對以碳材料實現更高電遷移率方面進行研究,但其結論則是這些材料的商用時機未到。

“使用納米碳或石墨烯的碳互連結構具有非常吸引人的特性。”英特爾公司的Bohr指出,“不過,盡管大體積材料具有更低電阻,連接路徑的電阻卻不低。不過這是一種非常具有前景的材料,因此我希望在今后幾年能夠見到更多的業界相關研究。”