十四、傳輸門

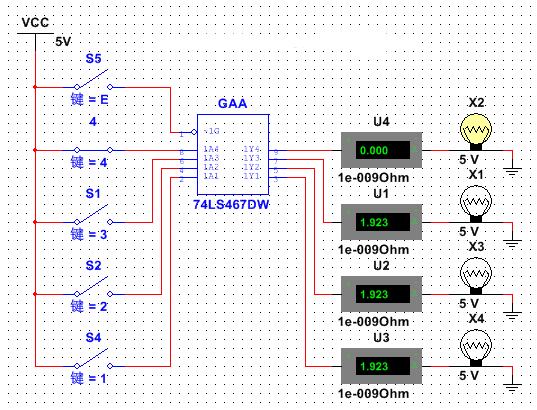

下圖所示的傳輸門的作用是:當左邊的“~1G”端輸入為0時,左側的1A4、1A3、1A2、1A1會直接傳輸到右側對應的1Y*,就像一條線直接從1A*連接到1Y*一樣;當左邊的“~1G”端輸入為1時,左側的1A4、1A3、1A2、1A1都不能傳輸到右側對應的1Y*,就像從1A*到1Y*的連線被剪斷了一樣。

注:本文里我做的電路圖片都是GIF格式的,你可以在瀏覽器里看到隨著開關的開閉,輸入和輸出電路上的燈泡是如何變化的。每個圖上都有(http://bitzhuwei.cnblogs.com)標識我的博客地址,不過每個GIF圖的最后一幀都去掉了這個標識。這樣,看到一幀沒有標識的時候,就知道下一幀將是GIF圖的第一幀了。

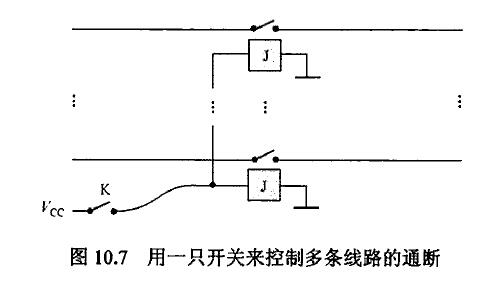

傳輸門的原理很簡單,就是在每個1A*到1Y*之間的連線上放個繼電器而已,如下圖所示。(取自《穿》)

十五、寄存器

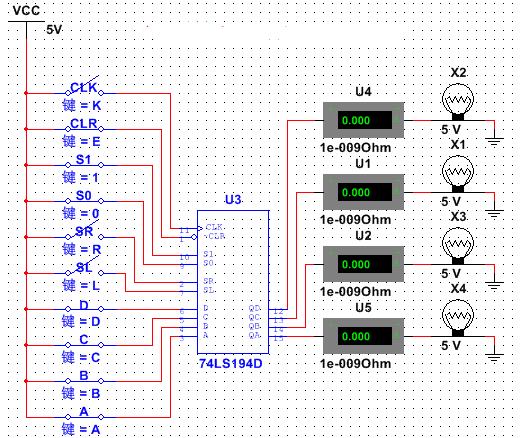

在上一篇已經說明了寄存器的原理,這里僅僅是為了說明“74LS194”這個帶有各種無聊管腳的四位寄存器的用法。將“~CLR”、“S1”和“S0”置為1,“SR”和“SL”置為0,然后,“74LS194”就是一個簡單的四位寄存器了。(本人在multisim12.0里只找到了這個靠譜的四位寄存器,湊合用吧。)

十六、數值顯示器

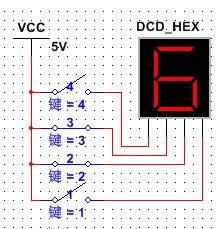

為了更直觀地看到CPU的運算結果,我們將使用“DCD_HEX”這個東西。它能夠把輸入的“0101”顯示為“5”,把“1010”顯示為“A”。

本文還要用一個四位的加法器,直接在下面這個簡陋的CPU里看就好了,不再單獨展示。

十七、回到頂部(go to top)

一個簡陋的CPU現在一切就緒,可以開始設計CPU了!

CPU包括運算器和控制器兩部分。我們首先做出運算器,然后逐步實現控制器,最后感受一下用機器語言編程的過程。本文實現的CPU雖然功能及其簡陋,但是能夠傳達出當前真實CPU的原理。

十八、運算器和手動控制器

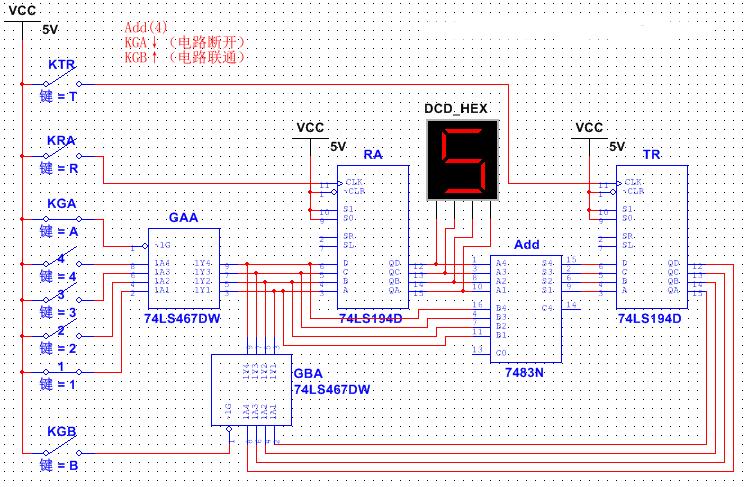

現在我們要做的這個CPU,字長是4位,只能做兩個數的加法。實現了運算器和手動版的控制器的CPU如下圖所示。我們把這個版本稱為version1的CPU。

上圖中,“Add”是加法器,能執行兩個4位數的加法運算。“RA”和“TR”是寄存器,“GAA”和“GBA”是傳輸門。“4”“3”“2”“1”用來準備需要相加的數據(0到15),“KTR”“KRA”“KGA”“KGB”是用來控制傳輸門通斷和寄存器脈沖的開關。

在上圖所示的GIF動畫中,顯示了“5+1+2+4”這個過程。這個過程可以分為4個步驟:①加載一個數值(Load);②加上一個數值(Add);③加上一個數值(Add);④加上一個數值(Add)。具體來說,每一個步驟要做的事情是:

十九、指令內容

加載一個數(Load)準備數據(0101); KGB↓, KGA↑; KRA↓↑

加一個數(Add)準備數據(0001); KGB↓, KGA↑; KTR↓↑; KGA↓, KGB↑; KRA↓↑

加一個數(Add)準備數據(0002); KGB↓, KGA↑; KTR↓↑; KGA↓, KGB↑; KRA↓↑

加一個數(Add)準備數據(0004); KGB↓, KGA↑; KTR↓↑; KGA↓, KGB↑; KRA↓↑

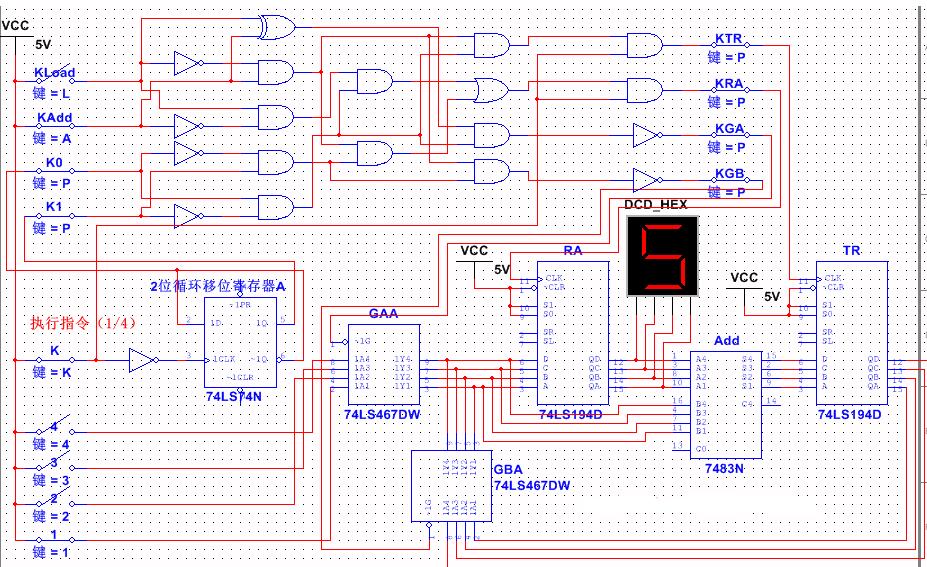

你可以看到,每次執行(Add)這一步,要做的事情(搬動開關)是一樣的,規律性極強。這意味著可以用簡化的方式控制“KTR”“KRA”“KGA”“KGB”這幾個開關的狀態。經過簡化的CPU就有一定的自動化控制的性質了,如下圖所示。我們把這個版本的CPU稱為version2的CPU。

Verison2要比剛才的verison1進化了一些。為便于理解,我們保留原來的“KTR”“KRA”“KGA”“KGB”這四個開關(把它們挪到了右上角,因為實在沒地方放了),但讓它們永遠保持閉合的狀態。這是想說明:version2里新增的電路只是實現了更加自動化地控制“KTR”“KRA”“KGA”“KGB”的開閉,它沒有改變version1中電路的工作流程。

Version2中的“KLoad”和“KAdd”開關分別代表了“Load”和“Add”這兩個指令。當“KLoad”閉合時,表示CPU要進行加載操作,這會把“4”“3”“2”“1”上的數據存入寄存器“RA”;當“KAdd”閉合時,表示CPU要進行相加操作,這會把“4”“3”“2”“1”上的數據與“RA”當前的數據相加,然后相加的結果又存儲到“RA”。

Version2中的“K0”和“K1”兩個開關會依次的開閉,即兩者總有一個是斷開且另一個是閉合的(若出現其它情況那就是電路設計錯了)。所以實際上“K0”和“K1”可以用一個“2位循環移位寄存器”代替。(為便于理解,仍然保留“K0”和“K1”這兩個開關,只不過讓它們永遠保持閉合的狀態)

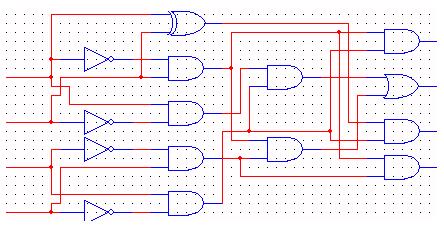

Version2中,只需重復“準備指令,準備數據,執行指令(K↓↑↓↑)”這樣的操作,就能完成version1中的控制功能。這需要一個從“KLoad”“KAdd”“K0”“K1”到“KTR”“KRA”“KGA”“KGB”的轉換電路,即version2電路圖中的上半部分,如下圖所示。

這需要一點點設計邏輯電路的知識,本文直接列出真值表,據此即可畫出轉換電路。(想知道如何推導的話,請查閱《穿》或者數字電路類書籍)

KloadKaddK0K1KGAKRAKTRKGB

10101100

01101010

01010101

其中“KLoad”“KAdd”“K0”“K1”為輸入,“KTR”“KRA”“KGA”“KGB”為輸出。只有如上三種輸入情況下,輸出部分會有1;其它的輸入情況下,輸出全部為0,所以就不需要列出來了。

舉個例子,“KGA”=“KLoad”“~KAdd”“K0”“~K1” + “~KLoad”“KAdd”“K0”“~K1”=(“KLoad” ⊕“KAdd”)“K0”“~K1”,據此可以畫出“KGA”的轉換電路。

在version2中,CPU要做的就是重復“準備指令,準備數據,執行指令(K↓↑↓↑)”這件事。其中執行指令這一步是完全重復完全自動化的(只要用振蕩器替換K就可以),而準備指令和準備數據還需要手工操作。每次要執行哪個指令、要準備的數據是多少,這都是沒有規律的,可改進的方法就是:把指令和數據按順序保存到一些特別的寄存器里,需要的時候取出來用。這些特別的寄存器,就是內存。