采用90nm工藝制造的DDR3 SDRAM存儲器架構支持總線速率為600 Mbps-1.6 Gbps (300-800 MHz)的高帶寬,工作電壓低至1.5V,因此功耗小,存儲密度更可高達2Gbits。該架構無疑速度更快,容量更大,單位比特的功耗更低,但問題是如何實現DDR3 SDRAM DIMM與FPGA的接口呢?

關鍵詞——均衡!

如果沒有將均衡功能直接設計到FPGA I/O架構中,那么任何設備連接到DDR3 SDRAM DIMM都將是復雜的,而且成本還高,需要大量的外部元器件,包括延時線和相關的控制。

什么是均衡?為什么如此重要?

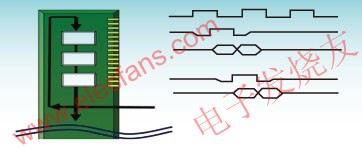

為了在支持更高頻率時提高信號完整性,JEDEC委員會定義了一個fly-by(飛越式)端接方案,該方案采用了時鐘和命令/地址總線信號來改善信號完整性以支持更高的性能。當時鐘和地址/命令通過DIMM時,fly-by拓撲結構通過故意引起每個DRAM上的時鐘和數據/選通之間的飛行時間偏移(flight-time skew)來減小并發開關噪聲(SNN),如圖1所示。

飛行時間偏移可能高達0.8 tCK,當該偏移被擴展得足夠寬時,將不知道數據在兩個時鐘周期中的哪個內返回。因此,均衡功能可以使控制器通過調節每個字節通道內的時序來補償這一偏移。最新的FPGA能夠為各種應用提供與雙倍數據率SDRAM存儲器接口的許多功能。但是,要與最新的DDR3 SDRAM一道使用,還需要更魯棒的均衡方案。

FPGA I/O結構

像Altera Stratix III系列高性能FPGA提供的I/O速度高達400 MHz (800 Mbps),還具有很高的靈活性,能夠支持現有的和新興的外部存儲器標準,如DDR3。

圖1:DDR3 SDRAM DIMM:飛行時間偏移降低了SSN,數據必須被控制器調高到兩個時鐘周期。

讀均衡

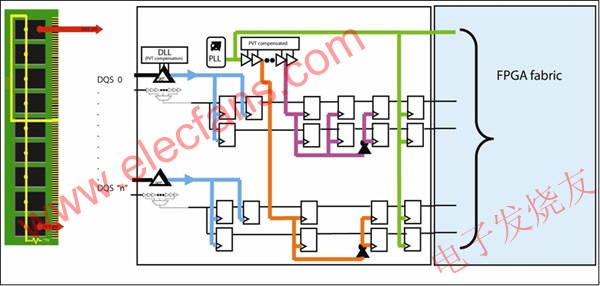

在讀取操作中,存儲器控制器必須補償由飛越存儲器拓撲引起的、影響讀取周期的延時。均衡可以被視作為出現在數據通道上的比I/O本身延時還要大的延時。每個DQS都要求一個同步時鐘位置的獨立相移(經過了工藝、電壓和溫度(PVT)補償)。圖2顯示出同一讀取命令下從DIMM返回的兩個DQS組。

圖2:I/O單元中的1T、下降沿和均衡寄存器。

一開始,每個分開的DQS被移相90度,從而捕獲與該組相關的DQ數據。然后用一個自由運行的再同步時鐘(頻率和相位與DQS相同)將數據從捕獲域轉移到圖2所示用粉紅色和橙色連線表示的均衡電路中。在這個階段,每個DQS組都有一個獨立的再同步時鐘。

接著DQ數據被送到1T寄存器。圖2中給出了一個1T寄存器實例,在上層通道中需要用這個1T寄存器對特定DQS組中的DQ數據位進行延時。注意在該例中,下層通道不需要1T寄存器。通過該過程開始對齊上層和下層通道。任何一個指定的通道是否需要1T寄存器是自動確定的,這是免費物理層IP內核中校準方案的一部分功能。

隨后兩個DQS組被傳送到下降沿寄存器。如果需要的話,還可以在啟動時通過自動校準過程把可選寄存器切換進來或切換出去。最后是將上層和下層通道對齊到同一再同步時鐘上,這樣就形成了一個將完全對齊的或經過均衡的單倍數據率(SDR)數據傳遞到FPGA結構的源同步接口。

寫均衡

與讀均衡類似,不過方向相反,DQS組在不同的時刻發出信號,以便與到達DIMM上的器件的時鐘一致,并且必須滿足tDQSS參數要求的+/- 0.25 tCK。控制器必須通過創建反饋環路來調整DQS與CK的關系,在此過程中,控制器會將數據寫入DRAM,再通過順序相位進行掃描讀回,直到發現寫入窗的終點。為了更好的建立和保持余量,數據應該在好窗口的中間點發出。

其他的FPGA I/O功能創新

高性能的Stratix III FPGA還具有許多創新性的其他I/O功能,可以實現到各種存儲器接口的簡單且魯棒性連接,這種功能包括了動態片上端接(OCT)、可變的I/O延時以及半數據率(HDR)等。

動態OCT

并行和串行OCT為讀寫總線提供合適的線路端接和阻抗匹配,因此FPGA周邊不需要外接電阻,從而減少了外接元件成本,節約了電路板面積,而且降低了布線復雜度。另外,它還大大降低了功耗,因為并聯端接在寫操作時可以有效地被旁路掉。

用于DQ去偏移(deskew)的可變延時

采用可變的輸入和輸出延時來跟蹤長度失配和電氣去偏移。精細的輸入和輸出延時分辨率(即50皮秒步進)被用于更精細的DQS間去偏移(獨立于均衡功能),這種偏移是由電路板長度失配或FPGA和存儲器件上I/O緩存的變化所引起的,如表1所示。最終,這增加了每個DQS組的捕獲余量。

表1:分辨率和絕對值待定特性。

為了將DDR3自動去偏移算法成為啟動校準過程的一部分,需要從運行時的FPGA結構實現延時單元。也可以利用輸出延時在輸出通道中插入少量偏移來有意地減少同時開關的I/O數量。

可靠的捕獲

DQS信號用作輸入選通信號,它必須移位到一個最佳位置才能捕獲讀取事務。移相電路可以將輸入的DQS信號移相0°, 22.5°, 30°, 36°, 45°, 60°, 67.5°, 72°, 90°, 108°, 120°, 135°, 144°或 180°,具體取決于DLL的頻率模式。移相后的DQS信號隨后被用作I/O單元各個輸入寄存器的時鐘。

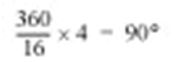

延時鎖定環路(DLL)在整個PVT范圍內將相位保持在一個固定位置。DLL模塊的相位比較器用于將兩個輸入之間的相位差保持在零。實現的方法是均勻地修正DLL模塊中的特定延時(10-16)。用于更新DLL中某個延時模塊的控制信號還被發送到DQS輸入路徑中的時延模塊。例如,可以利用DLL中的全部16個延時單元和DQS相移輸入路徑中的第4個延時抽頭來實現90°的相移:

或者選擇DLL中的10個延時單元和DQS相移輸入路徑中的抽頭4來實現36°的相移:

或120°:

該DLL采用頻率基準為每個DQS引腳中的延時鏈動態產生控制信號,并允許它補償PVT的變化。在Stratix III FPGA中有4個DLL,它們都位于器件的邊角,目的是使每個DLL能夠覆蓋器件的兩側,從而可以在器件的各個邊上支持多種DDR3 SDRAM存儲器接口。

跨越高速數據率域和設計簡化

DDR捕獲寄存器和HDR寄存器支持數據從雙倍數據率域(數據在時鐘的兩個邊沿)安全傳送到SDR域(數據位于頻率相同的時鐘的上升沿,但數據寬度加倍),再到HDR域(數據位于時鐘的上升沿,數據寬度仍是加倍,但時鐘頻率僅是SDR域的一半),這樣使得內部設計時序更容易實現。

裸片、封裝和數字信號完整性改進

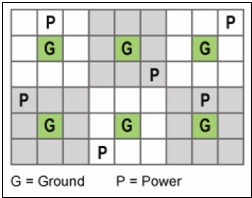

FPGA裸片和封裝的設計必須為高性能的存儲器接口提供更好的信號完整性(即用戶I/O與地和電源的比例為8:1:1,并具有最佳的信號返回路徑,如圖3所示)。此外,FPGA應該提供動態OCT和可變的偏移率,以便能夠控制信號的上升和下降時間以及可編程驅動能力,從而滿足所用標準(即SSTL 1.5 Class II)的要求。

圖3:連接到每個電源和地的8個用戶I/O。

本文小結

高性能Stratix III FPGA可以通過提供高存儲器帶寬、改進的時序余量以及系統設計中的靈活性來彌補高性能DDR3 SDRAM DIMM的不足。由于DDR3在實際使用中將很快超過DDR2,故提供更低成本、更高性能、更高密度和優異的信號完整性的高端FPGA必須提供與JEDEC兼容的讀寫均衡功能,以便與高性能的DDR3 SDRAM DIMM相接。FPGA與DDR3 SDRAM的有機整合將能夠滿足目前和下一代通信、網絡以及數字信號處理系統的要求。欲了解更多信息請登錄電子發燒友網(http://www.1cnz.cn)