如果看過前幾節內容的話,應該就對晶振比較了解了,但是還有一個問題,那就是測試。電路設計好之后,如何測試晶振電路是否滿足設計要求呢?

關于晶振的測試,我在村田官網上面看到一個比較好的視頻,有5節內容,網址是這個:

https://www.murata.com/zh-cn/products/timingdevice/crystalu/overview/basic

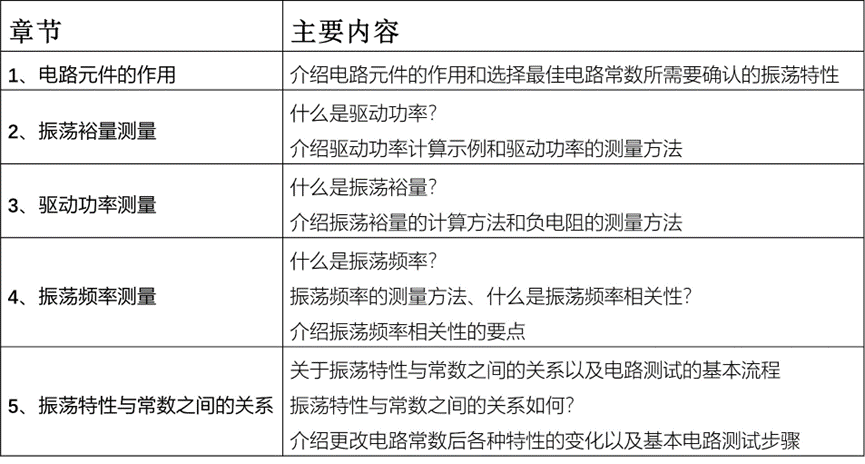

5節內容簡介如下:

視頻不長,每節大概3-4分鐘,不過該說的也都說了,還有實操部分。

按道理說我告訴兄弟們有這個視頻就可以了,可以自己去看,不過我還是把視頻的觀點作為筆記寫下來了。因為我也需要學習,相當于再鞏固一遍,加深理解吧。另外一方面,我個人不是喜歡視頻,因為視頻不好不斷暫停,而通常一些觀點需要停下來思索一下,結合自己已經知道的知識,兩者相互印證。如果不暫停,就像沒經過大腦,看完就完了,難以真正變成自己的知識。

下面就來看看我的文字筆記吧。

第1節、電路元件的作用

首先,我們需要評估一個晶振電路到底OK不OK,因為如果設計不合理,就會造成電路工作異常。

異常現象一般有下面兩種:

1、晶振電路停振

2、頻率偏差過大

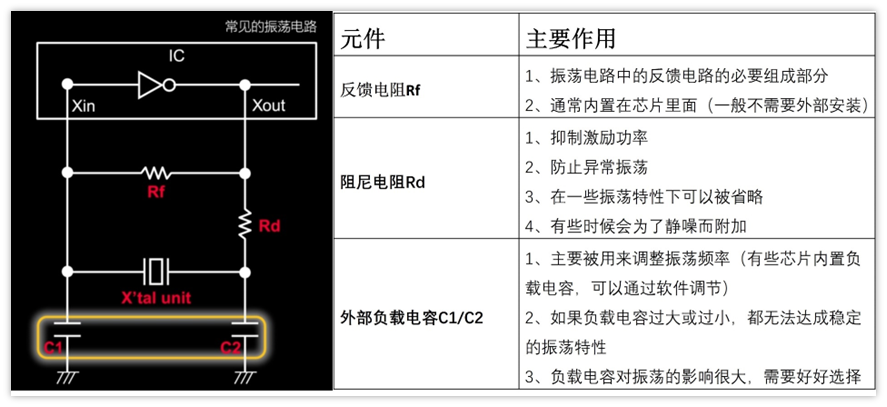

電路元件功能再次介紹:

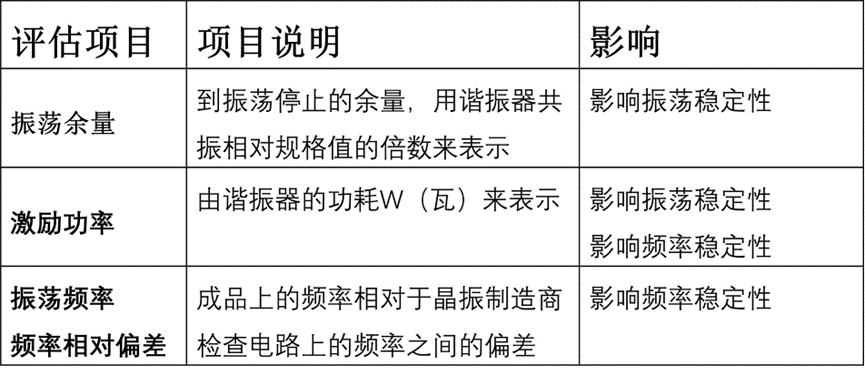

為了選擇最佳的電路參數,需要對下面三項內容進行測量評估:

1、振蕩余量

2、激勵功率

3、振蕩頻率相對偏差

第2節、振蕩余量的測量

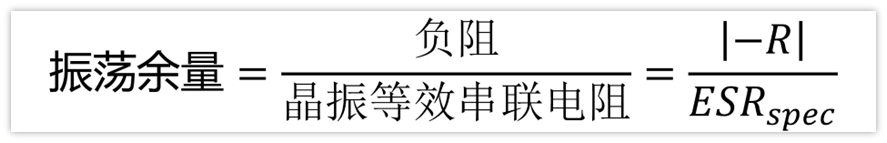

什么是振蕩余量?

振蕩余量是一個倍數,它等于晶體諧振器的負阻除以晶體諧振器的等效串聯電阻。理論上,振蕩余量有1倍以上就可以起振,但是當振蕩余量接近1倍時,偶爾可能發生不振蕩的情況。

為了穩定起振,一般要求振蕩余量大于5倍。

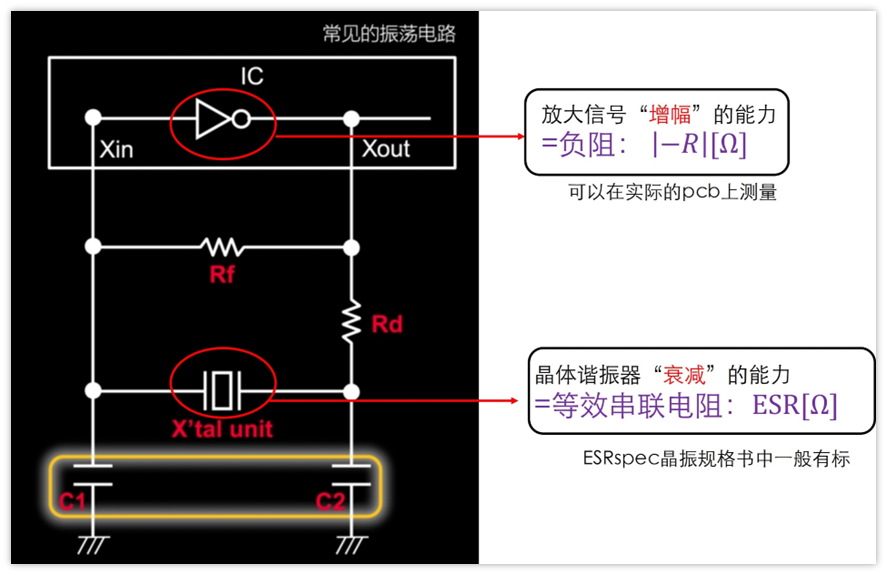

負阻可以看成是放大器放大信號的放大能力,負阻的大小需要在實際電路中測量得到。負性阻抗不是晶振的內置參數,而是振蕩電路的一項重要參數。

而等效串聯電阻ESRspec會消耗能量,可以理解為阻礙信號放大的阻力。ESRspc一般在晶振規格書手冊中有標注大小。

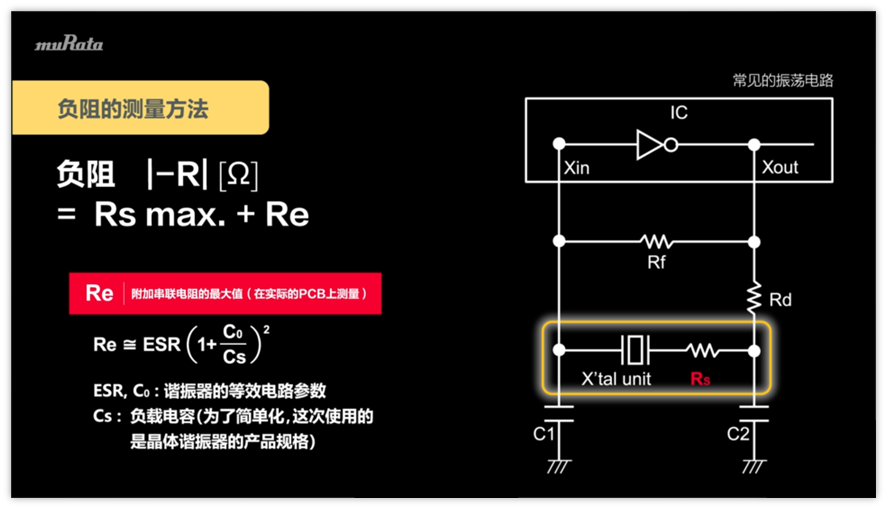

測量負阻方法:

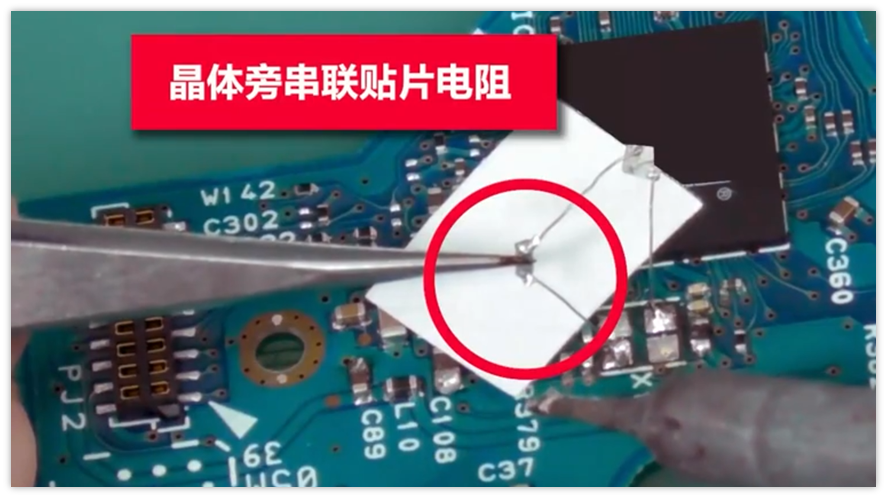

1、將電阻Rs串聯到晶體諧振器上面,逐步增大這個電阻,直到晶振還可以振蕩的極限為止,此時的阻值大小為Rsmax。

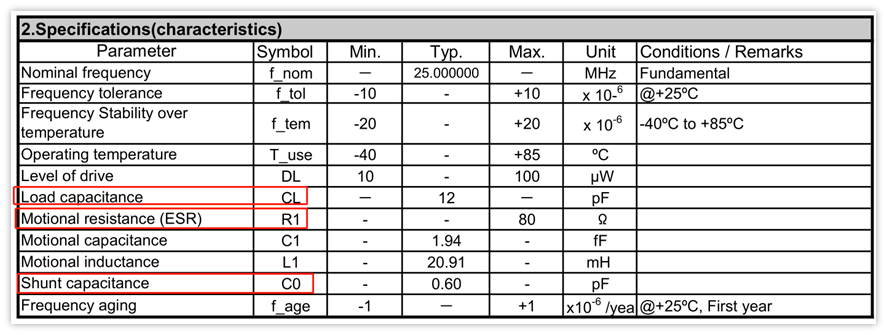

2、根據晶振手冊中的參數計算Re,Re≈ESR*(1+C0/Cs)^2。其中ESR為諧振器的等效串聯電阻,C0為晶體諧振器的shunt capacitance,Cs為晶振的負載電容,這三個參數一般都在晶體諧振器規格書手冊中有標注。

振蕩余量計算舉例

原視頻舉了一個例子,過程如下圖:

但是吧,我發現有個bug,實例里面Re=50Ω,ESR=100Ω,可以得到:ESR>Re。而從前面的計算公式Re≈ESR*(1+C0/Cs)^2,那么肯定有ESR

那么哪里出錯了呢?我覺得公式是沒錯的,所以應該是舉的實例算錯了,兄弟們怎么看呢?

第3節、激勵功率的測量

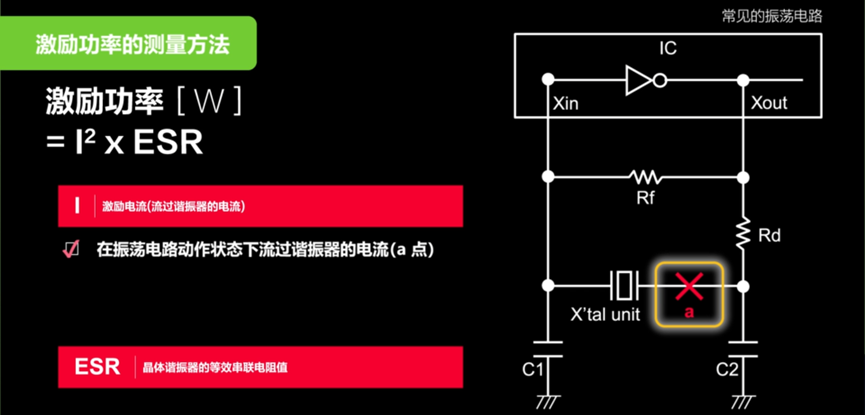

激勵功率指的是晶體諧振器的功耗。

晶振廠家一般都會在手冊中標注這個參數DL,如果實際電路中,晶振的實際功耗大于手冊中標準的DL,那么就過驅動了,存在風險,可能會引起頻率和等效串聯電阻的意外變化。

測量方法

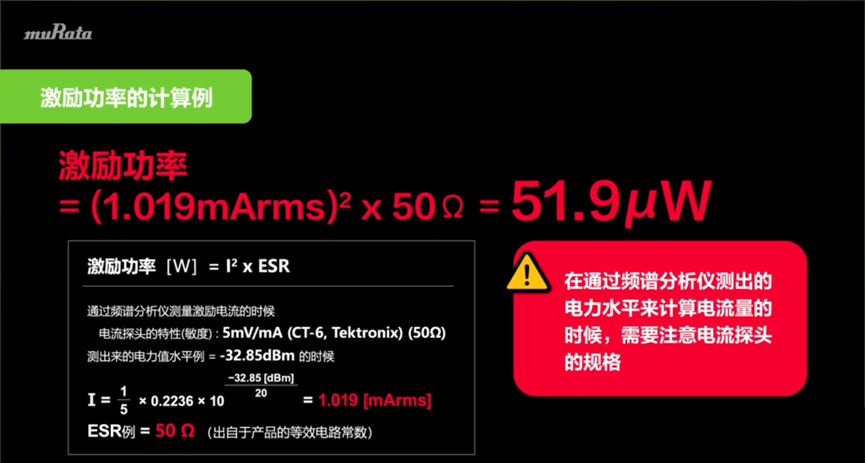

使用電流探頭,并使用示波器或頻譜分析儀等儀器,測量數據來計算上圖中a點的電流值。

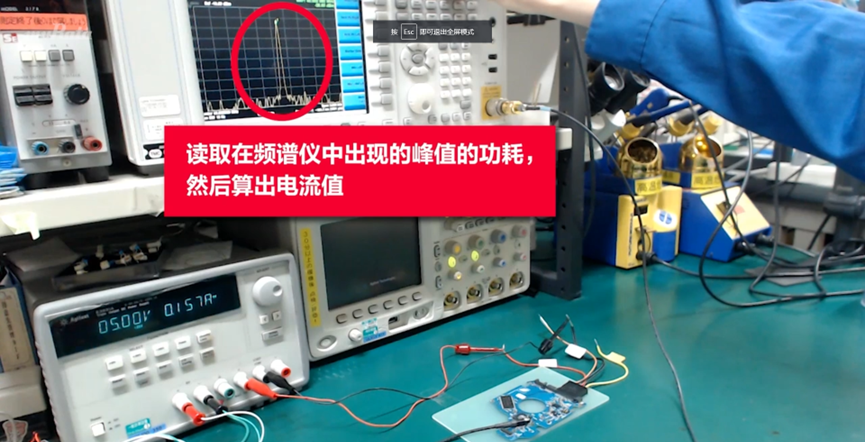

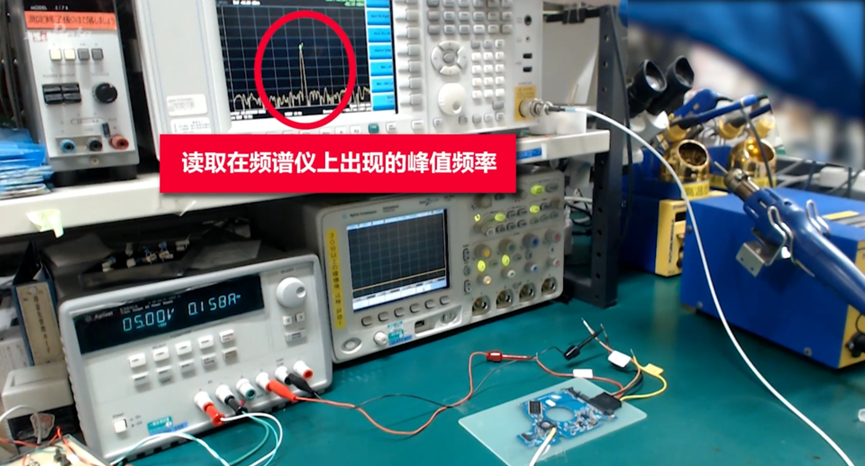

下面圖片是村田使用頻譜儀測量的過程:

1、接入電流探頭

2、讀取頻譜儀中的功耗,然后計算電流值

3、計算

問題來了,里面那個0.2236是個什么鬼?我也沒搞懂。。。

第4節、振蕩頻率的測量方法

振蕩頻率是指晶振在電路中實際工作的頻率,決定振蕩頻率的主要因素是晶振的特性,但是,實際的振蕩頻率也受下面因素的影響:

1、芯片的特性

2、外部匹配電容的容量

3、PCB的雜散電容

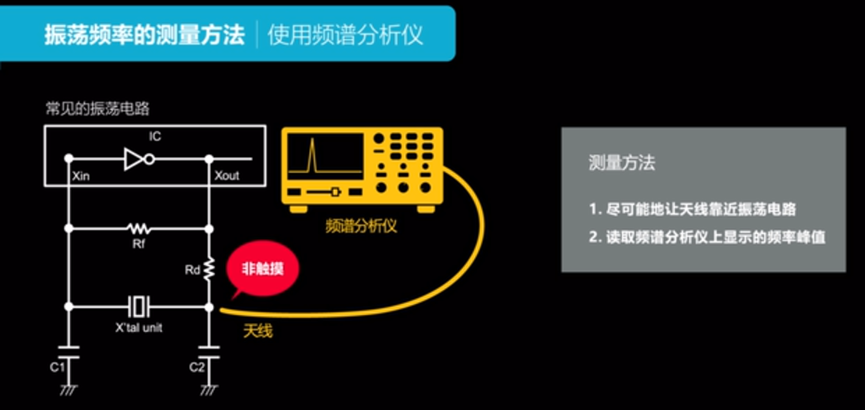

面臨的一個比較大的問題就是:如果用探頭直接接觸振蕩電路進行測量,是無法精確測量頻率的,因為會引入電容,所以,一定要通過非接觸式的方式來進行測量。

測量儀器:

1、頻譜分析儀

2、頻率計數器

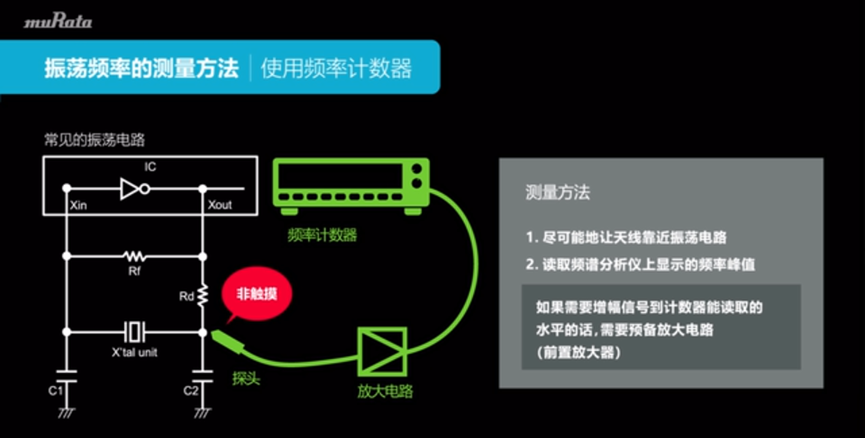

用頻譜分析儀時,使用非接觸式的天線來接收信號,讀取頻譜分析儀顯示的峰值處的頻率。

使用頻率計數器時,也需要用非接觸模式來測量,但是通常需要增幅信號到計數器能讀取的水平,所以需要預備放大電路。

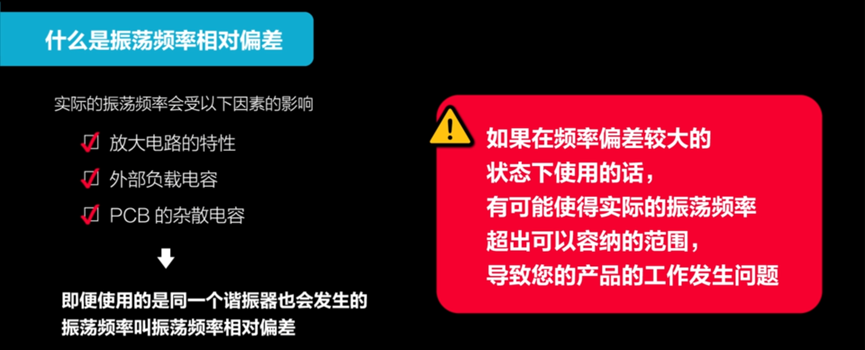

振蕩頻率相對偏差

實際的振蕩頻率受下面因素的影響:

1、芯片的特性

2、外部電容的容量

3、PCB的雜散電容

所以實際在PCB上測量頻率的時候,即使使用同一個晶振,也可能跟晶振廠家的PCB上測量的頻率不一樣,這個偏差就是振蕩頻率相對偏差(并非相對晶振標稱值頻率的頻偏)。

如果在頻率偏差較大的狀態下使用,有可能使得實際的振蕩頻率超出可以容納的范圍,進而導致產品工作有問題。

如果需要較高的頻率精度,就需要格外注意頻率偏差!必須把這個相對偏差加上諧振器的規格偏差(手冊中的頻偏),來判斷是否能把頻率調整在希望的范圍內。

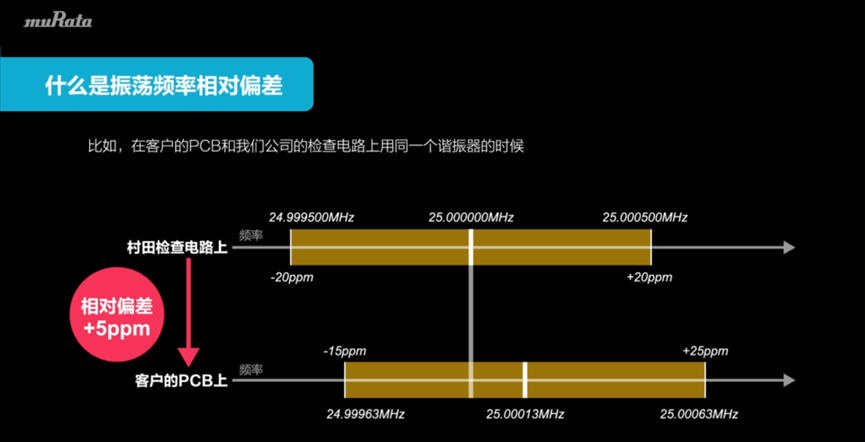

如下圖:相對偏差為+5ppm,晶振規格偏差為±20ppm,所以,最終實際的頻偏應該是:-15ppm~+25ppm。

實際工作中,可以跟廠家要帶頻率數據的樣品,然后將樣品裝在自己的PCB板上實測,測得的頻率與廠家給的頻率之間的偏差就是相對偏差。

第5節、振蕩電路與電路測試的關系

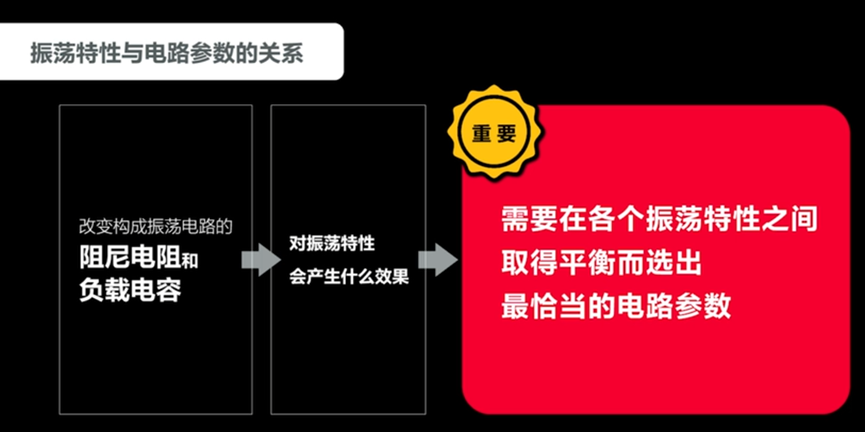

前面介紹了3個測試,分別是振蕩余量、激勵功率、振蕩頻率相對偏差。既然是測試,那么就有可能不合格,那么不合格怎么辦呢?

自然是要調整電路,能調整的器件不多,主要是2個:

1、阻尼電阻Rd(串聯電阻)

2、負載電容C1/C2(匹配電容)

那調整的目標是什么呢?

目標:振蕩余量較大好,一般大于5倍;激勵功率較低好;振蕩頻率偏差小好;

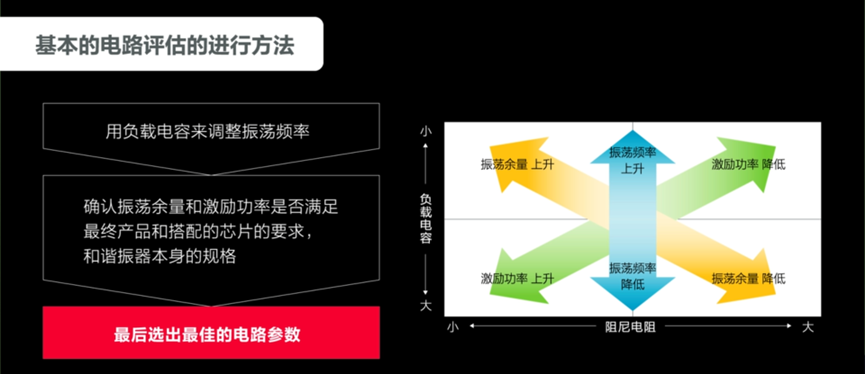

問題是這幾個參數之間是矛盾的,因此需要進行平衡。

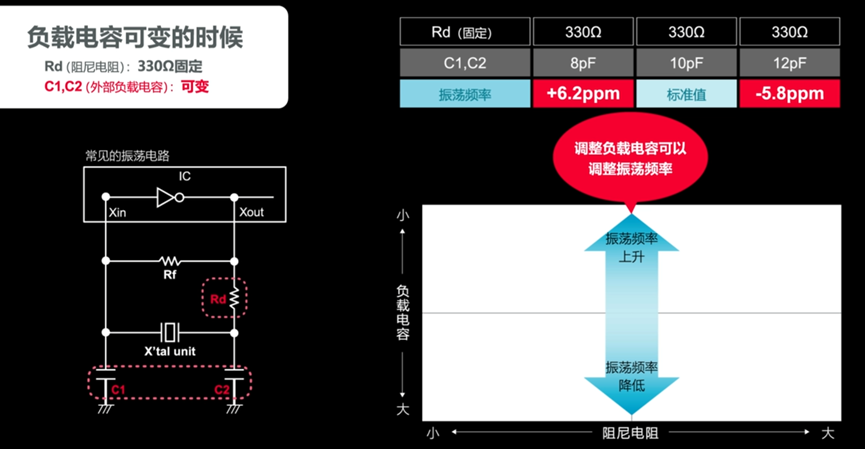

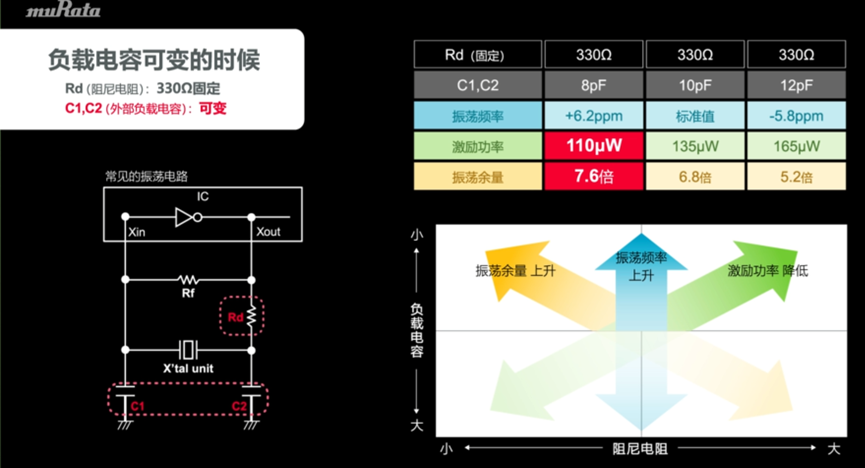

變動負載電容(匹配電容)時

如果減小負載電容,那么振蕩頻率會上升;反之如果增大負載電容,那么振蕩頻率會下降。

但是,另一方面,增大了負載電容,會導致激勵功率增加,同時振蕩余量減小,這都是不好的影響。

如果為了降低激勵功率,減小振蕩余量去調小電容,首先會造成頻率升高。其次,如果電容太小,那么電容值本身的偏差,PCB板雜散電容的影響就會增大,造成振蕩頻率變化大。

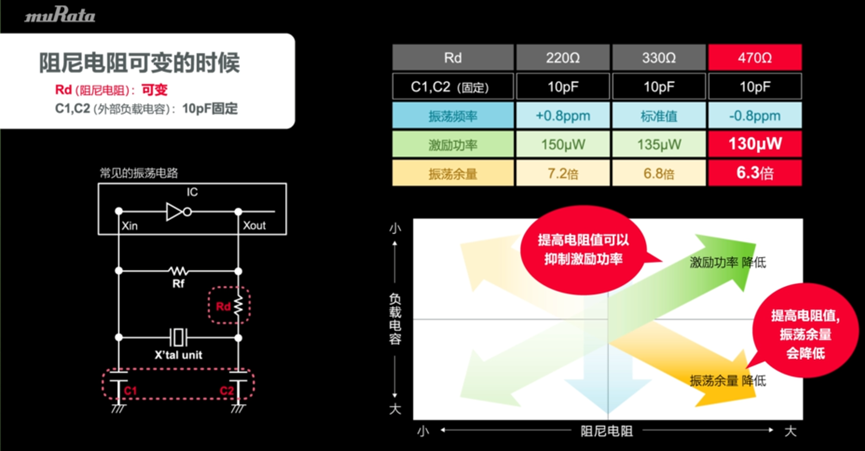

變動阻尼電阻Rd(串聯電阻)

首先,增大電阻,可以降低激勵功率,但是會引起振蕩余量降低,這兩個影響一好一壞,需要平衡。

另外,從下圖可以看出, Rd的變化對振蕩頻率的影響很小,從330Ω到470Ω,頻率變化0.8ppm。

電路調整測量

結合前面的分析,電阻對振蕩頻率影響較小,振蕩頻率主要由匹配電容決定,而同時匹配電容又跟振蕩余量和激勵功率相關。

因此策略如下:

1、首先通過調整負載電容C1/C2(匹配電容)來調整振蕩頻率到合適值

2、再通過調整Rd來將振蕩余量和激勵功率調到合適的值。

小結

以上就是視頻的主要內容,這樣寫下來,自我感覺確實比看一遍視頻了解更多。

另外,關于晶振電路的測量,我個人其實并沒有太多的經驗,以前實際測試也只是拿示波器直接接觸量的,并非像視頻說的那樣使用頻譜儀來測量。不過從道理上來說,使用頻譜儀測量確實應該更接近真實的情況。如果我們遇到晶振偶爾壞掉的問題,個人覺得上面這一套測試方法還是比較科學的分析手段。

晶振電路,兄弟們都是怎么測試的呢?測試了哪些內容呢?

?