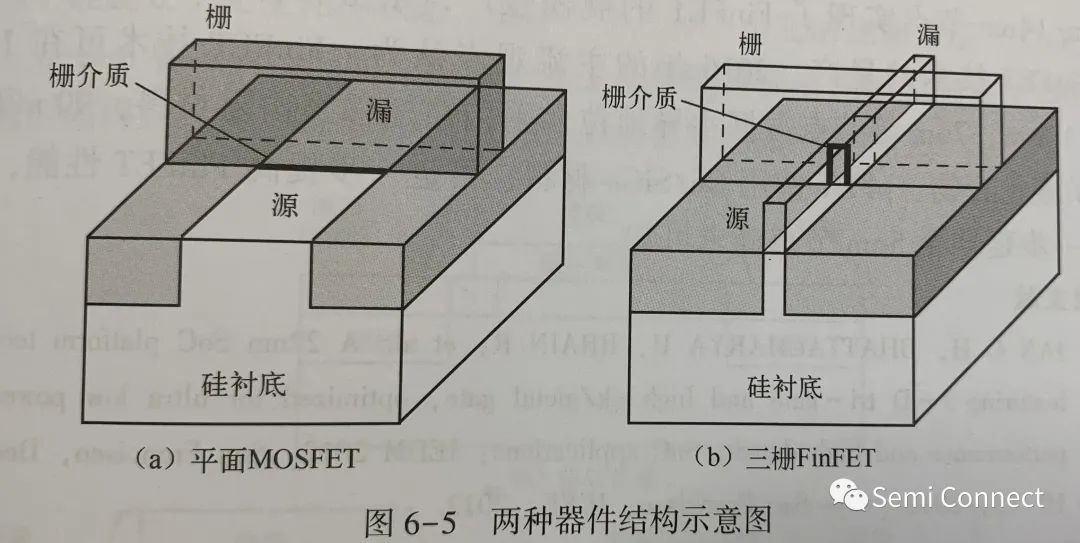

鰭式場效應(yīng)晶體管(FinFET)是立體多柵器件的一種,其主要特征是由魚鰭形(Fin)的薄層硅構(gòu)成折疊的導(dǎo)電通道,并由雙面或三面折疊包圍的柵極控制,如圖6-5所示。較薄的溝道和多柵控制提高了器件的柵控能力,可以保證器件工作于全耗盡狀態(tài)。與平面CMOS器件相比,F(xiàn)inFET因其三維全耗盡的結(jié)構(gòu),在抑制短溝道效應(yīng)、提高器件性能、降低功耗等方面具有明顯的優(yōu)勢;由于FinFET的短溝道效應(yīng)控制較好,因此溝道摻雜濃度可顯著降低,從而改善遷移率下降和隨機摻雜漲落問題;雙柵或多柵FinFET可明顯改善器件亞閾值斜率,優(yōu)化后的亞閾值斜率可接近60mV/decade;在相同的硅片投影面積上,F(xiàn)inFET可形成更寬的有效溝道,從而提高芯片的驅(qū)動能力。

FinFET由美國加州伯克利分校的胡正明(Chenming Hu)團隊在1999年命名,其原型為DELTA(Depleted Lean- Channel Transistor)器件。英特爾公司將類似器件稱為三柵晶體管(Tri- Gate Transistor),在技術(shù)文獻中一般將這種基于Fin并具有多柵結(jié)構(gòu)的器件(無論雙柵還是三柵),都稱為FinFET。

2006年之前,F(xiàn)inFET的制備尚未引入源漏選擇性外延和應(yīng)變硅技術(shù),因此其驅(qū)動電流普遍較低。而對設(shè)計者來說,無法靈活地改變溝道寬度,所以離量產(chǎn)應(yīng)用尚有距離。英特爾公司在2006年發(fā)表的論文中采用了源漏外延的方法來增加應(yīng)力和源漏接觸面積,從而提高遷移率,降低串聯(lián)電阻,F(xiàn)inFET 獲得了足夠的驅(qū)動能力,nFET和pFET的電流驅(qū)動能力均達到1mA/um以上。此外,在設(shè)計中,F(xiàn)inFET溝道寬度的調(diào)整可通過Fin的不同數(shù)量來變通實現(xiàn),這就為FinFET的量產(chǎn)奠定了基礎(chǔ)。

FinFET在量產(chǎn)應(yīng)用中也面臨著諸多挑戰(zhàn):Fin具有較大的高寬比,這對于Fin的圖形化及精確控制,表面光滑及缺陷去除處理,摻雜注入,以及后續(xù)工藝中對Fin的無損傷保護等都有很高的難度;由于Fin的存在,非平面的硅片表面給柵,側(cè)墻等工藝的刻蝕和填充等都帶來了挑戰(zhàn);Fin的厚度存在一定的優(yōu)化值,厚度過小會導(dǎo)致驅(qū)動電流過小;增加Fin的高度可以獲得更大的有效溝道寬度,但是也會增加寄生電容;通過Fin的數(shù)量實現(xiàn)的有效溝道寬度變化存在離散化、非連續(xù)的特點,給電路設(shè)計的靈活性帶來問題。

在22nm技術(shù)節(jié)點之前,采用了高k金屬柵的平面CMOS技術(shù)尚能滿足量產(chǎn)的需要,再加上FinFET技術(shù)的上述挑戰(zhàn),以及由此帶來的成本上升,因此FinFET技術(shù)一直沒有實現(xiàn)工業(yè)量產(chǎn),并從16nm/14nm節(jié)點開始成為國際主流集成電路制造廠商的首選技術(shù)。截止2017年4月,已有英特爾、三星、臺積電和格芯在16nm/14nm節(jié)點實現(xiàn)了FinFET的規(guī)模量產(chǎn),三星和臺積電也已開始進行10nmFinFET技術(shù)的量產(chǎn)。2016年的主流觀點認為,F(xiàn)inFET技術(shù)可在16nm/14nm、10nm、7nm等節(jié)點占據(jù)主導(dǎo)地位,采用高遷移率溝道材料,如nFET使用III-V 族化合物、pFET使用Ge/SiGe材料,可進一步提高FinFET性能,但是否能進一步延伸至5nm節(jié)點尚未可知。

審核編輯:劉清