平面互補場效應晶體管工藝流程

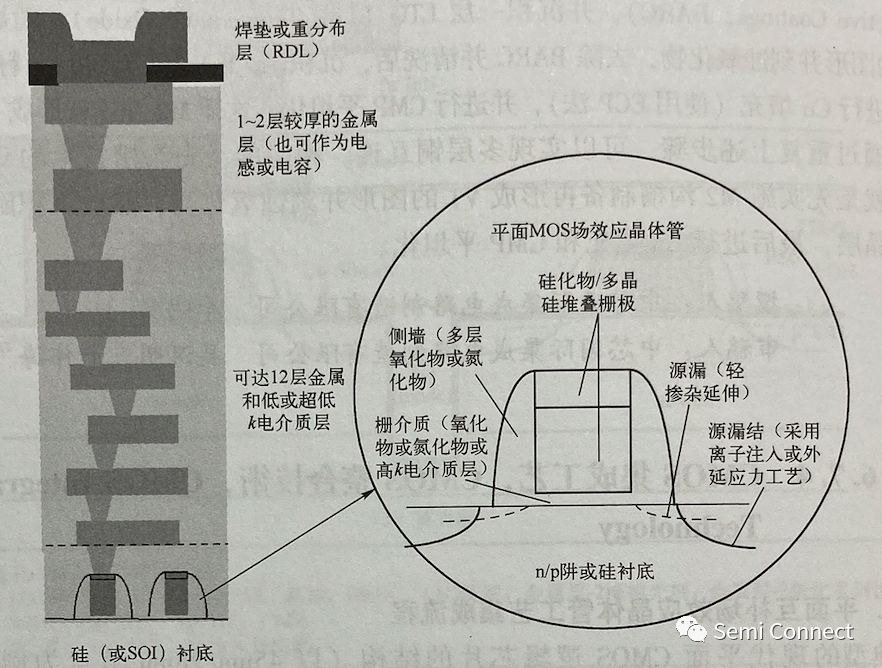

典型的現代平面CMOS 邏輯芯片的結構(以 45nm/28nm 節點為例)如圖所示。

?典型的襯底是p型硅或絕緣體上硅(SOI),其直徑為 200mm 或300mm;在多層銅互連中,最上面兩層金屬較厚(常被用于制造電感或電容),頂層的鋁層用于制造封裝用的鍵合焊盤。局部放大圖顯示了 MOS 場效應晶體管的多晶硅和硅化物柵疊層、高K柵介質、輕摻雜(LDD) 或源漏擴展區、外延生長應變硅源漏等細節。

CMOS 場效應晶體管(28nm 節點)的特征包括鈷或鎳硅化物多晶硅柵疊層、氮氧化硅或高k材料(氧化鉿)柵介質、多層(Oxide-Nitride-Oxide, ONO)側墻、輕摻雜(LDD) 或源漏擴展結 (S/D Extension)和鎳硅化物 S/D 深結。

內部核心邏輯電路的場效應晶體管的典型工作電壓為 0.9~1.1V,溝道長度為 30~40nm,柵介質等效氧化硅厚度為 1.5~2nm, S/D 擴展結厚度為 15~20nm。I/0 電路(連接外圍芯片的接口)場效應晶體管的典型工作電壓是 1.5V、1.8V 和2.5V,相應的溝道長度為 100~200nm,柵介質厚度為3~6nm,S/D 擴展結厚度為 25~30nm。

核心邏輯電路較小的工作電壓是為了減小操作功耗。在 45nm/28nm CMOS節點都采用了溝道工程,通過沿場效應晶體管溝道方向施加應力來增強遷移率(如針對 n-MOS 溝道中電子施加張應力和針對p-MOS 溝道中空穴施加壓應力)。 28nm CMOS 節點都采用了 SiGe 應變硅外延 S/D?(用于p-MOS)和應力記憶技術(用于n-MOS)。

在28nm/20nm 及以下的節點還采用了新的模塊技術,如新的高k介質和金屬柵疊層,雙應力 SiC 或?Si ?:P 外延與應力記憶技術(用于n-MOS 源漏)。在16nm/ 14nm/10nm/7nm 及以下的更先進節點,都采用子非平面溝道器件 FinFET。 現代平面 CMOS 場效應晶體管和金屬互連的制造工藝流程如圖所示。

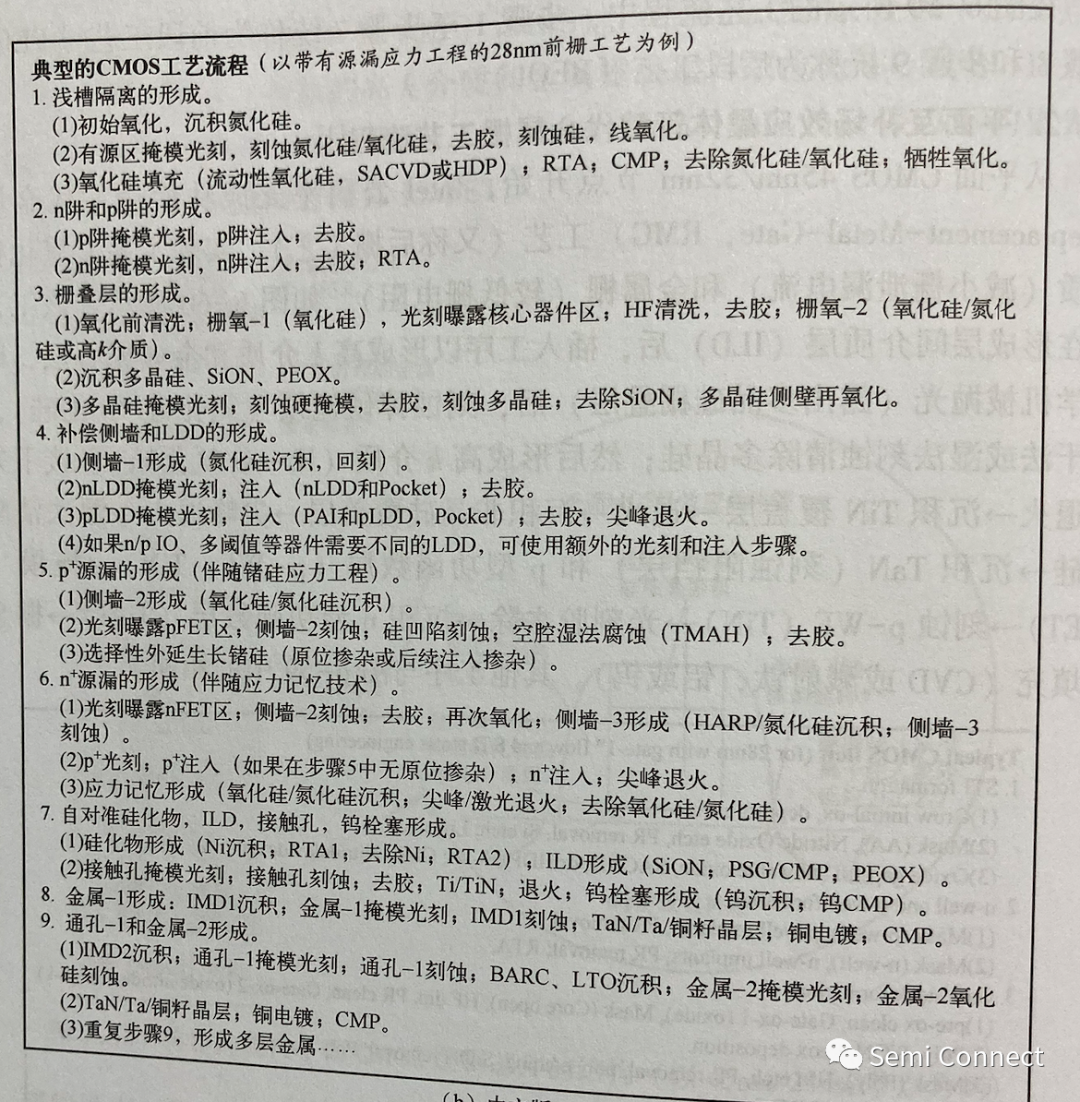

以平面 CMOS 28nm 節點為例,其制造工藝流程如下所述。

(1)形成淺槽隔離 STI,然后形成n阱區城(用于 pMos)和p阱區域(用于nMOS),分別對阱區域進行選擇性注入摻雜。

(2)生長n-MOS?和?p-MOS 柵氧化層,形成多晶柵疊層和圖形化,再氧化以保護多晶柵疊層的邊緣,然后形成補償側墻來調整 n/p MOS LDD 的位置。

(3)形成鍺硅(SiGe)外延p-MOS 的源漏;再形成n-MOS 的源漏,并進行應力記憶技術和源漏注入摻雜。

(4) ? 形成鎳硅化物,沉積層間介質層 (ILD)后,通過圖形化,刻蝕和鎢栓塞(W-Plug)填充形成接觸孔。至此,n-MOS 和 p-MOS 晶體管己經形成。

(5) 通過單鑲嵌技術形成第一層銅 M1,其他的互連通過雙鑲嵌技術來實現。通過重復雙鑲嵌技術實現多層互連。最頂層的兩個金屬層和鋁層用于制造無源器件和鍵合焊盤。 ?

在圖2所示的工藝流程中,步驟 1至步驟7統稱為前段工藝(FEOL),步驟8和步驟9統稱為后段工藝 (BEOL)。

審核編輯:劉清