?

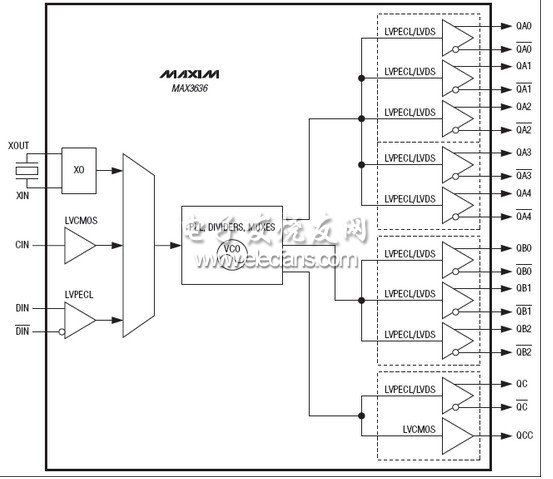

MAX3636是一個高度靈活,高精度鎖相環(huán)(PLL)時鐘發(fā)生器為下一代網絡設備的要求低抖動時鐘發(fā)生器和強大的高速數據傳輸的分布進行了優(yōu)化。優(yōu)異的電源噪聲抑制,以及引腳可編程的LVDS / LVPECL輸出接口。 MAX3636提供9個差分輸出和一路LVCMOS輸出。每個輸出的頻率和輸出接口,可單獨編程,使這一設備系統(tǒng)板上的多個晶體振蕩器和時鐘分配IC的理想替代品,節(jié)約成本和空間。

這3.3V IC采用7mm x 7mm,48引腳TQFN封裝,從-40 ° C至+85 ° C。

關鍵特性

輸入

水晶接口:18MHz的到33.5MHz

LVCMOS輸入:15MHz的至160MHz

15MHz到350MHz的差分輸入:

輸出

LVCMOS輸出:可達160MHz

LVPECL/ LVDS輸出:可達800MHz

三個人的輸出銀行

引腳可編程分頻器

引腳可編程輸出接口

VCO調諧范圍寬(3.60GHz至4.025GHz)

低相位抖動

0.34psRMS(12kHz至20MHz)

0.14psRMS(1.875MHz到20MHz)

優(yōu)異的電源噪聲抑制

-40° C至+85° C工作溫度范圍

3.3V電源