LVDS低電壓差動信號技術是應用于數(shù)據(jù)通訊、電信、ISP及儲存產(chǎn)品上多點通訊的革命性高效能基架。在許多案例中,它擴充了四倍的頻寬,并且消耗低功率,簡化終端的復雜度。本文提供了總線LVDS基架設計上的秘訣及實務設計指南,并輔以設計計算、仿真及實際硬件量測來強化上述的概念。

總線 LVDS 簡介

總線低電壓差動訊號傳輸 (BLVDS) 芯片是美國國家半導體在低電壓差動訊號傳輸 (LVDS) 技術的基礎上進一步開發(fā)出來的全新系列總線接口電路。這系列接口芯片最適用于多點傳輸電纜及基架應用方案。BLVDS 技術與標準的 LVDS 技術不同,前者可提供更高的驅動電流,因此可支持多點傳輸應用方案所必需的兩個終端裝置,而且其頻率爭奪保護功能及平衡輸出阻抗的效能也獲得加強。目前市場上已有收發(fā)器、轉發(fā)器、串聯(lián)器、解串器及時脈緩沖器等的供應。

BLVDS 芯片的低電壓差動訊號只有約 300 mV 的電壓振幅,而且轉變時間較快,令驅動器可以支持低速的應用方案 (低至只有幾兆赫或甚至直流電) 以至 400 Mbp-s 以上的高速應用方案。此外,其低電壓振幅可將功率消耗及噪聲減至最低,而差動數(shù)據(jù)傳輸設計則可支持 +/- 1 伏 (V) 的共模電壓范圍,容許芯片插入正在帶電作業(yè)的總線。

一向以來,業(yè)界只致力提高標準邏輯單端驅動器 (244 類型) 的驅動電流,以解決總線驅動的問題。雖然這個方法可提供標準的邏輯振幅及更高的驅動電流,但只能將速度提高至 10 至 20 MHz 之間,而且無法超越這個速度上限。由于單單提高驅動電流并不足以將速度進一步提高,因此便需要其它方面的改善加以配合。一直以來,每當我們提高驅動電流,訊號振幅便會縮小,于是便有基架收發(fā)器邏輯 (BTL) 電路的出現(xiàn),這種邏輯電路可以支持 80 mA 的接收點 (sink) 及 1 伏的訊號振幅。這個設計可以輕易驅動負載較大的基架,令傳輸速度可高達 50 至 66 MHz。但 BTL 像一般的TTL 一樣,仍采用單端的設計,而且只有約 400 mV 的噪聲容限。低振幅的單端設計無法突破 100 MHz 的速度限制,因為噪聲容限已處于可以接受的最低水平。

由于 BLVDS 可將訊號振幅減至比 TTL 更低的水平,同時也可將驅動電流減低至 10 mA,因此可以無需大量電流。BLVDS 采用類似 LVDS 但可支持多點傳輸應用方案的差動數(shù)據(jù)傳輸設計,因此其噪聲容限比其它低振幅單端技術高一倍,不但確保 300 mV 的訊號振幅能在數(shù)百 Mbps 的速率下進行作業(yè),而且又可提供雙倍的噪聲容限以及減低噪聲。由于 BLVDS 的接收器擁有共模排斥功能,因此也容許芯片插入正在帶電作業(yè)的總線。

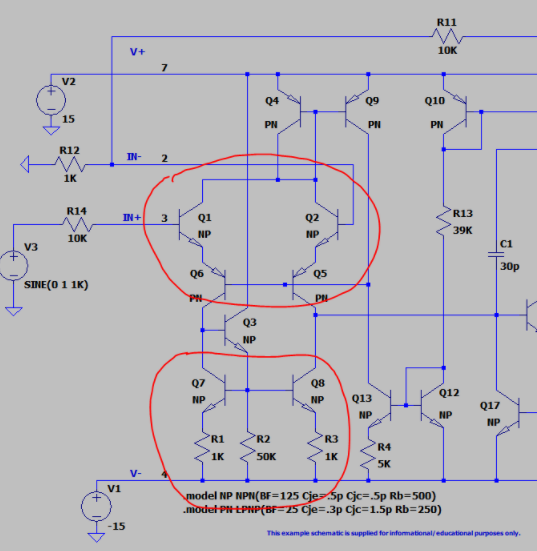

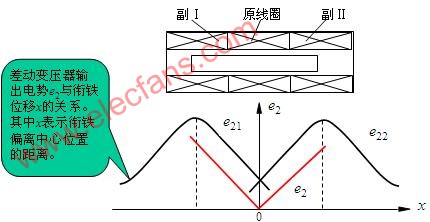

圖 1:BLVDS 訊號

總線配置

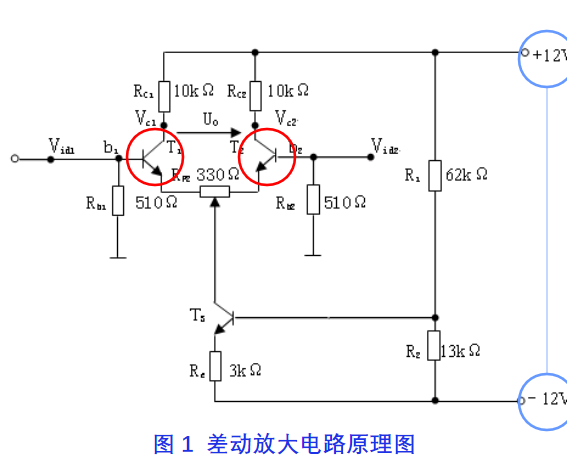

BLVDS 芯片適用于點對點應用方案、多站式 (multi-drop) 數(shù)據(jù)分布應用方案或舊式的多點傳輸共享總線應用方案,可支持數(shù)據(jù)總線、訊號控制或時鐘分布。圖 2 顯示點對點、多站式以及多點傳輸總線的配置。多站式傳送是多點傳送的其中一個特別情況。多站式傳送應用方案采用一個供電來源驅動多個接收器。若驅動器設于總線的起點,便只需在另一端裝設終端裝置。由于多點傳輸?shù)脑O計可以容許供電來源設于總線上的任何位置,因此總線的兩端均需要裝設終端裝置。每當同一訊息需要傳送到多個地方,多站式及多點傳輸?shù)呐渲帽闩缮嫌脠觥H粢曰ミB密度作標準衡量,這種總線配置也可說極有效率。我們?nèi)粼O計通訊速度在 500 Mbps 以上的應用方案,便應考慮采用點對點鏈接,因為其中的線路互連可確保訊號質(zhì)素。

圖 2:一般的總線配置:(A) 點對點,(B) 多站式,(C) 多點傳輸

差動基架設計的 13 項秘訣

以下介紹采用 LVDS 技術的差動基架,并分別就 13 個不同的基架設計問題討論各種有關的建議、別出心裁的解決辦法、設計原則或有關技術的最新發(fā)展趨勢,以確保這種 LVDS 差動基架可以發(fā)揮最高的效能。設計秘訣均以斜體排印。

秘訣 1:邊緣速率

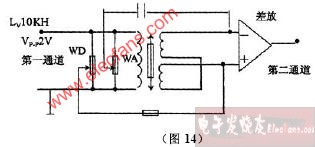

我們曾利用多點傳輸基架模型進行 TDR 仿真測試,并分析多點基架的邊緣速率。整個分析均采用 NESA 專有的 “被動式訊號完整性” (Passive Signal Integrity) 差動 TDR/TDT 模擬工具。

我們首先將差動式 TDR 激發(fā)訊號輸入設有 11 個插槽的基架仿真模型的第 8 插槽內(nèi),然后分別以 0.3、0.5 及 1.0 毫微秒 (ns) 的 TDR 上升時間進行模擬,以取得不同的 TDR 模擬結果。模擬時也分別采用 0.5 吋、1.0 吋及 1.5 吋等不同的線頭長度,以便可以提供多個不同的重要參數(shù)以供參考。以下圖 3 顯示有關負載及邊緣速率的表現(xiàn)。留意圖中的曲線在接近 28 ? 的水平穩(wěn)定下來,其效果相等于將兩個 56 ? 終端電阻以平行方式連接一起。邊緣速率越快,曲線的振幅便越大。雖然高速傳輸需要較快邊緣速率的支持,但這樣會令線路出現(xiàn)嚴重的傳輸問題,不過有關問題可以稍后解決。

圖 3:分別以 0.3、0.5 和 1 ns TDR 上升時間配對 0.5 吋線頭進行的差動 TDR 模擬

TDR 模擬的結果顯示多點傳輸基架的不連續(xù)性結構。差動阻抗的起點是 100 ?。這是啟動點上的 0.5 吋線頭的差動阻抗。第一個低點的出現(xiàn)是由電路分裂及連接器負載所造成。反彈高點出現(xiàn)在基架的第一條蝕刻線路,長度約相等于插槽間距。由于線頭及連接器以這一點為連接基架蝕刻線路的接點,因此最接近的一對插槽便造成第二個低點。由于反射性不連續(xù)性、銅導線及電介質(zhì)損耗等問題,TDR 激發(fā)訊號沿著基架向前傳送時速度會減慢。測試顯示出來的阻抗計有基架蝕刻線路、連接器、線頭及芯片等的凈負載阻抗。最后的平均數(shù)值約為 28 ?,這是將以上有負載基架的一半數(shù)值以平行方式加在一起而得出來的。

計算傳輸線路數(shù)字時,轉變時間 (上升或下降) 是最重要參數(shù),這點我們必須明白。300 ps 以上的邊緣速率已不適用于多站式或多點傳輸應用方案。

秘訣 2:線頭長度

我們也曾利用 NESA 的 TDR 及 TDT “被動式訊號完整性” 仿真方法分析線頭長度的影響。圖 4 及 5 顯示分別采用 0.5 吋、1 吋及 1.5 吋等線頭進行的差動 TDR 及 TDT 模擬測試。TDR 激發(fā)訊號的上升時間是固定的,而且只有 0.3 ns。

一如以上所述,TDR 的模擬結果顯示阻抗的變化,而 TDT 的模擬結果則顯示過大的波動。線頭越長,阻抗不連續(xù)性便越大。阻抗不連續(xù)性越大,振幅也越大。

圖 4:分別采用 0.5 吋、1 吋及 1.5 吋等線頭長度配對 300 ps 上升時間而進行的差動 TDR 模擬測試

TDR/TDT 模擬測試均顯示子卡的線頭長度應越短越好,建議長度不應超過 1.5 吋。線頭越短,效能便越高,這個定律適用于所有基架。

縮短線頭長度,以便減少傳輸線路問題的出現(xiàn)。

秘訣 3:接口組件的擺放位置

根據(jù)上述的 TDR 仿真測試及 TDR/TDT 仿真測試所顯示,線頭太長會產(chǎn)生線路傳輸?shù)膯栴},為了減少傳輸問題的出現(xiàn),接口芯片的位置擺放應該是首要考慮的問題,以確保線頭能縮至最短。這個建議實行起來非常簡單,若切實執(zhí)行,將有助減少許多傳輸線路問題的出現(xiàn)。

將收發(fā)器 (多點傳輸) 及接收器 (多站式傳輸) 盡量放置在靠近連接器的位置,并使用印刷電路板的底面兩面,以便將線頭縮至最短。

秘訣 4:差動阻抗

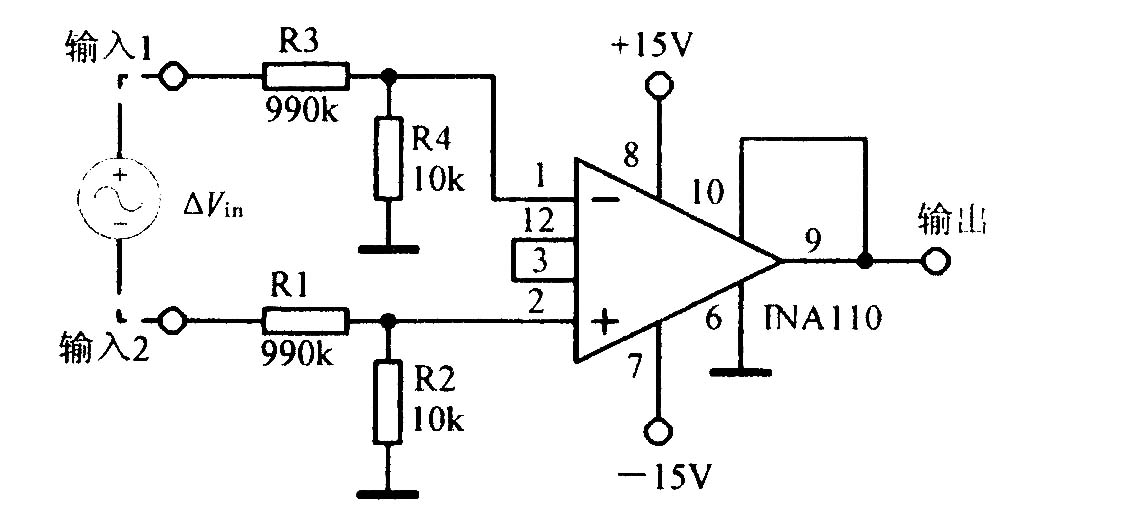

我們采用 NESA 的 Method-of-Moments 二維現(xiàn)場解方程式例程 (field solver) 以確定差動阻抗的三維參數(shù)。理想的結構正是寬邊耦合 (broadside-coupled) 差動傳輸導線所采用的結構,請參看圖 6。

BLVDS 的規(guī)定是針對每一對 100? 差動阻抗而設計。若采用以下所建議的體積參數(shù),便可實現(xiàn)這個阻抗。按照 Method-of-Moments 的方法計算,若采用寬 7 mils、厚 1 oz、而電介質(zhì)厚度 H1、H2 及 H3 分別為 12 mils 并采用 FR4 物料的銅線電路,差動阻抗便可達到 100?。只要將每一對電路的分隔空間保持在 20 mils 以上,便可在每一對電路之間提供極低的差動及共模耦合。這種電路結構的優(yōu)點是確保電路可以在連接器的范圍內(nèi)保持緊密耦合。

采用緊密耦合的電路可確保外來的噪聲以共模形式出現(xiàn),以便接收器可以將之排斥。此外,緊密耦合電路也可減低幅射數(shù)量。

基架的實際阻抗隨著基架的負載大小而改變。為了確定實際的阻抗,我們采用 NESA 專有的 “被動式訊號原整性” 差動 TDR 模擬測試分析設有 20 條插槽的基架。我們首先將差動 TDR 激發(fā)訊號輸入基架的一端,其 TDR 上升時間設定為 300ps,而 TDR 差動內(nèi)在阻抗則設定為 100?。

我們根據(jù)以下四個不同負載情況,進行了不同的 TDR 模擬分析,以確定基架的實際阻抗:

1) 100? 原始差動阻抗的印刷電路板基架蝕刻電路;

2) 基架的一面裝滿了 2mm 連接器;

3) 所有 20 個插槽均插滿了邏輯電路卡,線頭均為 1 吋 (并無芯片);

4) 每一張插卡的每一線頭末端均加設了 DS92LV090A 收發(fā)器。

?7 顯示負載一如所料可減少基架阻抗。若基架已加載半數(shù) 2mm 的連接器 (只限于接腳),其基架實際阻抗會減少至約 78?。線頭為 1 吋的滿載基架只有約 55? 的實際阻抗。加載了裝置 (DS92LV090A) 之后,基架阻抗減至約 53?。

阻抗軌跡上所見的波動是由于連接器及線頭負載出現(xiàn)阻抗不連續(xù)性的反射(discontinuity reflection)。接近 TDR 驅動點的上升時間較為明顯,足以使我們清楚區(qū)分蝕刻電路 (阻抗較高) 與連接器線頭 (阻抗較低)。當 TDR 階梯函數(shù)曲線往基架下方移動,上升時間漸漸失去其清晰度,令我們較難區(qū)分波形的已加載及未加載部分,而有關數(shù)字更融入所量度的平均阻抗之中。

由于互相緊貼的插卡產(chǎn)生分布式電容負載,因此基架的實際阻抗 (負載阻抗) 會較低。此外,數(shù)據(jù)傳輸速度 (基架下方的每一單位延誤) 也會受基架的負載影響。包括連接器、線頭及設備電容器等負載在內(nèi)的滿載基架比未滿載基架慢約 50%。

秘訣六:總線終端裝置

對于 BLVDS 來說,一般的多點傳輸 (multi-point) 應用方案只需要在總線兩端的線路之間加設一個電阻。但多站式 (multi-drop) 的應用方案便需要一至兩個電阻,視乎驅動器的位置而定。電阻值應相等于線路的實際負載差動阻抗。我們寧可高估電阻值,即使出現(xiàn)輕微的正反射也無需擔心,總比電阻值太低,令接收的訊號電壓減弱為好。電阻值的大小隨著不同的應用方案而不同,視乎線路阻抗 (無負載)、插卡之間的距離、以及加設插卡所產(chǎn)生的電容負載而定。在一般的應用情況下,這個電阻值會介于 50 至 100? 之間。若加了兩個電阻作為終端裝置,驅動器會把這兩個電阻視為平行連接,令負載介于 25 至 50? 之間。正因如此,美國國家半導體的 BLVDS 芯片所提供的驅動電流是標準 LVDS 驅動器的三倍。以 10mA 的驅動電流計,采用 BLVDS 芯片便可驅動 50? 以下的阻抗,而且可以達到采用 LVDS 芯片搭配 3mA 驅動器驅動 100? 負載時所能達到的水平。基架上的負載若互相過于緊貼,在一般情況下均會將基架阻抗減至 50? 以下。

圖 8:負載不足、相同負載及超額負載等三種終端裝置的波形

圖 8 分別顯示三個終端接收器輸入的差動波形。有負載基架的實際阻抗是 56?,所顯示的波形分別來自相同負載的終端裝置 (56?)、雙倍負載的終端裝置 (112?) 以及半載的終端裝置 (28?)。以噪聲容限作為標準衡量,相同負載及超額負載的終端裝置具有最大的噪聲容限。上述模擬采用滿載的 18 插槽多點傳輸基架進行。驅動器裝設于第 18 插槽。圖中顯示的是第 1 插槽接收器輸入的波形。

電子發(fā)燒友App

電子發(fā)燒友App

評論