安捷倫科技(Agilent Technologies)推出一款I(lǐng)nfiniiMode差動(dòng)測(cè)試探棒,這些新一代低價(jià)的1.5GHz、3.5GHz和6GHz差動(dòng)主動(dòng)式探棒可用于通用、高速的差動(dòng)探量應(yīng)用;新的測(cè)試探棒特別適合用于數(shù)位系

2012-08-23 09:04:34 1069

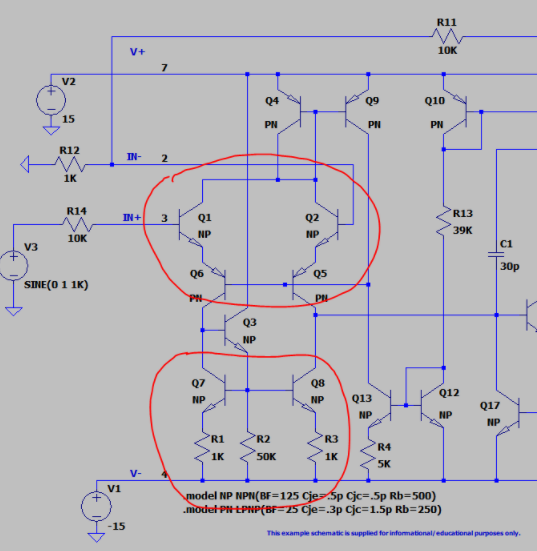

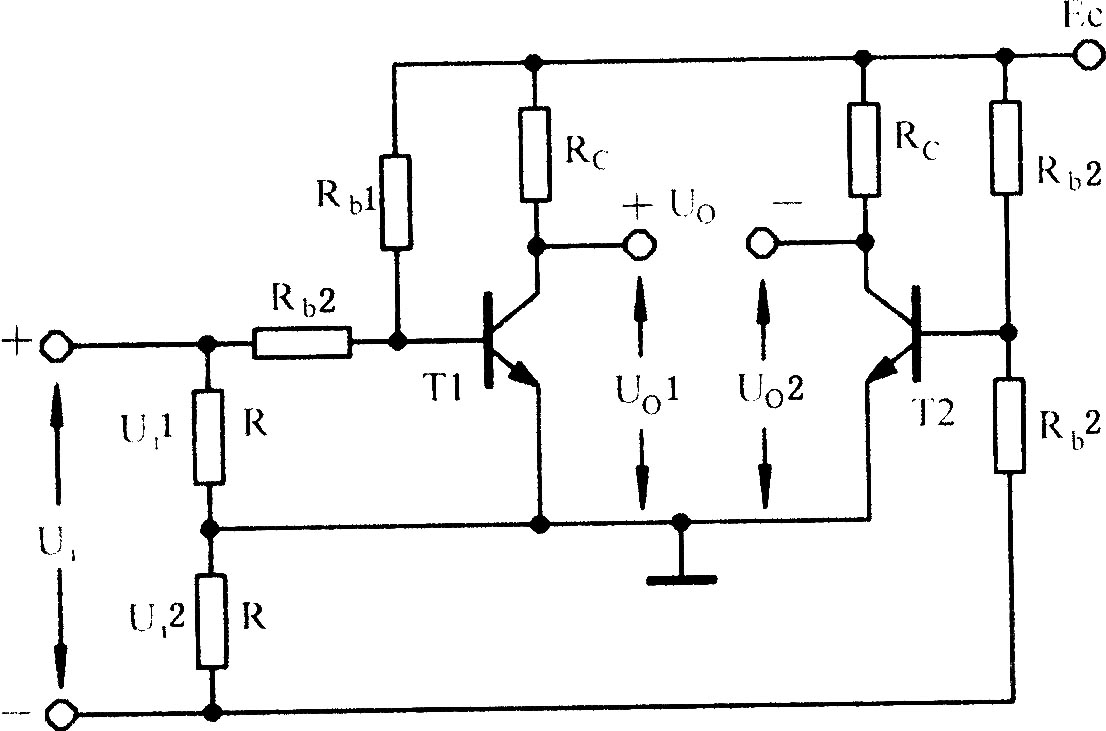

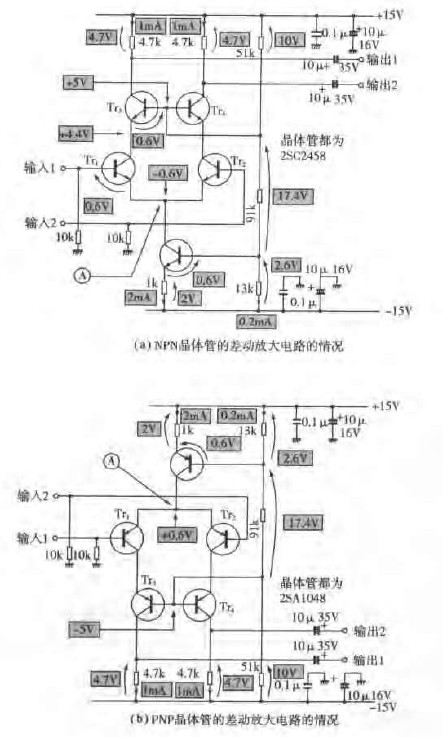

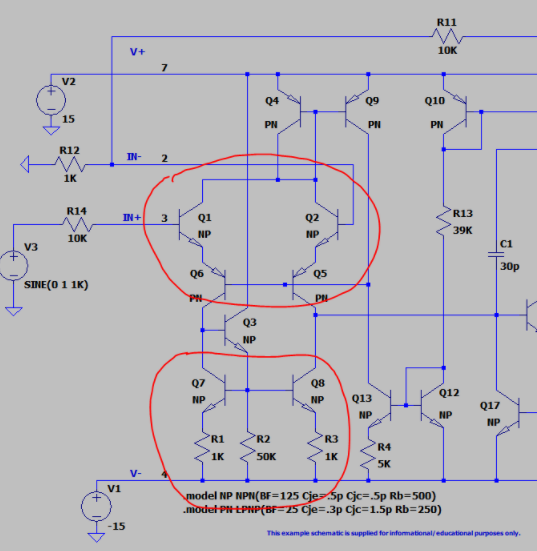

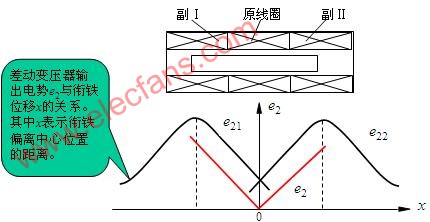

1069 首先我們來(lái)看一下放大器LM741的內(nèi)部原理圖,從741的輸入級(jí)可以看出是一個(gè)差動(dòng)輸入級(jí),而且基本上所有的放大器的輸入級(jí)都是一個(gè)差動(dòng)放大電路,下面我們就研究一下差動(dòng)放大電路。

2022-08-15 17:08:29 3713

3713

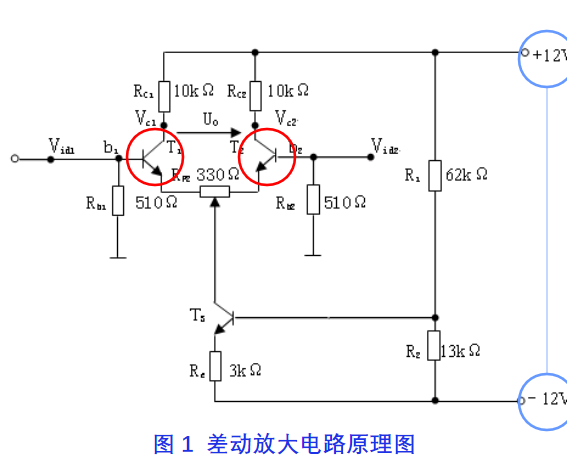

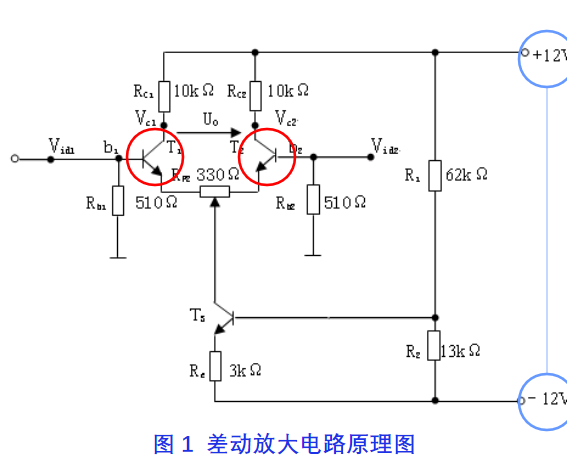

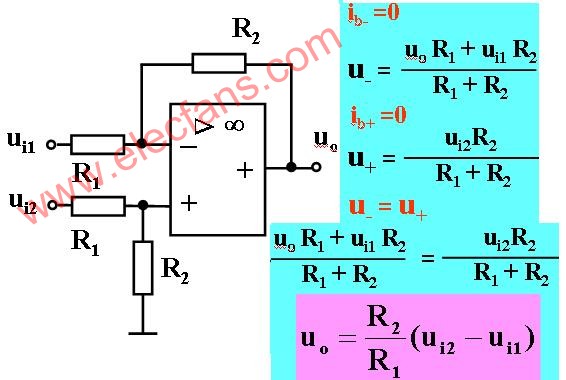

差動(dòng)放大電路原理圖分享

2023-01-30 17:46:36 1816

1816

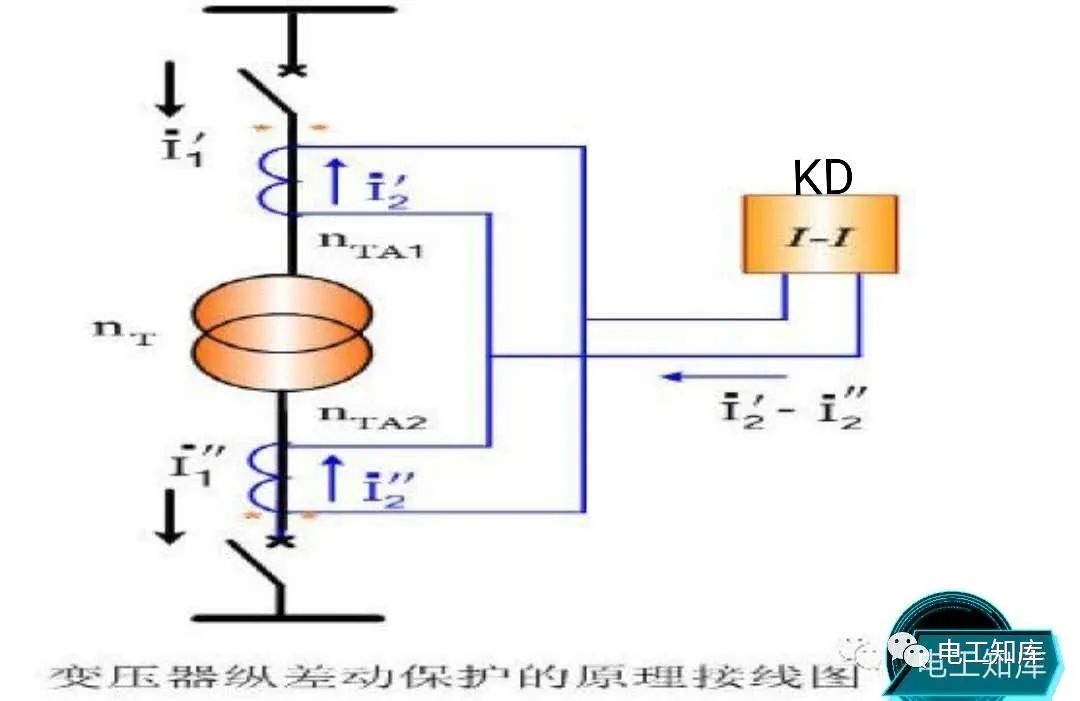

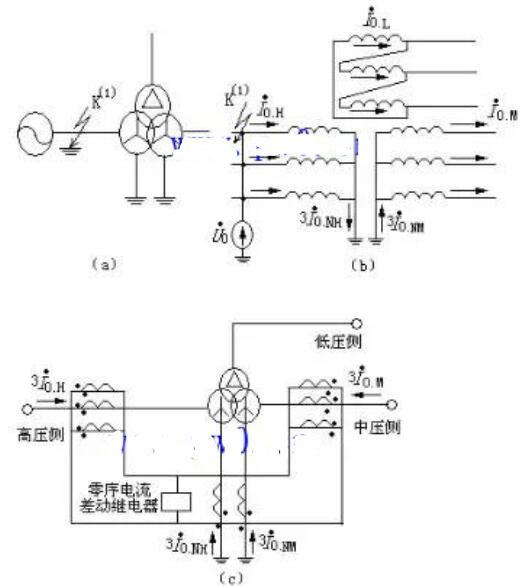

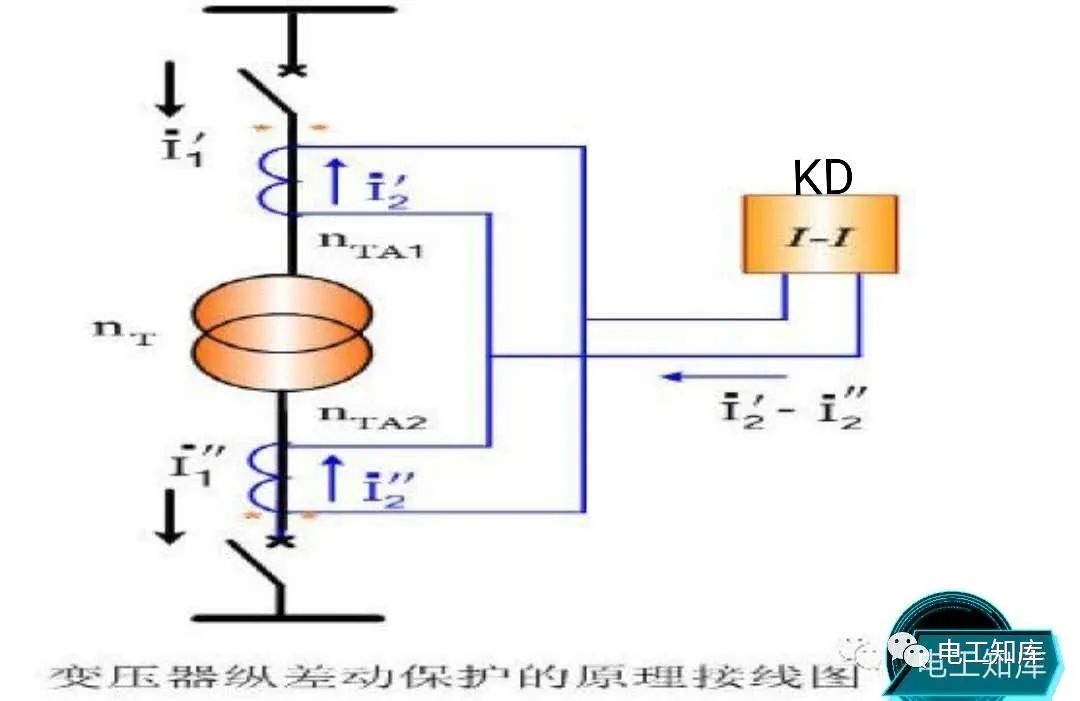

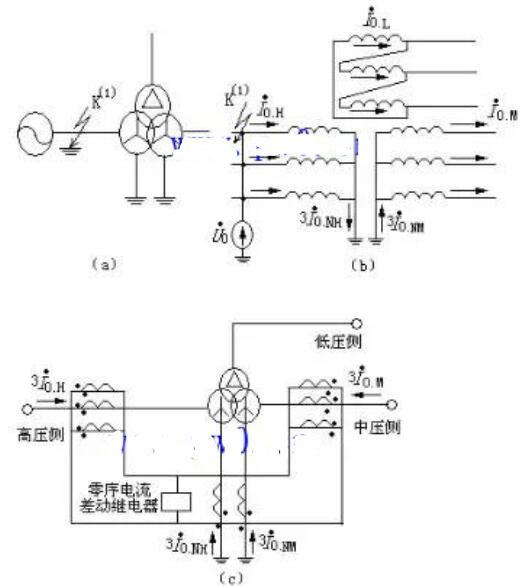

一、變壓器的差動(dòng)保護(hù) 變壓器縱聯(lián)差動(dòng)保護(hù)簡(jiǎn)稱縱差保護(hù)或差動(dòng)保護(hù),是反應(yīng)變壓器繞組、套管及引出線上各種短路故障的主保護(hù),但因它對(duì)油箱內(nèi)部的繞組匝間短路等故障反應(yīng)不靈敏,通常由縱差保護(hù)和瓦斯保護(hù)一起構(gòu)成

2023-10-11 10:11:29 2071

2071

差動(dòng)變壓器學(xué)習(xí)PPT

2020-02-13 17:21:58

是否有差分輸入、單端輸出,300M帶寬的差動(dòng)放大器

2012-06-10 21:00:29

我想設(shè)計(jì)采集200~300MHz的信號(hào)的系統(tǒng),首先2路反相的信號(hào)輸入差動(dòng)放大器,然后差動(dòng)放大器輸出接1G采樣率的高速采集卡,接著當(dāng)采集到信號(hào)高于某一閾值時(shí)將其輸出到電腦里,其他時(shí)間采集的的信號(hào)不輸出。我想請(qǐng)問(wèn)這樣設(shè)計(jì)是否合理,差動(dòng)放大器應(yīng)該怎么選擇,高速采集卡只輸出大于某一閾值的信號(hào)能否實(shí)現(xiàn)

2012-06-09 22:18:09

差動(dòng)放大器和電流檢測(cè)放大器附件差動(dòng)放大器和電流檢測(cè)放大器.pdf329.1 KB

2018-11-05 09:10:37

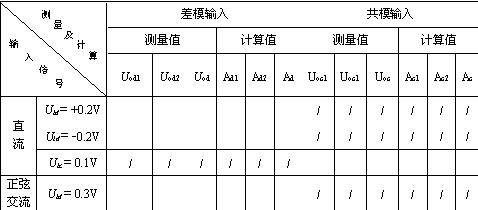

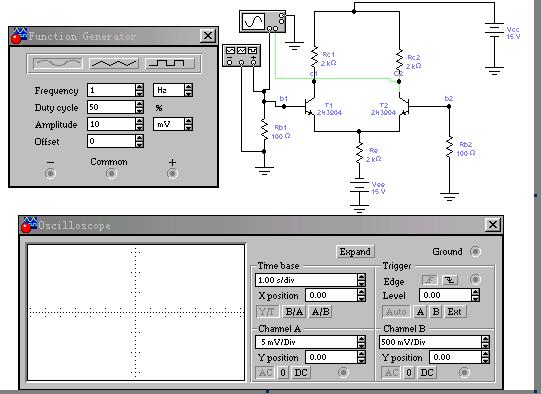

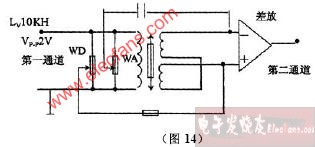

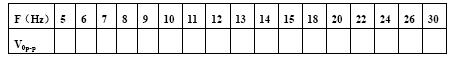

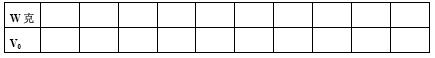

差動(dòng)放大電路加深理解差動(dòng)放大器的工作原理;學(xué)習(xí)差動(dòng)放大器共模抑制比的測(cè)量方法;掌握提高差動(dòng)放大器共模抑制比的方法;差動(dòng)放大器是一種零點(diǎn)漂移非常小的直接耦合放大器。由于電路結(jié)構(gòu)的盡可能對(duì)稱性,使其具有

2009-09-08 08:52:26

實(shí)驗(yàn)四 A 差動(dòng)放大電路實(shí)驗(yàn)差動(dòng)放大電路 (3)熟悉電路圖結(jié)構(gòu),并在實(shí)驗(yàn)箱上連接電路。(4)±12v電源內(nèi)部已接好。(5)按準(zhǔn)備報(bào)告的要求去作。(6)用萬(wàn)用表直流電壓檔測(cè)試靜態(tài)工作點(diǎn),調(diào)節(jié)RP使

2009-03-18 20:18:40

`差動(dòng)電感脈沖調(diào)寬電路`

2011-03-13 21:39:25

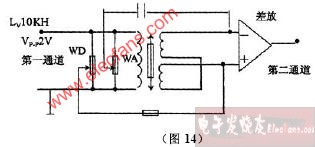

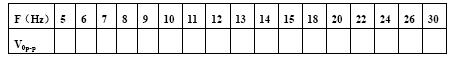

差動(dòng)脈沖調(diào)寬電路圖 4-2-8 差動(dòng)脈沖調(diào)寬電路

2011-03-13 21:38:43

高速DAP仿真器 BURNER

2023-03-28 13:06:20

描述此參考設(shè)計(jì)展示了高速放大器 LMH6554 執(zhí)行單端至差動(dòng)轉(zhuǎn)換以驅(qū)動(dòng)高速模擬至數(shù)字轉(zhuǎn)換器 (ADC),同時(shí)保持卓越的噪聲和失真性能的能力。為交流和直流耦合應(yīng)用顯示了連接到 ADS4449 四通

2018-08-03 06:00:28

高速無(wú)線調(diào)試器HSWLDBG BURNER 3.3,5

2023-03-28 13:06:20

AD7265采用差動(dòng)和單端配置的12位,3通道SAR ADC,采用AD8022高速運(yùn)算放大器。 AD8022直流耦合電路,將雙極性單端信號(hào)轉(zhuǎn)換為單極性差分信號(hào)

2019-06-17 13:05:07

ADS1211接成差動(dòng)輸入 ,不適用BIAS那個(gè)引腳的話 ,輸入的差動(dòng)電壓 是多少啊?

輸入端口相對(duì)于地的電壓 要高多少呢?

2023-12-25 08:01:42

LED燈具設(shè)計(jì)的幾個(gè)關(guān)鍵秘訣,需要完整版的小伙伴可以下載附件。

2021-08-19 10:58:59

本帖最后由 yixuanba 于 2015-11-6 15:39 編輯

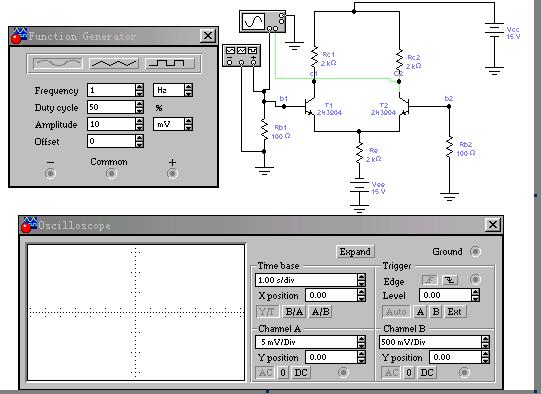

LM324 差動(dòng)仿真異常!請(qǐng)各位幫我看下,是什么問(wèn)題?

2015-11-05 16:42:38

Labview開(kāi)發(fā)技術(shù)叢書(shū)--LabVIEW界面設(shè)計(jì)秘訣

2016-09-02 18:03:55

labview界面設(shè)計(jì)秘訣

2015-02-17 14:36:35

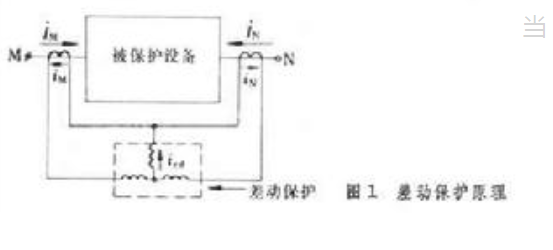

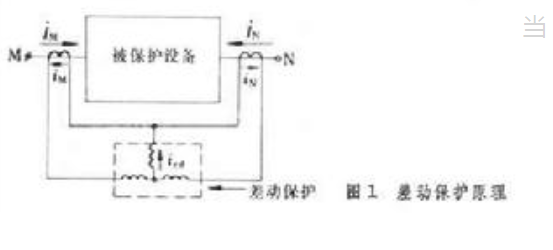

1、什么是差動(dòng)保護(hù)差動(dòng)保護(hù)的基本原理是基爾霍夫定律,即“電路中流入節(jié)點(diǎn)電流的總和等于零”。差動(dòng)保護(hù)把被保護(hù)的電氣設(shè)備看成是一個(gè)節(jié)點(diǎn),正常時(shí)流進(jìn)被保護(hù)設(shè)備的電流和流出的電流相等,差動(dòng)電流等于零。當(dāng)設(shè)備

2021-07-07 08:04:44

使用示波器進(jìn)行功率測(cè)量的7大秘訣你知道嗎?

2021-05-08 09:32:09

1、什么是差動(dòng)保護(hù) 差動(dòng)保護(hù)的基本原理是基爾霍夫定律,即“電路中流入節(jié)點(diǎn)電流的總和等于零”。差動(dòng)保護(hù)把被保護(hù)的電氣設(shè)備看成是一個(gè)節(jié)點(diǎn),正常時(shí)流進(jìn)被保護(hù)設(shè)備的電流和流出的電流相等,差動(dòng)電流等于零。當(dāng)

2021-06-30 07:58:55

,從而成為鄰近電路的巨大電磁干擾源(EMI)。 差動(dòng)信號(hào)傳輸使用由兩條導(dǎo)線組成的信號(hào)對(duì):一個(gè)用于正向電流,而另一個(gè)用于返回電流。每個(gè)信號(hào)導(dǎo)線均有一個(gè)共模電壓 VCM,其由 50% 差動(dòng)驅(qū)動(dòng)器輸出 VOD

2018-09-19 14:38:04

單端接口與差動(dòng)接口的區(qū)別在哪里?

2021-05-18 06:35:20

變壓器差動(dòng)保護(hù)的工作原理是什么?變壓器差動(dòng)保護(hù)與線路差動(dòng)保護(hù)的區(qū)別在哪?變壓器縱差動(dòng)保護(hù)的特點(diǎn)有哪些?

2021-09-23 09:20:29

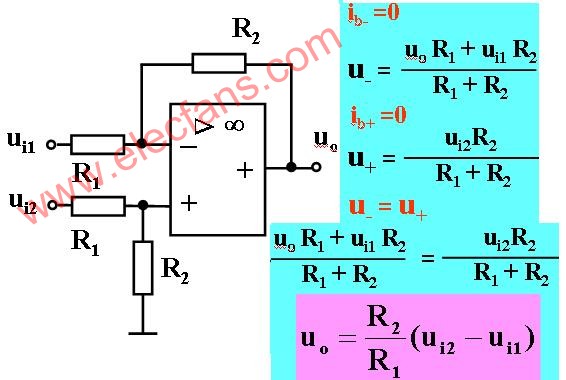

經(jīng)典的分立差動(dòng)放大器設(shè)計(jì)非常簡(jiǎn)單,一個(gè)運(yùn)算放大器和四電阻網(wǎng)絡(luò)有何復(fù)雜之處?經(jīng)典的四電阻差動(dòng)放大器性能可能不像設(shè)計(jì)人員想要的那么好。從實(shí)際生產(chǎn)設(shè)計(jì)出發(fā),分立電阻有什么缺點(diǎn)?

2019-07-30 07:28:28

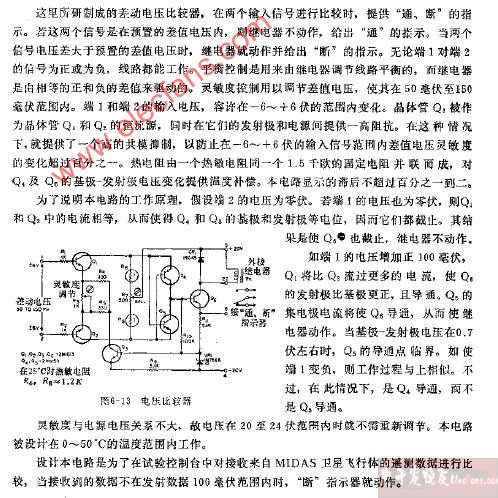

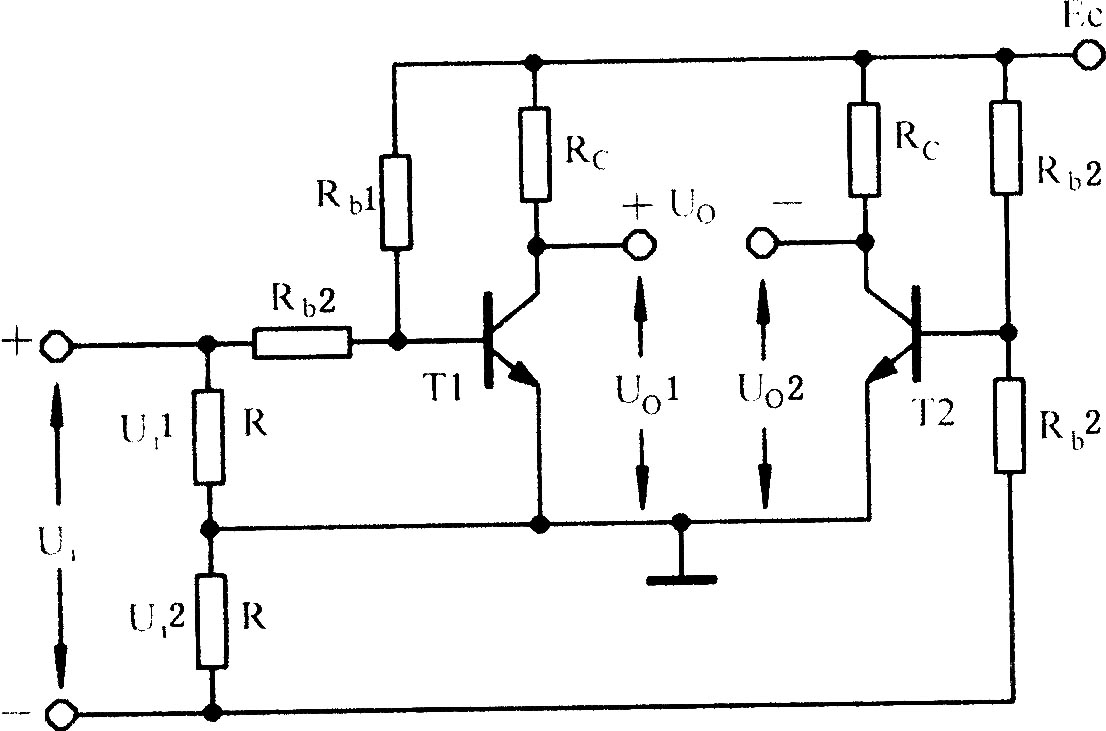

差動(dòng)放大電路也稱差分放大電路,是一種對(duì)零點(diǎn)漂移具有很強(qiáng)抑制能力的基本放大電路。差動(dòng)放大原理電路如圖Z0501所示。它由兩個(gè)對(duì)稱的共射極基本放大電路組成:其中,T1、T2是兩個(gè)特性完全相同的晶體管、Rb1=Rb2、...

2021-04-13 07:45:03

嵌入式軟件測(cè)試的秘訣:1、懂的使用工具;2、盡早發(fā)現(xiàn)內(nèi)存問(wèn)題(指針越界,數(shù)據(jù)類型超限等);3、深入理解代碼優(yōu)化;4、重現(xiàn)并隔離問(wèn)題;5、確定測(cè)試的完整性;6、利用初學(xué)者的思維,去發(fā)現(xiàn)問(wèn)題。...

2021-10-27 07:38:11

工程師使用示波器執(zhí)行功率測(cè)量有什么秘訣分享嗎?

2021-05-10 07:06:10

開(kāi)關(guān)電源設(shè)計(jì)秘訣,需要完整版的朋友可以下載附件保存哦~一鍵分析設(shè)計(jì)隱患,首款國(guó)產(chǎn)PCB DFM分析軟件免費(fèi)用!地址下載(電腦端下載):https://dfm.elecfans.com/uploads

2021-09-06 09:54:02

新的13 Gbps / 13 GHz + 3.3V高速邏輯系列

2019-04-28 11:39:26

`模擬電路實(shí)驗(yàn)--差動(dòng)放大電路實(shí)驗(yàn)[hide][/hide]`

2017-03-15 16:33:22

求助基于模糊控制的雙輪差動(dòng)小車避障的設(shè)計(jì),需用matlab simulink,謝謝{:soso_e100:}

2012-03-28 04:33:19

電動(dòng)機(jī)差動(dòng)保護(hù)基本原理 電動(dòng)機(jī)差動(dòng)保護(hù)基本原理為檢測(cè)電動(dòng)機(jī)始末端的電流,比較始端電流和末端電流的相位和幅值的原理而構(gòu)成的。正常情況下,二者的差流為零,即流入電動(dòng)機(jī)的電流等于流出電動(dòng)機(jī)的電流,當(dāng)

2023-03-02 14:11:26

,工程師必須不定期地對(duì)探頭執(zhí)行消磁處理,以消除探頭核心的殘余磁性,并補(bǔ)償鉗形電流探頭的直流偏置。秘訣5 使用差動(dòng)探頭執(zhí)行安全浮動(dòng)點(diǎn)測(cè)量示波器使用者經(jīng)常需要執(zhí)行浮動(dòng)點(diǎn)測(cè)量。在這種測(cè)量中,任何測(cè)量點(diǎn)都不能潛在

2020-02-17 11:00:30

示波器用于功率測(cè)量時(shí)的7大秘訣

2012-08-06 13:09:22

示波器用于功率測(cè)量時(shí)的7大秘訣

2012-08-08 14:46:34

示波器用于功率測(cè)量時(shí)的7大秘訣

2012-08-18 08:45:40

編寫(xiě)無(wú)錯(cuò)C程序秘訣。

2012-08-15 23:48:49

編程精粹Microsoft編寫(xiě)優(yōu)質(zhì)無(wú)錯(cuò)C程序秘訣 原文書(shū)名:《Writing Clean Code ── Microsoft Techniques for Developing

2009-10-26 18:27:53

ADS1211 接成差動(dòng)輸入 ,不適用BIAS那個(gè)引腳的話 ,輸入的差動(dòng)電壓 是多少啊?輸入端口相對(duì)于地的電壓 要高多少呢?

2018-11-14 09:33:03

高壓電動(dòng)機(jī)縱差動(dòng)保護(hù)工作原理與變壓器縱差動(dòng)保護(hù)相似嗎?電力網(wǎng)的電力線路按用途一般可分為哪幾種?電流互感器有何作用?怎樣去計(jì)算電路中負(fù)載消耗的電能W呢?

2021-09-15 07:52:57

DCD-2A型差動(dòng)繼電器1用途DCD-2A 型差動(dòng)繼電器(以下簡(jiǎn)稱繼電器)用于兩繞組或三繞組電力變壓器以及交流發(fā)電機(jī)的單相差動(dòng)保護(hù)線路中,作為主保護(hù)。繼電器能預(yù)防在非故障狀

2009-11-24 16:19:42 14

14 DCD-2A 型差動(dòng)繼電器1 用途DCD-2A 型差動(dòng)繼電器(以下簡(jiǎn)稱繼電器)用于兩繞組或三繞組電力變壓器以及交流發(fā)電機(jī)的單相差動(dòng)保護(hù)線路中作為主保護(hù)繼電器能預(yù)防在非故障狀

2009-11-25 10:51:03 19

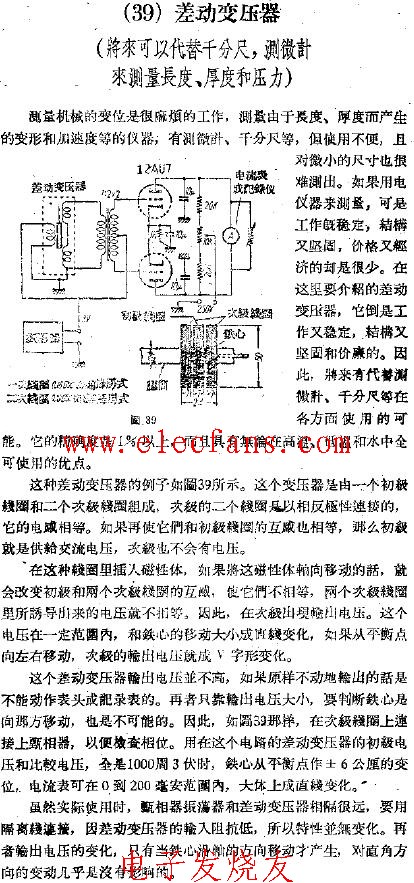

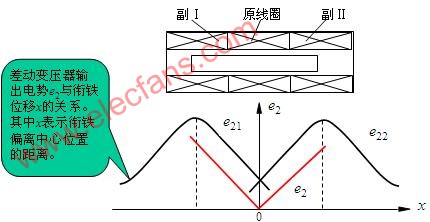

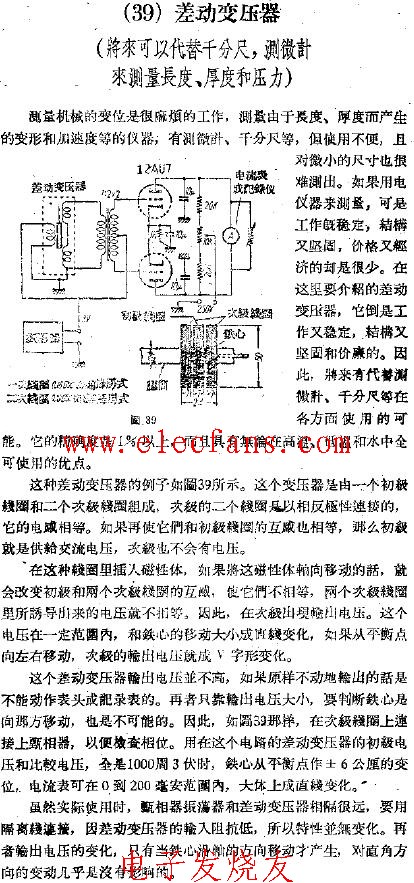

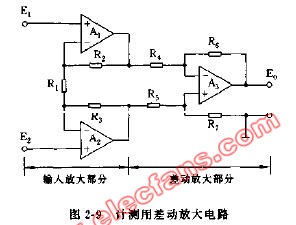

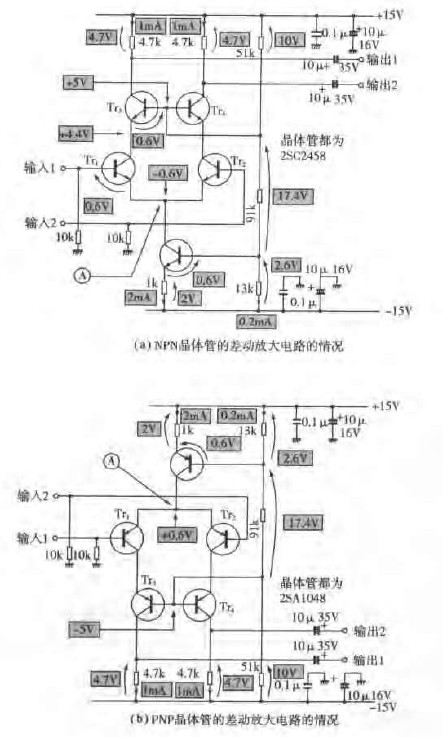

19 差動(dòng)變壓器的輸出電壓是調(diào)幅波,為了辨別銜鐵的移動(dòng)方向,需要進(jìn)行解調(diào)。常用的解調(diào)電路有:差動(dòng)相敏檢波電路與差動(dòng)整流電路。采用相敏檢波的差動(dòng)變壓器測(cè)量電路框圖如圖1

2010-04-23 08:13:36 18

18 目 錄秘訣 1. 快速完成一般任務(wù)的簡(jiǎn)易要訣 2秘訣 2. 函數(shù)波形產(chǎn)生器輸出的電壓為何是設(shè)定值的兩倍 3秘訣 3. 產(chǎn)生任意波形的兩種簡(jiǎn)易方法 4秘訣 4. 運(yùn)用函數(shù)/任意波形

2010-07-23 21:35:26 25

25 對(duì)差動(dòng)保護(hù)進(jìn)行相關(guān)檢查、試驗(yàn)如下: 1、檢查BCH-2型差動(dòng)繼電器與定值單相符,對(duì)差動(dòng)繼電器進(jìn)行檢查、檢驗(yàn)合格。

2010-10-25 16:16:18 24

24

差動(dòng)變壓器電路

2008-04-30 00:24:32 1150

1150

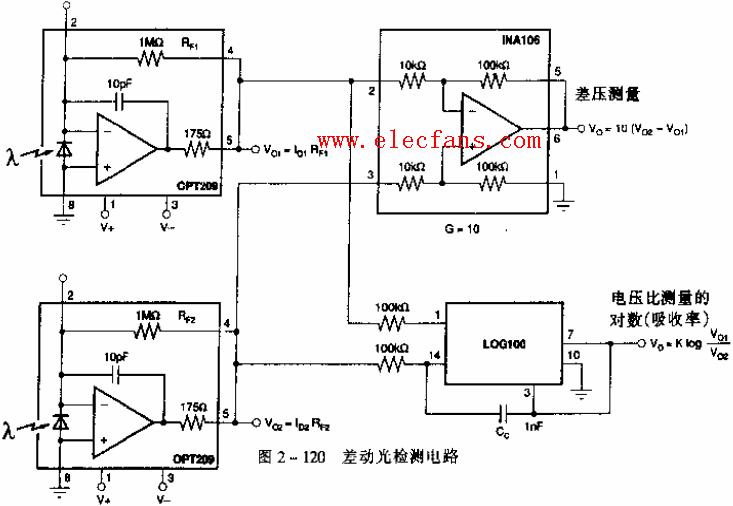

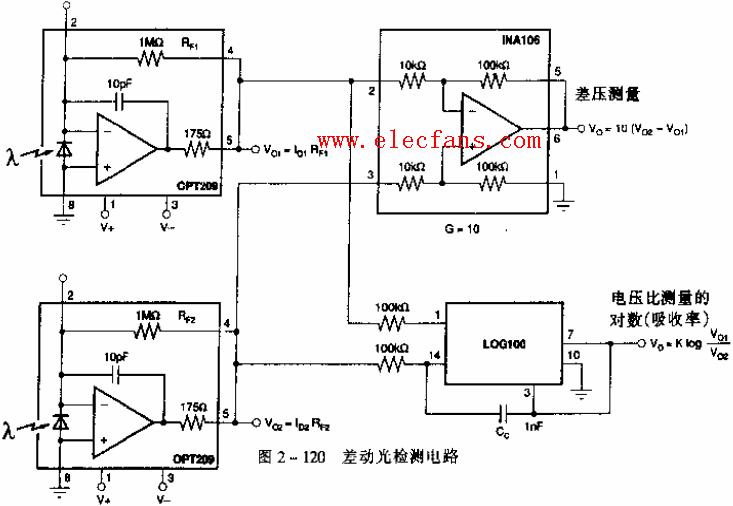

差動(dòng)光檢測(cè)電路

2008-05-15 09:39:16 575

575

差動(dòng)放大器實(shí)驗(yàn)

2008-09-27 17:11:24 10547

10547

變壓器的差動(dòng)保護(hù)

變電所的主變微機(jī)差動(dòng)保護(hù).(1)電磁式繼電器構(gòu)成的變壓器差動(dòng)保護(hù)在正常情況和外部故障時(shí),

2008-10-07 08:44:56 1104

1104 差動(dòng)放大電路

實(shí)驗(yàn)?zāi)康?、加深對(duì)差動(dòng)放大電路工作原理及特點(diǎn)的理解,了解零點(diǎn)漂移產(chǎn)生的原因與抑制零漂的方式。2、學(xué)習(xí)差動(dòng)放

2008-12-05 22:27:51 17436

17436

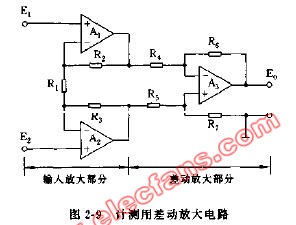

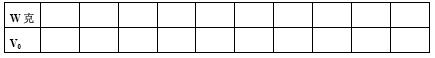

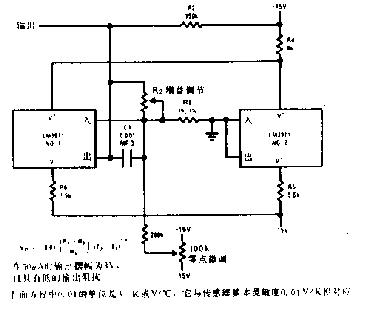

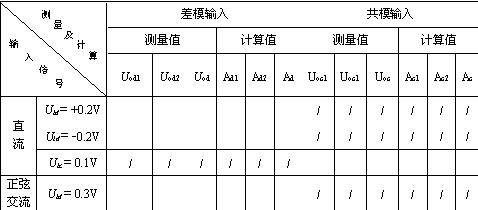

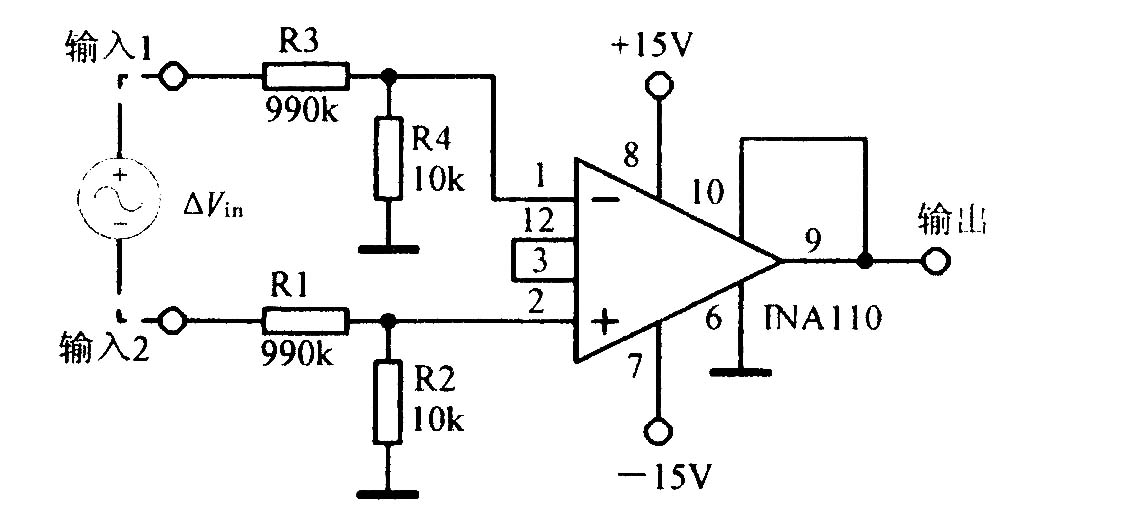

計(jì)測(cè)用差動(dòng)放大電路圖

2008-12-17 14:23:17 679

679

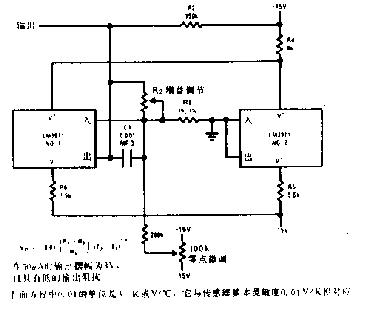

實(shí)驗(yàn) 差動(dòng)變壓器零殘電壓的補(bǔ)償

實(shí)驗(yàn)?zāi)康模河捎诹銡堧妷旱拇嬖跁?huì)造成差動(dòng)變壓器零點(diǎn)附近的不靈敏區(qū),此電壓經(jīng)過(guò)放大器還會(huì)使放大

2009-03-06 15:43:47 2905

2905

實(shí)驗(yàn) 差動(dòng)變壓器的振動(dòng)測(cè)量實(shí)驗(yàn)?zāi)康模毫私?b class="flag-6" style="color: red">差動(dòng)變壓器的實(shí)際運(yùn)用情況。實(shí)驗(yàn)所需部件:差動(dòng)變壓器、音頻信號(hào)源、電感傳感器實(shí)驗(yàn)?zāi)K、公共電路實(shí)

2009-03-06 15:45:32 6386

6386

實(shí)驗(yàn) 差動(dòng)變壓器的應(yīng)用—電子秤

實(shí)驗(yàn)所需部件:差動(dòng)變壓器、電感傳感器實(shí)驗(yàn)?zāi)K、公共電路實(shí)驗(yàn)?zāi)K、電壓表、振動(dòng)平臺(tái)、砝碼

2009-03-06 15:46:13 2432

2432

高共模電壓的差動(dòng)放大電路圖

2009-04-02 16:01:33 1875

1875

差動(dòng)溫度計(jì)電路圖

2009-04-13 09:23:34 2332

2332

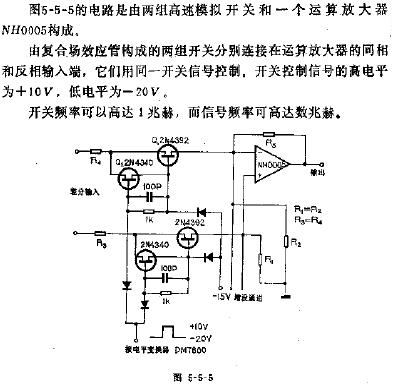

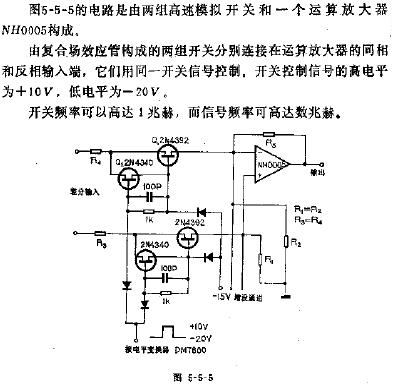

高速差動(dòng)模擬開(kāi)關(guān)

2009-04-13 10:48:07 958

958

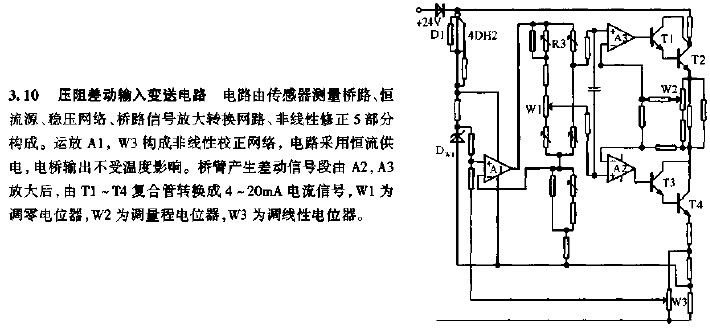

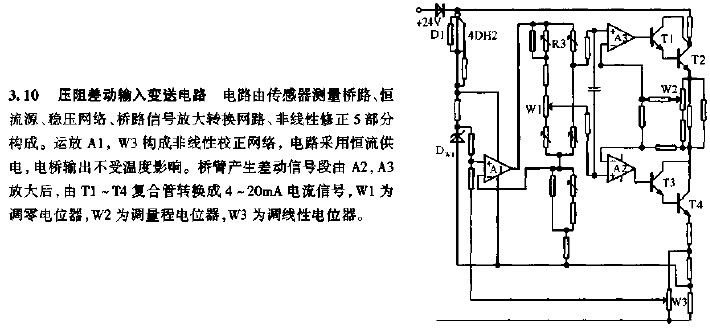

壓阻差動(dòng)輸入變送電路

2009-04-21 21:14:52 842

842

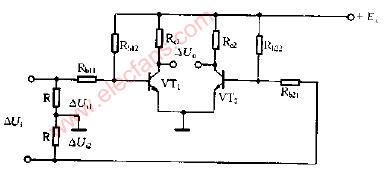

差動(dòng)放大基本電路圖

2009-05-07 12:47:01 2074

2074

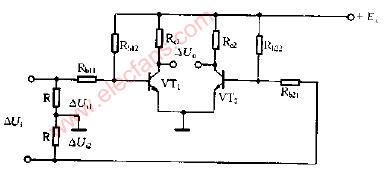

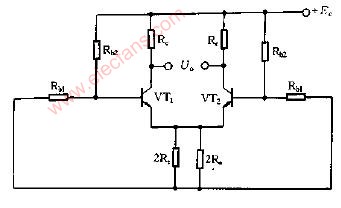

射極耦合差動(dòng)電路圖

2009-05-07 12:52:03 844

844

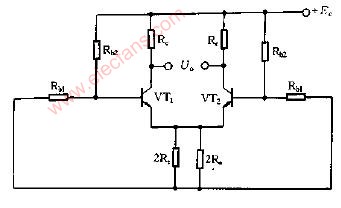

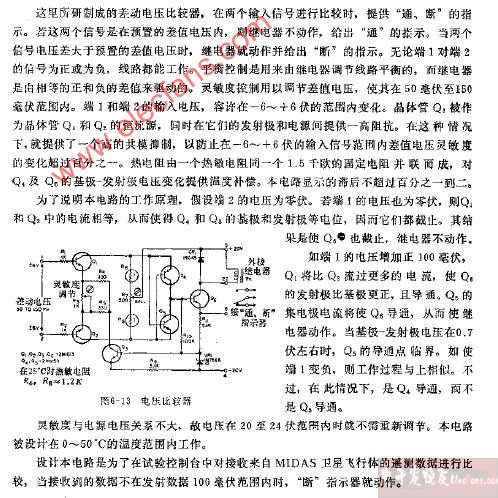

差動(dòng)電壓比較器電路圖

2009-06-27 09:53:32 2840

2840

什么是差動(dòng)放大電路

差動(dòng)放大電路又叫差分電路,他不僅能有效的放大直流信號(hào),而且能有效的減小由于電源波動(dòng)和晶體管隨溫度變化多引起的零

2009-07-05 09:49:14 2261

2261

渥爾曼化后的差動(dòng)放大電路圖

2009-08-04 10:48:19 2069

2069

延長(zhǎng)充電電池壽命的秘訣

延長(zhǎng)充電電池壽命的秘訣有以下幾點(diǎn):

● 儲(chǔ)藏溫度:一般情況下,電池由于內(nèi)

2009-11-04 15:45:51 773

773 變壓器差動(dòng)保護(hù)知識(shí)

論述變壓器的差動(dòng)保護(hù)、標(biāo)積制動(dòng)差動(dòng)保護(hù)、零序差動(dòng)保護(hù)等主保護(hù)在使用中應(yīng)注意的技術(shù)問(wèn)題,指出差動(dòng)

2009-12-11 11:13:37 1041

1041 關(guān)于變壓器差動(dòng)保護(hù)的幾個(gè)觀點(diǎn)

論述變壓器的差動(dòng)保護(hù)、標(biāo)積制動(dòng)差動(dòng)保護(hù)、零序差動(dòng)保護(hù)等主保護(hù)在使用中應(yīng)注意的技術(shù)問(wèn)題

2009-12-12 09:29:22 834

834 差動(dòng)變壓器的結(jié)構(gòu)原理與等效電路

分氣隙型和差動(dòng)變壓器兩種。目前多采用螺管型差動(dòng)變壓器。其基本元件有銜鐵、初級(jí)線圈、次

2010-02-06 08:41:03 7175

7175

主變差動(dòng)保護(hù)防誤動(dòng)分析

1 引言

主變差動(dòng)保護(hù)是變壓器的主要保護(hù)手段,基本原理是反應(yīng)被保護(hù)變壓器各端流入和流出電流的差,在保護(hù)區(qū)內(nèi)故障,差動(dòng)回路中

2010-04-11 18:22:43 1103

1103

差動(dòng)放大電路圖

2010-04-13 10:28:45 1360

1360

怎樣才能做出一套自己心滿意足的音箱呢?本文介紹十個(gè)秘訣

秘訣一:喇叭單元選擇合適的單元口徑,了解單元的

2010-08-27 10:01:39 7357

7357 THS770012具有從10dB到13dB的可選增益的高速全差動(dòng)ADC驅(qū)動(dòng)器放大器

2011-02-06 11:11:37 1512

1512

每一到兩季就會(huì)買下一家公司的半導(dǎo)體購(gòu)并王博通(Broadcom)又有新動(dòng)作!10余年來(lái)不間斷的購(gòu)并策略,提供了博通高速成長(zhǎng)的動(dòng)力。博通購(gòu)并的成功秘訣到底是什么?

2011-12-30 09:16:56 944

944 LabVIEW 界面設(shè)計(jì)秘訣對(duì)想做漂亮LV界面的童鞋來(lái)說(shuō)是有用的。

2016-05-17 16:41:51 108

108 今天早晨起床看朋友圈里全是換敬業(yè)福,買敬業(yè)福,送敬業(yè)福,別out了,告訴你個(gè)秘訣這樣就可以啦!

2017-01-24 08:43:00 3770

3770 信號(hào)完整性設(shè)計(jì)秘訣

2018-01-15 15:19:30 0

0 差動(dòng)液壓缸左右兩腔壓力相等,但無(wú)桿腔的有效面積大于有桿腔,因此作用力大,活塞由無(wú)桿腔向有桿腔運(yùn)動(dòng),差動(dòng)時(shí)有桿腔的油液回到無(wú)桿腔,流量增大,所以速度變快。比如一般的油缸伸出速度為4Q/πD2,那么差動(dòng)時(shí)速度就為4Q/πd2,可以看出差動(dòng)回路的速度快。

2018-02-24 13:53:47 65187

65187

差動(dòng)保護(hù)把被保護(hù)的電氣設(shè)備看成是一個(gè)節(jié)點(diǎn),那么正常時(shí)流進(jìn)被保護(hù)設(shè)備的電流和流出的電流相等,差動(dòng)電流等于零。當(dāng)設(shè)備出現(xiàn)故障時(shí),流進(jìn)被保護(hù)設(shè)備的電流和流出的電流不相等,差動(dòng)電流大于零。當(dāng)差動(dòng)電流大于差動(dòng)保護(hù)裝置的整定值時(shí),上位機(jī)報(bào)警保護(hù)出口動(dòng)作,將被保護(hù)設(shè)備的各側(cè)斷路器跳開(kāi),使故障設(shè)備斷開(kāi)電源。

2018-02-24 14:01:52 39029

39029

線路電流差動(dòng)保護(hù)的基礎(chǔ)是線路的RL集中參數(shù)模型和電荷連續(xù)性。行波差動(dòng)保護(hù)的基礎(chǔ)是線路的分布參數(shù)模型和行波傳輸不變性。針對(duì)兩類差動(dòng)保護(hù)在電力線路上的應(yīng)用進(jìn)行了詳細(xì)的理論和仿真對(duì)比研究。指出二者的根本

2018-03-01 15:32:09 0

0 零序電流差動(dòng)保護(hù)同樣廣泛采用比率制動(dòng)特性,其整定原則應(yīng)躲過(guò)正常運(yùn)行或外部相間故障情況下的最大不平衡電流,具體計(jì)算方法與差動(dòng)保護(hù)類似。值得注意的是,零序電流差動(dòng)保護(hù)的保護(hù)范圍只包含有電路連接的變壓器

2019-10-21 10:11:38 15305

15305

ADA4830-1/ADA4830-2:高速差動(dòng)放大器,輸入具有電池短路保護(hù)功能

2021-03-19 01:56:30 6

6 差動(dòng)放大電路組成

2022-07-04 15:04:39 0

0 直流無(wú)刷電機(jī)驅(qū)動(dòng)器芯片挑選的秘訣

2022-07-06 10:24:26 3198

3198 差動(dòng)測(cè)試棒提供一個(gè)安全的絕緣儀器給示波器使用,它可以轉(zhuǎn)換由高輸入的差動(dòng)電壓進(jìn)入一個(gè)低電壓并且顯示波形在示波器上,使用頻率高達(dá)100MHz,非常適合大電力測(cè)試、研發(fā)使用。 差動(dòng)測(cè)試棒輸出標(biāo)是設(shè)計(jì)在操作

2022-08-16 15:31:29 767

767

能量采集的秘訣:樹(shù)懶和熊

2022-11-04 09:50:48 0

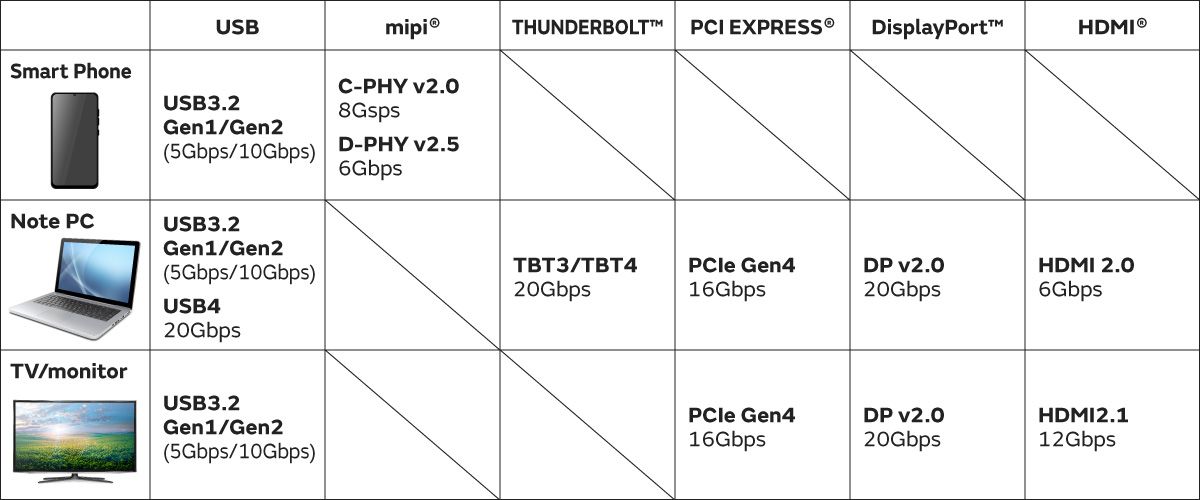

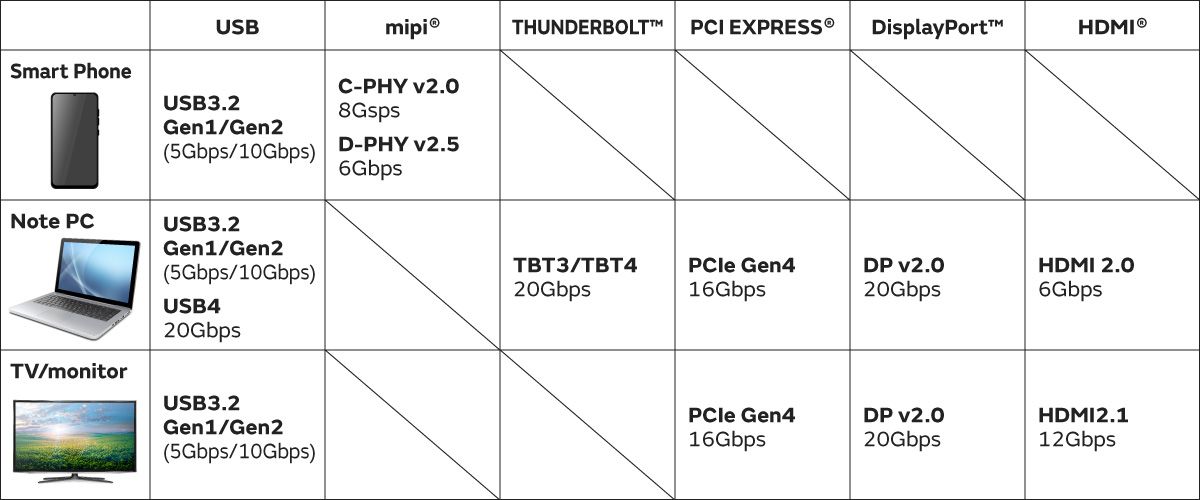

0 ,Wi-Fi作為常用的無(wú)線通信方式得以普及。 ? 2. 差動(dòng)接口的噪聲問(wèn)題 隨著差動(dòng)接口的高速化與無(wú)線通信的普及,內(nèi)部系統(tǒng)EMC備受關(guān)注。 內(nèi)部系統(tǒng)EMC:USB3.2發(fā)出的噪聲干擾設(shè)備內(nèi)的Wi-Fi天線,使Wi-Fi通信質(zhì)量劣化的現(xiàn)象 針對(duì)標(biāo)準(zhǔn)規(guī)格的EMC:設(shè)備主體及

2023-01-31 15:30:23 254

254

的問(wèn)題SingleReferencePlane高速差動(dòng)信號(hào)的走線需參考單一的Groundreference而不是有斷裂(Split)或是有撈空(Void)的groundref

2022-09-20 09:42:55 611

611

差動(dòng)放大電路和差分放大電路一樣嗎 差動(dòng)放大電路和差分放大電路是兩種不同的電路原理,差動(dòng)放大電路可以被認(rèn)為是差分放大電路的一種特例。雖然兩種電路有許多相似之處,但它們的不同之處是很重要的。在這

2023-08-27 16:13:19 5039

5039 變壓器差動(dòng)保護(hù)動(dòng)作的原因 變壓器差動(dòng)保護(hù)是保障變壓器安全穩(wěn)定運(yùn)行的一項(xiàng)重要保護(hù)措施,其主要作用是在變壓器運(yùn)行中監(jiān)測(cè)變壓器的差動(dòng)電流,一旦發(fā)現(xiàn)差動(dòng)電流超出設(shè)定范圍,就會(huì)觸發(fā)差動(dòng)保護(hù)器動(dòng)作,從而及時(shí)斷開(kāi)

2023-09-27 15:45:38 2742

2742 電路板的長(zhǎng)壽秘訣:如何保養(yǎng)PCB

2023-12-07 14:54:01 445

445

正在加载...

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論