高速轉換器三種最常用的數字輸出是互補金屬氧化物半導體(CMOS)、低壓差分信號(LVDS)和電流模式邏輯(CML)。

2015-02-04 11:20:34 832

832

本篇主要介紹LVDS、CML、LVPECL三種最常用的差分邏輯電平之間的互連。 下面詳細介紹第二部分:不同邏輯電平之間的互連。 1、LVPECL的互連 1.1、LVPECL到CML的連接 一般情況下

2020-12-20 11:49:31 20435

20435

分:同種邏輯電平之間的互連。 ? 輸入 ? ? CML PECL LVDS 輸出 CML √ √直流、交流耦合 √直流、交流耦合 PECL √直流、交流耦合 √直流、交流耦合 √直流、交流耦合 LVDS √直流、交流耦合 √直流、交流耦合 √ 1、LVDS到LVDS的連接 1.1、直流匹配 LVDS直接是可

2020-12-20 11:39:59 35579

35579

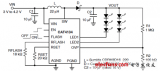

列舉了最常用的幾種差分信號技術和它們的主要參數。 下面講一講各信號模式之間的轉換: LVPECL到CML的轉換 如圖1所示,在LVPECL驅動器輸出端向GND處放置一個150Ω的電阻對于開路發射極提供直流偏置以及到GND的直流電流路徑至關重要。為了將800mV LVPECL擺幅衰減到400mV的CM

2021-10-27 15:59:00 6320

6320 的價格。為了支持這一需求,我們正在努力開發新技術,進一步優化可實現這些顯示屏的 LED 驅動器。今年年初,TI 推出了業界第一個 48 輸出(48 通道)LED 標牌顯示器驅動器產品系列。TLC5954

2018-09-12 14:37:21

隔離電源轉換器詳解柵極驅動器解決方案選項最優隔離柵極驅動器解決方案

2021-03-08 07:53:35

我想知道Vivado IO約束(XDC)的規則是否同樣適用于由FPGA驅動的LVDS信號的pos(_P)和neg(_N)?我是否為此LVDS輸出的_P和_N指定IO位置約束?另外,我認為LVDS輸出

2020-05-11 07:13:50

率超過155.5 Mbps(77.7 MHz)。MS90C031將接TTL/CMOS輸入信號,轉換成低壓(350mV)的差分輸出信號。芯片驅動器還支持三態輸出功能,可以用來關斷輸出驅動級,通過關斷輸出

2022-01-05 11:30:34

LVDS用戶手冊-包含高速CML和信號調理內容LVDS技術已在通信網絡中得到普及,廣泛用于漆上計算機,辦公用成像,工業視覺,測試與測量,醫療和汽車等領域。 [hide]LVDS用戶手冊.rar[/hide]

2009-10-22 11:02:40

作者:Yuriy Kurtsevoy, 戰略應用工程師引言數字輸出驅動器廣泛用于工業應用中的過程控制(PLC系統)和樓宇自動化,也可用于任何使用24V DC系統進行控制的應用,例如電機控制、機器人

2019-07-23 06:48:24

本應用筆記介紹了八通道數字輸出驅動器MAX14912 / MAX14913的關鍵特性,以及如何在工業和樓宇自動化應用中使用它們。數字輸出驅動器廣泛用于工業應用中的過程控制(PLC系統)和樓宇自動化

2020-09-24 10:24:25

什么是運動控制?運動控制系統是由哪些部分構成的?驅動器的工作模式有哪幾種?

2021-10-11 07:56:21

比較器ADCMP606是CML差分電平輸出,這里我只想用到CML的正極作為輸出,負極接地,請問這樣做是否可行?

2023-11-23 08:05:04

(1)ADC、DAC選型時候的有個data input format 是lvds和cmos什么意思啊?1. lvds是不是那個DCO+和DCO-?。這兩個信號是不是必須要從時鐘專用引腳輸入

2017-01-23 15:17:38

使用輸出失調電壓為1.25V(典型值)的LVDS時鐘驅動器。沒有交流耦合電路文件不清楚....請澄清謝謝卡爾

2020-07-17 13:45:49

可以處理2對CML(輸入/輸出)。但是,GTX可以生成和接收LVDS信號嗎?或者必須使用I / O bank來處理LVDS信號?謝謝你的回答。問候,亞歷克斯

2020-06-13 08:38:27

8通道恒定電流吸入型LED驅動器主要特點?八個恒定電流輸出通道,可吸收5mA至120mA電流?恒定輸出電流,不隨負載電壓而改變?負載開路、負載短路及溫度過熱檢測?256級可編程總體電流增益?可并聯

2014-01-24 13:44:07

完成由P 型設備完成的任務。對LVPECL 而言,很少有人研究過完成輸出級設計所需要的發射極電流控制與傳輸線終端之間的關系。剖析LVPECL 閘道的基本原理和分析任何特定LVPECL 驅動器的典型終端,有助于工程師量身定制穩健和高能效的LVPECL 終端。

2019-07-08 07:05:43

過程中產生比特錯誤。在下圖 3 中,我舉了兩個實例,用以說明如何在 CML 驅動器、LVPECL 驅動器和 LVDS 接收器之間實施 AC 耦合。圖3:不同接口的互連連接任意兩個不同接口時可使用這種相同

2018-09-13 14:28:38

伺服控制原理主要是什么?伺服電機驅動器有哪幾種控制模式?

2021-06-28 09:29:56

驅動器上電沒有電壓輸出,

2018-11-02 12:48:52

電機內部的編碼器把數據反饋給運動控制卡來進行閉環。就是通過同一個編碼器把信息反饋給不同的對象。一個是伺服驅動器內部廠家設計好的,另一個就是自己的上位裝置。本人用的是安川7系列的驅動器和電機,驅動器上面的CN1上的A,B,C相信號線到底輸出的是什么?編碼器數據不是已經反饋給了伺服驅動器了嗎?難道這兩個是并聯的?

2017-12-19 21:48:30

L298N與L298P是什么?VNH5019又是什么?代替TB6612FNGIC的驅動器有哪幾種呢?

2021-12-21 07:53:09

嗨,每個人,我都使用V4 FPGA從CMOS接收LVDS數據。同時,CMOS輸出一個LVDS時鐘資源'dck'作為同步時鐘。數據在上升沿和下降沿傳輸,如下圖所示。 我清楚地知道在verilog

2020-04-20 10:21:22

具有升壓轉換器的RE46C317壓電喇叭驅動器的典型應用。 RE46C317 / 18是CMOS壓電喇叭驅動器IC,內置升壓轉換器

2020-04-24 09:22:57

你好!我正在使用斯巴達6 lx100與斯巴達6 lx9進行通信,它位于不同的主板上。它們之間的連接是點對點的,通過30厘米電纜和100Mhz LVDS信號。我應該使用外部驅動器和接收器還是fpgas

2019-06-24 15:44:23

linux系統中網卡驅動的典型工作方式有哪幾種?uboot中網卡驅動的工作方式有哪幾種?

2021-12-24 07:52:25

工作記錄流水賬1.機器人電機驅動器安裝接線。2.CML2.00開發包繼續研究:電機驅動器底層API。3.基于電機驅動CML-2.00程序編寫(控制臺)實現功能:多驅動器串聯同時控制速度角度控制連續運行4.MFC界面實現功能:多驅動器串聯同時控制速度角度控制連續運行第一版:運動控制系統...

2021-09-13 06:27:55

8.04Vpp的最大輸出擺幅。這使得CMOS驅動器能夠直接連接并驅動LDMOS和GaN等功率晶體管。該驅動器的最大導通電阻為4.6Ω。2.4GHz時所測量的占空比控制范圍為30.7%到71.5%。采用通過

2019-07-31 06:07:48

本文我們將回過頭來了解如何在 LVPECL、VML、CML、LVDS 和子 LVDS 接口之間轉換。系統當前包含 CML 與 LVDS 等各種接口標準。理解如何正確耦合和端接串行數據通道或時鐘通道

2022-11-21 07:59:56

你好我需要將LVDS輸出驅動器連接到ZYNQ 7030的HP Bank。LVDS輸出驅動器的電源電壓為VCCO_LVDSout_DRIVER = 2.5V,HP bank為VCCO_HP_BANK

2020-08-12 09:34:33

本篇主要介紹常用的差分邏輯電平,包括LVDS、xECL、CML、HCSL/LPHCSL、TMDS等。

2021-07-17 19:37:39

NB7L32MMNGEVB,2.5V / 3.3V,12-GHz,用CML輸出評估板除以2。該評估板旨在便于快速評估NB7L32M GigaComm時鐘驅動器。 NB7L32M設計用于支持高工作頻率

2019-02-20 09:29:07

怎樣去設計壓電驅動器輸出電壓監測顯示系統?如何高效的利用20路電壓測量模塊采集到壓電陶瓷驅動器的輸出電壓?

2021-04-08 06:30:52

負載驅動器?電磁閥驅動器?燈和LED顯示屏?邏輯電平變換器?一般低壓側開關應用說明DRV777電機驅動器具有7個低輸出阻抗驅動器,最大限度地減少片內功耗。DRV777支持1.8V到5V的CMOS邏輯輸入接口

2020-09-11 17:31:35

ADI最新推出兩款模擬輸出驅動器AD5750和AD5751,能顯著提高過程控制應用的效率和可靠性,包括那些在高恒流電壓和高溫條件下工作的過程控制應用。這兩款器件基于ADI公司的iCMOS工藝技術

2019-07-01 07:08:17

比較器ADCMP606是CML差分電平輸出,這里我只想用到CML的正極作為輸出,負極接地,請問這樣做是否可行?

2018-10-19 09:26:54

/CMOS 輸入信號,轉換成低壓(350mV)的差分輸出信號。芯片驅動器還支持三態輸出功能,可以用來關斷輸出驅動級,通過關斷輸出電流可以得到11mW的靜態功耗。芯片還具有掉電關斷功能,當VCC開路

2021-11-17 11:10:28

電機驅動器輸出電流不夠,可能由哪些原因造成,求助大家來指點一下。驅動器檔位調節至2A,但實際電機運動時,電流只有0.3A左右。求助大家來討論指點一下,謝謝啦。

2017-09-01 17:38:56

電機驅動器主要可以分為兩種,數字式的驅動器和非數字式的驅動器: 數字式的基本上依靠總線通訊,通過讀寫驅動器上的控制器的寄存器或者RAM來實現數據交換。在上層就只需要發送簡單的控制參數就可以了(例如

2021-09-07 08:40:47

,輸出電壓低于VSS+0.5V(VSS為數字地)為邏輯 0。CMOS電路輸出高電平約為 0.9Vcc,而輸出低電平約為 0.1Vcc.當輸入電壓高于VDD-1.5V時為邏輯 1,輸入電壓

2019-03-22 07:00:00

請問ADF4350輸出能直接驅動LVDS嗎,或者和別的電平能匹配嗎,能不能用DC耦合驅動CML或者LVPECL 或者LVDS的電平?

2018-12-12 09:10:29

LVDS輸出等各項特色的組合是其它SXGA CMOS圖像傳感器產品所無法媲美的。賽普拉斯一直致力于滿足對于具有更高幀頻和更多集成特色的創新高速圖像采集解決方案的市場要求,以廣泛用于各類應用,包括運動分析

2018-10-24 11:39:57

運動控制卡是什么?運動控制卡有何功能?伺服驅動器是什么?伺服驅動器有哪幾種控制方式?

2021-10-09 08:17:42

的穩定性,令數據傳輸出現誤碼。克服這些問題的其中一個辦法是采用低電壓差分信號 (LVDS) 數據總線。圖 1 是其中一種模擬/數字轉換器的結構框圖,帶有LVDS 輸出信號,驅動專用集成電路或解串器。圖 1:結構框圖

2019-07-12 06:42:45

DC1954A-D,LTC6954-4演示板低相位噪聲,三路輸出時鐘分配器/驅動器,3路LVDS / CMOS輸出(DC590或DC2026)。演示電路1954A采用LTC6954-4,一種低相位噪聲,三輸出時鐘分配器/驅動器。 DC1954A有四種選擇,每種版本的LTC6954都有一種

2019-02-21 07:36:59

討論柵極驅動器是什么,為何需要柵極驅動器?考慮一個具有微控制器的數字邏輯系統,其I/O引腳之一上可以輸出一個0 V至5 V的PWM信號。這種PWM將不足以使電源系統中使用的功率器件完全導通,因為其過驅電壓一般超過標準CMOS/TTL邏輯電壓。如此,請大神分析下面兩種方式:

2018-08-29 15:33:40

8.04Vpp的最大輸出擺幅。這使得CMOS驅動器能夠直接連接并驅動LDMOS和GaN等功率晶體管。該驅動器的最大導通電阻為4.6Ω。2.4GHz時所測量的占空比控制范圍為30.7%到71.5%.通過使用新型薄

2019-07-12 07:43:04

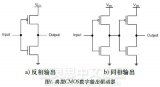

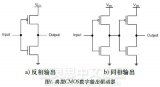

的數字輸出。典型的CMOS驅動器由兩個晶體管(一個NMOS和一個PMOS)組成,連接在電源(VDD)和地之間,如圖1a所示。這種結構會導致輸出反轉,因此,可以采用圖1b所示的背對背結構作為替代方法,避免

2021-12-08 07:00:00

的數字輸出。典型的CMOS驅動器由兩個晶體管(一個NMOS和一個PMOS)組成,連接在電源(VDD)和地之間,如圖1a所示。這種結構會導致輸出反轉,因此,可以采用圖1b所示的背對背結構作為替代方法,避免

2020-12-01 06:00:00

,CMOS 是很常見的數字輸出。典型的 CMOS 驅動器由兩個晶體管(一個 NMOS 和一個 PMOS)組成,連接在電源(VDD)和地之間,如圖 1a 所示。這種結構會導致輸出反轉,因此,可以采用圖 1b

2020-11-17 08:30:00

LED恒流驅動器的幾種類型:

2009-07-04 16:27:51 178

178 MADR-010410模塊驅動MADR-010410 是一款專用于多功能模塊的 CMOS 驅動器,例如基于 GaAs 的發射/接收模塊。驅動器將 CMOS/LVCMOS 輸入控制轉換為 GaAs

2023-03-31 12:51:25

MADR-010269-DIE用于數字衰減器和移相器的 CMOS 串行/并行十六進制驅動器MADR-010269-DIE 是一款 CMOS 驅動器,旨在與 MACOM 的數字衰減器和移相器配合

2023-03-31 13:49:25

LVDS、PECL和CML介紹隨著高速數據傳輸業務需求的增加,如何高質量地解決高速IC芯片間的互連變得越來越重要。低功耗及優異的噪聲性能是有待解決的主要問題。芯

2010-04-10 10:02:54 34

34 提出了一種用于多點數據傳輸的BLVDS(Bus low voltage differential signal)驅動器電路設計。設計中將電壓模式驅動器電路和雙電流源模式驅動器電路相結合實現多點數據傳輸,既充分利用了LVDS

2010-07-29 15:45:25 0

0 lvds是什么意思?

摘要:與ECL、PECL和CML標準相比,ANSI EIA/TAI-644的低電壓差分信號(LVDS)標準具有低功耗、低噪聲輻射等優勢。本文主要討論LVDS的特性及

2009-05-01 11:13:29 10087

10087

ADN4667: 3 V LVDS四通道CMOS差分線驅動器

ADN4667是一款四通道CMOS低壓差分信號(LVDS)線驅動器,提供400 Mbps以上的數據速率(200MHz)和超低功耗。它具有流通引腳,可

2009-09-28 08:17:18 1508

1508 外圍驅動器,什么是外圍驅動器

接口電路的外圍驅動器我們可以簡單分為下列幾種:

1. 與門 2. 或門 3. 或非

2010-03-24 14:35:59 1826

1826 本文描述TI 的客戶在不用 LVDS (低壓差分信號傳輸)驅動器時,如何采用LVDS 接收器于其他驅動器配合解決一些簡單的問題。

2011-07-18 15:21:36 30

30 CAT4134專用 LED驅動器 典型電路:

2012-05-07 11:11:45 3478

3478

MAX6957 LED顯示驅動器及輸入/輸出擴展器典型應用電路

2012-05-17 11:19:39 1746

1746

數字輸出驅動器廣泛用于工業應用中的過程控制(PLC系統)和樓宇自動化,也可用于任何使用24VDC系統進行控制的應用,例如電機控制、機器人和機械自動化。

2017-09-19 11:44:49 19

19 低功耗數據傳輸領域的主流技術。它具有信號擺幅小、速度快、功耗低、抗共模噪聲能力強、電磁干擾小等優點。 LVDS接口技術的原理可簡單概括為:由驅動器( driver)將CMOS或TTL信號轉換成LVDS差分信號,并經過互連線傳輸到接收器端,而接收器又將差分信

2017-11-01 15:50:08 11

11 高速轉換器三種最常用的數字輸出是互補金屬氧化物半導體(CMOS)、低壓差分信號(LVDS)和電流模式邏輯(CML)。ADC中每種數字輸出類型都各有優劣,設計人員應根據特定應用仔細考慮。這些因素取決于ADC的采樣速率和分辨率、輸出數據速率、系統設計的電源要求,以及其他因素。本文將討論每種輸出類型的電

2017-11-17 20:08:48 15266

15266

典型的差分驅動電路設計與原理分析

2018-04-08 14:06:12 79

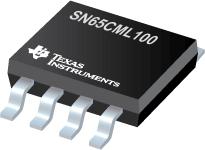

79 電子發燒友網為你提供TI(ti)SN65CML100相關產品參數、數據手冊,更有SN65CML100的引腳圖、接線圖、封裝手冊、中文資料、英文資料,SN65CML100真值表,SN65CML100管腳等資料,希望可以幫助到廣大的電子工程師們。

2018-10-16 10:08:54

LVDS接收器可以承受至少±1V的驅動器與接收器之間的地的電壓變化。由于LVDS驅動器典型的偏置電壓為+1.2V,地的電壓變化、驅動器偏置電壓以及輕度耦合到的噪聲之和,在接收器的輸入端相對于接收器的地是共模電壓。

2018-11-01 16:47:28 73997

73997

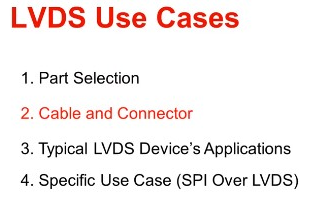

LVDS典型用例

2019-05-13 06:17:00 5760

5760

本篇主要介紹LVDS、CML、LVPECL三種最常用的差分邏輯電平之間的互連。由于篇幅比較長,分為兩部分:第一部分是同種邏輯電平之間的互連,第二部分是不同種邏輯電平之間的互連。

2021-01-07 16:30:00 36

36 ADCLK846:1.8 V、6 LVDS/12 CMOS輸出低功耗時鐘扇出緩沖器

2021-03-20 11:31:10 9

9 電子發燒友網為你提供詳解信號邏輯電平標準:CMOS、TTL、LVCMOS、LVTTL、ECL、PECL、LVPECL、LVDS、CML資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-09 08:45:44 90

90 AD9665:4通道、LVDS、雙輸出、帶振蕩器的激光二極管驅動器數據表

2021-04-16 12:42:10 2

2 幾種典型神經網絡結構的比較與分析說明。

2021-04-28 10:11:58 3

3 AD9522-5:12 LVDS/24 CMOS輸出時鐘發生器數據表

2021-04-28 10:53:01 0

0 ADN4663:雙路3 V CMOS LVDS高速差分驅動器數據表

2021-05-08 14:25:27 2

2 ADN4670:可編程低壓1:10 LVDS時鐘驅動器

2021-05-09 15:28:56 9

9 ADN4667:3 V LVDS快速CMOS差線驅動數據Sheet

2021-05-25 09:47:02 12

12 ADN4661:單路、3 V、CMOS、LVDS、高速差分驅動器數據表

2021-05-25 14:12:55 1

1 ADN4665:3V,LVDS,Quad,CMOS差分線驅動數據Sheet

2021-05-25 14:18:22 2

2 GM8827C實現以7:1的壓縮比將27位CMOS/TTL信號(RGB 8位和HSYNC、VSYNC、 DE)換成串行 LVDS 輸出數據流。輸入時鐘經內部鎖相后,同頻率輸出,同時轉換為 LVDS

2021-11-30 21:06:05 8

8 獲得連接:LVPECL、VML、CML、LVDS 與子 LVDS 之間的接口連接

2022-11-04 09:52:13 3

3 許多微處理器提供的數字脈寬調制 (PWM) 輸出基于內部 8 位或 16 位計數器,并具有可編程占空比。它適用于調節LCD驅動器,負電壓LED驅動器或電流控制LED驅動器的輸出。

2023-01-13 16:03:05 1655

1655

輸入級可單端或差分驅動,可采用多種信號格式(CML、LVDS、LVPECL或CMOS),以及交流或直流耦合。輸入級同樣具有可調輸入阻抗。該器件集成帶有可調擺幅/功率電平的8路LVPECL輸出和1路CML輸出,步進為3 dB。

2023-02-01 15:23:19 295

295 在有源晶振,也就是石英振蕩器技術手冊中,CMOS模式是較為常見的一種輸出,屬于電壓控制形式,用來驅動邏輯電平輸入。CMOS是TTL輸出模式的改進方案,相比以往的TTL,CMOS輸出模式具有傳輸

2022-07-07 14:29:12 1023

1023

差分驅動器可以由單端或差分信號驅動。本教程利用無端接或端接信號源分析這兩種情況。 情形1:差分輸入、無端接信號源 圖1顯示一個差分驅動器由一個平衡的無端接信號源驅動。這種情況通常是針對低阻抗信號源,信號源與驅動器之間的連接距離非常短。 圖1:差分輸入、無端接信號源 詳文請閱:差分驅動器分析

2023-11-28 15:19:25 0

0 電壓。 準備工具和設備: 為了測量伺服驅動器的輸出電壓,我們需要準備以下工具和設備: 數字電壓表:用于測量電壓的精確值。 電壓表探頭:用于將電壓表連接到伺服驅動器的電壓輸出端口。 電纜:將電壓表探頭連接到伺服驅動

2024-01-15 11:22:06 590

590

電子發燒友App

電子發燒友App

評論