模擬工程師以前在設計需要具有多路輸出、動態負載共享、熱插拔或廣泛故障處理能力的電源時,往往需要與復雜性抗爭。利用模擬電路來實現系統控制功能并非總是經濟有效或靈活的。采用模擬技術設計電源需要使用“過大的”元件來解決元件變化和元件漂移的問題。即使是在克服了這些設計難點之后,這些電源在生產線末端還需要進行人工調整。

那么,模擬工程師應該選擇什么來設計電源呢?工程學對這個問題的回答是利用功率轉換反饋環路的智能數字控制來實現上述功能。單片機已使模擬設計人員能夠實現監控、控制、通信甚至確定性功能(如電源中的上電時序、軟啟動和拓撲結構控制等)。不過,由于缺乏經濟有效的高性能技術,以數字方式控制整個功率轉換環路還不太現實。

模擬工程師設計數字電源轉換

1 開關電源中的DSC設計

現在,一種新型數字信號控制器(DSC)的問世使具有智能電源外設等功能的數字轉換成為可能,因為這種器件采用基于計數器的脈沖寬度調制(PWM)模塊、基于模擬比較器的反饋和協調模數轉換器(ADC)采樣,可以在一個單時鐘周期內進行快速乘法。這些特性的組合有助于DSC處理控制環路軟件所需的較高執行速度。

在開始進行電源設計之前,需要做出以下決擇。

a 選擇一種適合應用需要的拓撲結構:升壓型還是降壓型(Boost還是Buck),隔離式(正向、半橋還是全橋)。

b? 選擇一種開關技術: 硬開關還是軟開關。軟開關技術(如諧振模式或準諧振模式),以增加電路和控制的復雜程度為代價,換取較少的開關損耗。

c? 選擇一種控制方法:電壓模式還是電流模式。

電壓模式控制和電流模式控制是基于傳統模擬開關電源(SMPS)控制技術的兩種控制方法。在電壓模式條件下,利用期望的輸出電壓和實際的輸出電壓之間的差值(誤差)來控制電源電壓施加在電感器上的時間,進而間接地控制電感器中的電流。在電流模式控制條件下,利用期望的輸出電壓和實際的輸出電壓之間的差值(誤差)為模擬比較器創建一個門限值來設置峰值電感電流,從而控制平均電感電流。電壓模式可以在噪聲環境中或寬工作范圍條件下提供更高的穩定性;電流模式控制可以實現逐周期的電流限制和更快的瞬態響應,它還可防止可能導致電感器飽和并引起災難性MOSFET故障的“逐步增加的電感電流”。

d? 選擇PWM工作頻率。高頻PWM有助于使用更小的電感器和電容器,但是需要額外付出開關損耗為代價。

e? 確定需要的控制帶寬。這在很大程度上取決于應用所期待的負載瞬態響應。

f? 根據估計的控制帶寬需求來分配處理器資源。雖然有多種控制算法,但是常用的技術仍是比例、積分和微分(PID)方法。使用常用PID算法,控制環路將需要以所需控制系統帶寬的八倍速度運行,以保證足夠的相位容限。在估計控制環路的延遲時,控制環路內的所有延遲都必須考慮到(參見“計算控制環路的延遲”部分)。

接著,選擇一個可以滿足您所有或大多數設計需求的DSC。

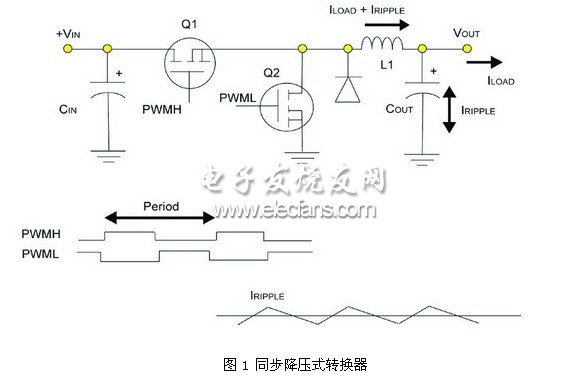

選擇采用Microchip的SMPS dsPIC DSC--dsPIC30F2020來設計一個同步降壓式轉換器。這種DSC有一個硬開關,可提供互補PWM模式的電壓控制模式。這種降壓式轉換器(見圖1)采用同步開關,用一個MOSFET取代了電路中的整流器,因為它比標準整流器有低得多的正向電壓降。通過降低電壓降,這種降壓式轉換器的整個效率可以提高5%~10%。同步開關與Q2需要一個次級PWM信號來補充初級PWM信號。當Q1關斷時,Q2接通,反之亦然。此外,在PWM信號的上升沿和下降沿期間,需要利用“死區”控制來防止Q1和Q2同時導通。

?

降壓式轉換器的輸入與輸出電壓的關系可以表示為:

VOUT = VIN ( D,其中 D = PWM占空比 = TON /(TON + TOFF)

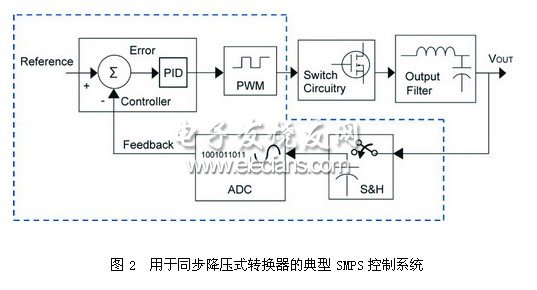

一個降壓式轉換器理想的輸出電壓是輸入電壓與晶體管占空比的乘積。通過檢測(見圖1),如果晶體管Q1是常通的,輸出電壓將等于輸入電壓。如果Q1是常斷的,那么輸出電壓將為零。實際上,當負載電流增加時,晶體管和電感器兩端存在的電壓降將會增加。圖2給出了如何使用DSC設計數字SMPS控制系統。

?

采樣保持(S/H)電路通常每2~10ms進行一次采樣,ADC需要大約500ns將模擬反饋信號轉換成為數字值。PID控制器是一種運行于DSC的程序,有大約1~2ms的計算延遲。該控制器輸出可以轉換為一個PWM信號,由它來驅動開關電路。當進入新的占空比時,如果PWM發生器不能立即更新其輸出,就可能出現明顯的延遲。晶體管驅動器和相關的晶體管也會引入大約50ns到1微秒的延遲,其長短因使用的器件和電路設計而異。

2 計算控制環路的延遲

總控制環路延遲是ADC采樣與轉換時間(500ns)、PID計算時間(1μs)、PWM輸出延遲(0)、晶體管切換時間(50ns)和PID執行速度時期(2μs)之和。這個例子中的總環路延遲是3.65μs,這意味著最大有效控制環路的采樣率為274 kHz。雖然尼奎斯特定理需要2倍的采樣率來重建一個信號,數字控制環路仍必須以6倍至10倍采樣率進行采樣。這樣做的原因是只使用2倍的采樣率,相位滯后將180度。利用2倍采樣率,我們已經用完了180度的相位滯后“預算”,而沒有考慮系統中任何其他的延遲。一個采用8倍采樣率的系統單在采樣過程引入45度的相位滯后,這是一個好得多的采樣率。為了有足夠的相位容限,許多數字控制系統對模擬信號進行了10倍或更高的過采樣。假定最高有效采樣率為274 kHz,有效控制帶寬是其八分之一,也就是大約34 kHz。

3 SMPS設計中PWM的重要性

不同的電源規范推動著對不同電源拓撲結構的需求,這些不同的拓撲結構需要不同的PWM模式,其中每一種都支持多種SMPS設計,包括標準、互補、推挽、多相位、可變相位、電流復位和電流限制PWM模式。最基本的PWM模式是標準的邊沿對齊式PWM,其中的導通與關斷時間之比控制著電源電流。每對輸出中只有一個PWM輸出被用于這些異步降壓式、升壓式和反激式轉換器電路。同步降壓式轉換器采用互補PWM模式,其中的互補輸出控制一個由MOSFET實現的 “同步開關”整流器,而不是通常的整流器。互補PWM模式還可以用于采用同步整流來改善系統效率的其他電路。

推挽式轉換器通常用于DC/DC轉換器和AC/DC電源。“多相PWM”術語描述的是多PWM輸出而不是邊沿對齊的。多相轉換器電路經常用于必須提供大電流、負載變化可能非常迅速的應用的DC/DC轉換器。由于PC電源的廣泛使用,相位變換PWM模式正變得越來越常見。Microchip的dsPIC DSC SMPS系列可以支持當前廣泛用于電源行業的所有已知的PWM模式。

4 理解PWM分辨率

電源設計人員和客戶必須正確地理解“PWM分辨率”這個術語。PWM分辨率并不表示某個計數器有多寬,而是表示在PWM循環時期內可以發生多少次計數(盡可能最小的PWM時間片)。在電源行業,PWM分辨率表示的是PWM占空比內的最小時間增量。這個分辨率經常以ns表示。如果一個PWM模塊沒有足夠的分辨率,控制系統(硬件或軟件)就會使PWM輸出發生抖動,以實現期望的平均值輸出。在電源應用中,PWM抖動可以引起紋波電流的問題,并使控制進入所謂“極限循環期(Limit Cycling)”的不良運行模式。

例如,假設控制環路的輸出需要3.25的值,而PWM可以輸出的值是3和4。在這種情況下,PWM在33343334值之間抖動。這可以容易地看到--許多DSC都采用運行于40至150 MHz范圍之間的PWM計數器,可以產生6至25ns的PWM分辨率。SMPS dsPIC DSC系列具有1ns的占空比分辨率。在一個控制環路中,在PWM輸出一個新的占空比值之前,來自電壓和電流測量的采集時間被稱為“延遲”。當延遲下降時,控制環路變得更穩定和更具有響應能力。一些DSC配備了PWM模塊,只在PWM周期到周期的基礎上接收新的占空比數據。在PWM模塊接收數據之前,軟件計算新的占空比值的時間滯后會增加控制環路延遲,并使其穩定性下降。因此,最好采用有PWM模塊的DSC,以便及時接收和處理新的占空比數據。

5 SMPS ADC的需求

您可以將您的模擬知識運用于采用DSC的智能電源設計。片上ADC可以為控制環路提供系統狀態(反饋)。傳統的ADC是基于ADC值以“組”的方式進行采集和處理的假設而設計的。音頻處理和工業控制系統的ADC通常都是以這種方式發揮作用。組采樣可使處理器工作量達到組中的峰值,這將增加控制環路的延遲。

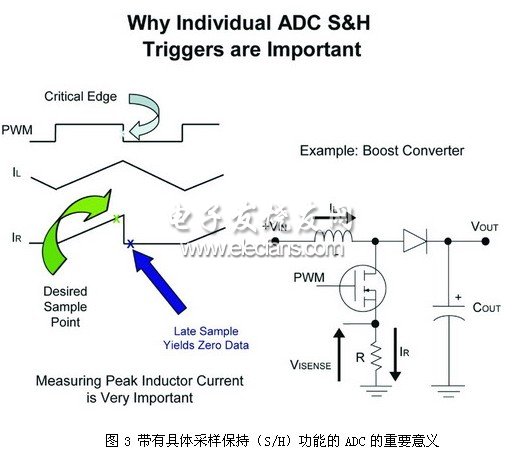

在SMPS電路中,通常不存在要被采樣和轉換的模擬信號,或者這樣的信號不會在任何時候都那么明顯。這樣的信號可能在PWM周期的某一刻才比較明顯。因此,由于不精確的采樣定時,標準的ADC模塊可能錯過希望得到的數據。

圖3給出了一個用于監測電流的電流檢測電阻器的實例電路。在這個電路中,只有當晶體管導通時,才能檢測到電流。典型的ADC模塊不能精確地使采樣保持電路在適當的時間進行一次采樣。如果應用需要多個電路進行檢測,那么這個ADC就不理想。SMPS dsPIC DSC的片上ADC模塊可提供獨立的采樣保持電路,可以進行彼此獨立的采樣。因此,它可以在準確的時刻監控電壓或電流,有助于實現事件瞬時(event transitory)信號的采樣,并降低系統成本。此外,SMPS dsPIC器件的片上ADC可以進行異步采樣,有助于支持PFC(70 kHz)和DC/DC(250 kHz)等不同頻率的多控制環路運行。

?

6 模擬比較器改進數字SMPS設計

因為ADC不能繼續不斷地監控信號,所以只能以高達每秒兆次采樣(MSPS)的量級進行采樣。一些DSC具有模擬比較器,可以解放處理器和ADC以完成其他重要的任務。例如,模擬比較器可以利用與傳統線性電源控制器直接控制PWM占空比類似的方式進行電流控制。模擬比較器還能夠提供對過壓或過流狀況的獨立監測。Microchip的SMPS dsPIC DSC的參考DAC和模擬比較器可以實現從電流測量到PWM更新的大約25ns的延遲。通常,從檢測到模擬電壓,直到由比較器對PWM輸出進行修改,大約需要25ns的時間。與其他必須使用“輪詢”技術的ADC以及利用處理器修改PWM輸出來響應變化條件的其他DSC相比,這個響應時間是非常迅速的。事實上,這正是DSC實現逐周期電流限制的方法,屬于電流模式控制。由于連接模擬比較器的參考DAC也是16位的,PWM分辨率也是相同的,因此同樣的控制分辨率對電壓和電流模式都是有效的。

7 PID算法

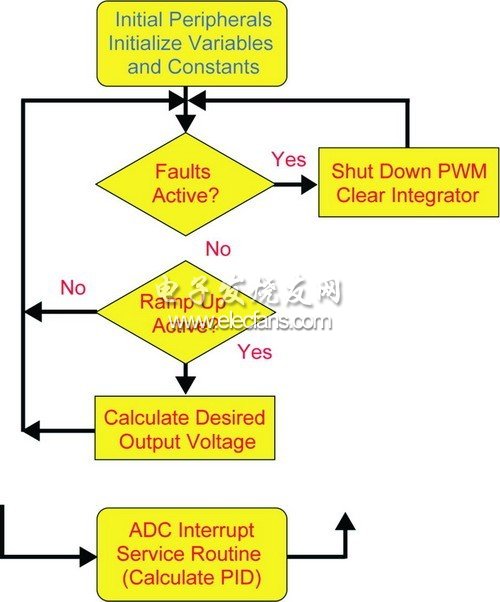

使用PID算法,將實際與期望輸出電壓之間的誤差進行比例、積分和微分計算,然后將這三項合起來,實現對PWM占空比的控制。PID算法可以用于采用電壓和電流模式的控制環路。處理Microchip的DSC不需要DSP技巧(見圖5的代碼列表),控制軟件(圖4)的主要“核心”是PID環路。PID軟件通常很小,但是其執行速度非常快,通常每秒可以反復幾十萬次。這么高的反復率需要PID軟件程序盡可能有效地發揮最佳性能。使用匯編程序是保證“嚴緊代碼”的一種很好的方法。

PID控制環路是定期由ADC進行中斷驅動,任何系統功能都能在“空閑環路”中執行,以便減少PID控制軟件內不必要的工作量。諸如電壓上升/下降、錯誤檢測、前饋計算和通信支持程序功能都是空閑環路可以執行的,其他中斷驅動進程的優先級都必須比PID環路低。

空閑環路在完成系統和外設的初始化任務之后啟動。通常,空閑環路監控溫度,計算“前饋”條件,并檢查故障狀況。SMPS軟件可執行該控制算法,將ADC中斷驅動的PID環路作為其與時間關系最密切的部分。PID軟件不應該使用超過可用處理器大約66%的帶寬,以便計算資源的其余部分能夠分配給空閑環路軟件。

假設以30 MIPS運行PID環路(包括30條指令),執行時間大約為1μs。如果反復率是500 kHz(2μs),那么PID工作量需要消耗一半可用的處理器帶寬,也就是15 MIPS。

用于數字式降壓式轉換器的PID軟件的實例代碼列表:

CALCULATE_PID:

push.s????? ; Save SR and W0-W3

bclr.b? IFS0+1, #3?? ; Clr IRQ flag in interrupt controller

#PID_REG_BASE, w8? ; Init pointer to PID register block

mov??? #PID_GAIN_REG_BASE, w10? ; Init pointer to PID gain register block

mov??? ADBUF1, w0??? ; Read ADC to get voltage measurement

mov??? COMMANDED_VOLTAGE, w1?? ; Get commanded output voltage

sub???? w1, w0, w0?? ; W0 = proportional voltage error

mov??? PROPORTIONAL_Error, w1? ; Get previous voltage error

sub???? w0, w1, w2?? ; diff error = new verr - old verr

mov??? w0, PROPORTIONAL_ERROR? ; Store New Proportional Voltage Error

mov??? w0, PREINTEGRAL_TERM? ; Store copy PERR? as pre integral term

mov??? w2, DERIVATIVE_ERROR? ; Store new Derivative Error

;?? These registers are reserved for PID calculations

;??? w6, w7?? = contains data for MAC operations

;??? w8, w10 = pointers to error terms, and gain coefficients

SUM_PID_TERMS:

clr????? A, [w8]+=2, w6, [w10]+=2, w7? ; clr A, prefetch w6, w7

mac??? w6*w7, A, [w8]+=2, w6, [w10]+=2, w7 ; MAC proportional term and gain

mac??? w6*w7, A, [w8]+=2, w6, [w10]+=2, w7 ; MAC derivative term and gain

mac??? w6*w7, B, [w8]+=2, w6, [w10]+=2, w7 ; Update Integrator

add??? ACCA??? ; Add ACCB (Integrator)? to ACCA

sftac?? A, -#8??? ; scale accumulator (shift)

mov??? ACCAH,w0?? ; Read MSW of acca (result)

btst?? ACCAU,#7?? ; Check sign bit of ACCA

bra??? z, Output_PWM? ; Branch if acca PWM value is positive

clr???? w0??? ; Clear negative PWM values

OUTPUT_PWM:

mov??? w0,? DC1?? ; Output new duty cycle value

pop.s???? ; Restore SR, w0-w3

retfie???? ; Return from Interrupt

評估板有助于設計人員測試和修改SMPS控制軟件,并理解SMPS的設計原理。在這種情況下,您可以考慮使用Microchip的dsPICDEM SMPS降壓型開發板--卓越的低功耗DC/DC降壓式轉換器來評估DSC器件和控制軟件。該板可通過標準AC/DC 9V,0.75A電源獲得其輸入電源。板上有兩個獨立的降壓式轉換器,演示軟件設置可提供高達+5V和+3.3V的輸出。

?

圖4 控制軟件的結構

這個開發板的輸入電壓范圍為8-14V DC。每個輸出負載應該限制在0.75A,而輸入電源可以通過同軸輸入電源連接器J2或測試夾連接P1和P2提供。該板也可為+5V輸出提供一個動態負載。這個負載是通過1 kHz方波信號驅動的,該信號是由輸出比較模塊產生的。板上動態負載使用一個FET將電阻器負載連接到轉換器對地輸出,實現轉換器激勵,以便可以測量轉換器的動態行為。動態負載的使用可通過跳線模塊和/或軟件由用戶自行選擇。

用戶可以選擇通過跳線設置,像標準降壓式轉換器或同步降壓式轉換器那樣運行開發板。所提供的軟件能夠以電壓控制模式運行該板,也可以進行電流監控。該板也可通過轉換器輸出端的一個檢測電阻器測量電流,而電壓則被放大并送到dsPIC30F2020器件的ADC輸入端。該板還可提供通過ADC輸入可讀取的三個備用可變電阻器。這些“電位器”可用于在原型設計中的模擬所需的信號。

8 結語

通過專用于數字回路控制的新款DSC,電源設計人員可以容易地在他們的設計中加入新的功能和能力。要做到這一點,無需學習復雜的數字信號處理器(DSP)處理技巧,使用熟悉的模擬元件和軟件,設計人員就能夠迅速而經濟地使用DSC開發具有更高智能的電源。

電子發燒友App

電子發燒友App

評論