讀卡頭靈敏度 - 極具成本效益的磁卡讀卡器設計

讀卡頭靈敏度:讀卡頭靈敏度取決于線圈匝數以及讀卡頭與磁條之間的間距。

由于所有這些參數的影響,信號幅度可能在幾百個uV至幾十個mV之間變化。這個范圍可以用放大器進行補償。但不能用固定增益放大器。當劃卡速度很高,卡的質量又很好時,放大器輸出可以飽和到電源軌電壓。而當信號飽和時,用兩個連續峰值之間的時間差代表的信息將丟失。因此如實地放大傳感器信號、不至于使波形發生飽和或改變很重要。這就要求使用增益可配置的放大器,以便我們隨時調整增益。要做到這一點,系統必須能夠檢測信號變弱的時刻。這可以用跟蹤傳感器信號的ADC尋找近似的信號峰值來實現。

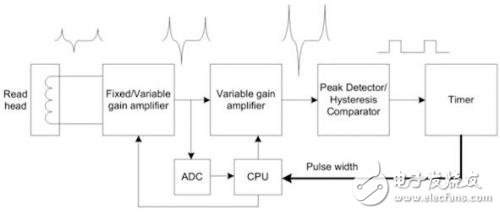

圖6顯示了一個完整的系統。最好將放大電路做成兩級,用ADC接收第一級電路的輸出。這樣就無需高分辨率ADC,8位ADC就足以滿足這種應用需求。第一級可以是固定增益的放大器,也可以是可變增益放大器。第二級是可變增益放大器。CPU讀取ADC結果,并通過調整增益使第二級放大器的信號輸出達到最佳。第二級放大器的輸出送到峰值檢測器/磁滯比較器電路進行峰值檢測。來自檢測器的脈沖輸出被饋送至定時器進行時間差測量,然后由CPU解碼出1和0.

圖6:磁卡讀卡器框圖

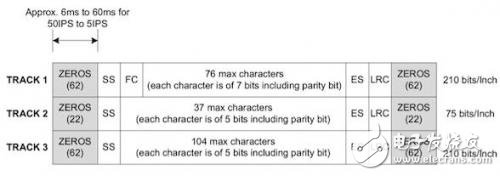

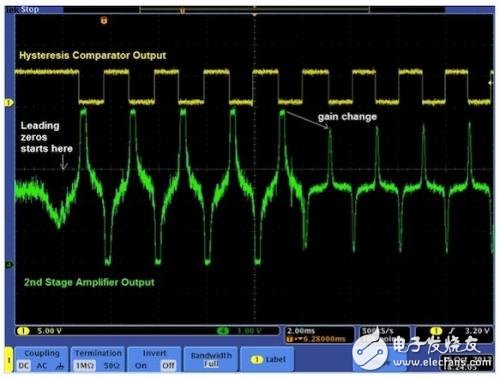

至此仍然存在增益更新之前是否有數據丟失的問題。為了避免這個問題,磁卡的兩頭會用前導零進行編碼以實現同步(這樣可以支持雙向劃卡)。這樣做的目的是使解碼器同步于劃卡速度。舉例來說,在磁道1中,共有約62個前導零。磁道1具有210個比特的數據密度。因此我們可以估算出劃卡速度為5 IPS時前導零將持續約60ms時間,劃卡速度為50 IPS時前導零將持續6ms.對另外兩個磁道來說或多或少是相同的,如圖7所示。在人為劃卡時一開始就是50 IPS的劃卡速度是不可能,因此系統具有比6ms長得多的時間來測量峰值并調整增益。圖8顯示了增益控制過程。

圖7:磁卡中三個磁道的內容

需要注意的是,CPU在劃卡期間可能會持續精細調整增益以適應變化的幅度。正常情況下,順著劃卡的方向,劃卡速度會增加,從而增加信號幅度。注意,在使用以恒定速度劃卡的自動劃卡機時這個觀點是不正確的。

圖8:增益改變過程

實現磁卡讀卡器

圖9顯示了基于賽普拉斯PSoC 1的雙磁道磁卡讀卡器實現方案。PSoC 1處理器具有與8位處理器內核集成在一起的可配置模擬和數字塊,在單顆芯片上集成了所有的功能。需要注意的是,圖中所示的無源器件是在處理器的外部。

圖9:PSoC 1磁卡讀卡器

由于傳感器信號可能是負的,因此必須用直流進行偏置。在PSoC 1中,模擬信號可以以不同于電源地的地為參考。這個地被稱為模擬地(AGND),輸入信號被鉗位到這個模擬地。信號隨后用可編程增益放大器(PGA)進行兩級放大。PGA是用連續時間模擬模塊實現的。它具有一個電阻陣列,當配置為放大器時用于改變增益。增益可以被配置為1至48之間18個選項之一。 CY8C28243 PSoC 1集成了一個最大采樣速率為150ksps的10位SAR ADC.

CPU讀取ADC,然后控制放大器增益。放大后的信號送到磁滯比較器產生邊沿接近信號峰值的數字信號。CPU隨后必須調整放大器增益,使其閾值接近峰值但不超過峰值。這有助于避免磁卡發生抖動時出現定時誤差。磁滯比較器輸出則送到定時器進行脈沖寬度測量。CPU讀取定時器輸出,并解碼為邏輯1或0的數據。當劃卡結束時,CPU打包數據比特,檢查是否有錯誤,然后通過I2C、SPI或UART接口將數據送給主機。

?

- 第 1 頁:極具成本效益的磁卡讀卡器設計

- 第 2 頁:讀卡頭靈敏度

本文導航

非常好我支持^.^

(0) 0%

不好我反對

(0) 0%

相關閱讀:

- [工業控制] MOVIPRO:電機初始化Starting up the motor encoder 2023-10-24

- [電子說] 一種用于高精度測量應用的低功耗模數轉換器(ADC)解決方案 2023-10-24

- [電子說] 學習STM32F103的ADC功能 2023-10-24

- [電子說] 無線模擬信號采集器0-10v0-5v 4-20mA數據wifi通訊 2023-10-24

- [電子說] 失調誤差是如何影響單極性ADC傳遞函數的? 2023-10-24

- [電子說] STM32速成筆記(7)—ADC 2023-10-24

- [電子說] 一文講解ADC模數轉換芯片的原理及轉換過程 2023-10-23

- [電子說] 功率分析儀中校零和消零方法 2023-10-23

( 發表人:廣立 )