極具成本效益的磁卡讀卡器設計 - 全文

通過磁性圖案存儲信息的技術最早出現(xiàn)在音頻記錄領域。從那以后,這個概念已被擴展應用于許多不同產(chǎn)品,如軟盤、音頻/視頻磁帶、硬盤以及磁條卡。本文將主要討論在全球金融交易和門禁控制中得到廣泛使用的磁條卡。

讀取磁條卡除了需要解碼數(shù)據(jù)的數(shù)字邏輯外還要求很重要的模擬電路。在磁卡上記錄數(shù)據(jù)是數(shù)字化的過程,通過沿著磁條長度磁化粒子完成。而成功讀取磁卡具有相當大的挑戰(zhàn)性,因為在實際應用中傳感器信號的幅度會隨著劃卡速度、磁卡質(zhì)量和讀卡磁頭的靈敏度而變化。此外,頻率也會隨著劃卡速度變化而變化。這就要求模擬電路能夠適應這種變化,無失真地處理傳感器信號。本文將介紹如何處理傳感器信號變化的機制。

磁性與磁卡

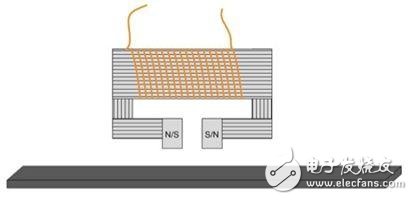

為了理解劃卡速度、磁卡質(zhì)量和傳感器靈敏度的影響,了解信息是如何存儲在卡上的以及如何被讀卡頭檢測出來很重要。在磁性存儲系統(tǒng)中,信息用諸如氧化鐵等磁化材料上的極性圖案表示。圖1顯示了涂覆在磁化材料上的磁條。磁化材料上的顆粒可能處于某種特定的排列方向,或者因以前沒有受到特定方向磁場的照射而處于隨機方向。然而,如果施加一定的外部磁場,磁條上的顆粒將按照外部磁場排列方向。

圖1:在外部磁場的影響下磁化材料按特定方向排列

在實用化系統(tǒng)中需要用到一個寫入磁頭,它其實就是繞在磁心上的一個線圈。通過控制線圈中的電流方向可以很容易編程磁場方向。這有助于在磁卡上形成南北極圖案。磁極之間的空隙越窄,磁卡上能夠編程的數(shù)據(jù)密度就越高。

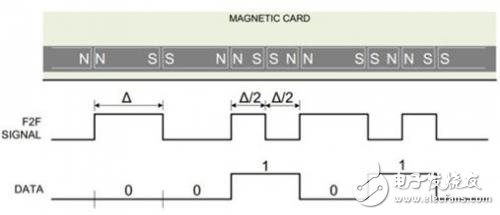

在F2F編碼機制中,如果在比特周期內(nèi)發(fā)生磁極轉(zhuǎn)換,那就代表邏輯1,否則代表邏輯0.例如圖3所示,如果比特周期是Δ,而磁極轉(zhuǎn)換發(fā)生在Δ/2處,那么這個比特就是邏輯1,否則就是邏輯0.注意,邏輯1和邏輯0在磁卡上占據(jù)的長度是相同的。不過比特周期Δ會隨劃卡速度而變化,這個問題在讀卡中必須加以解決。

圖2:用電磁體磁化磁條表示邏輯1和邏輯0,其中用到了F2F編碼機制

圖3:磁極圖案和數(shù)據(jù)

值得注意的是,比特周期長度對邏輯1和邏輯0來說都是相同的。

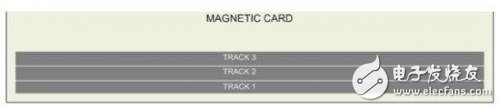

根據(jù)信息量的多少,數(shù)據(jù)將被編碼在不同的行,這個行被稱為磁道。一個磁卡上最多可以有3條磁道。

圖4:磁卡上的磁道

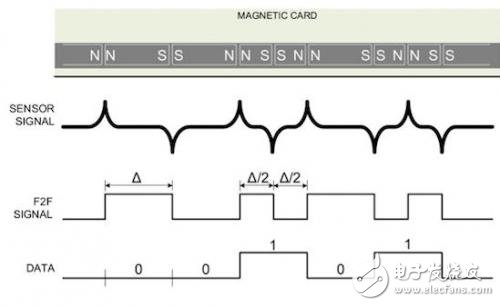

讀過程正好相反,它需要使用一個結(jié)構(gòu)上與圖2所示的線圈-磁芯相同的讀卡頭。需要注意的是,每個磁道要有一個傳感器。在劃卡時,源自磁條的磁場將在讀卡頭線圈中感應出電壓。圖5顯示了從讀卡頭得到的波形。

圖5:讀卡頭(傳感器)信號

信號在每次磁通量轉(zhuǎn)換時出現(xiàn)峰值。這是因為在磁極邊緣具有高密度的磁通量。正如你看到的那樣,信息是用信號峰值的位置表示的。峰值檢測器電路可以解碼這個信號,或者使用閾值非常接近信號峰值的磁滯比較器。不過在我們將這個信號交給檢測器電路之前,還需要進行額外的處理,原因如下:

劃卡速度:劃卡速度的單位規(guī)定為英寸/每秒(IPS)。一般來說,要求磁卡讀卡器能在5 IPS至50 IPS的劃卡速度范圍內(nèi)正常工作。傳感器信號的幅度隨劃卡速度變化而變化。劃卡速度增加,讀卡頭中的線圈切割的磁通量變化速度也增加,因此信號幅度會變大。與之相反,當劃卡速度變慢時,信號幅度將降低,從而增加數(shù)據(jù)讀取的難度。

磁卡質(zhì)量:隨著時間的推移以及使用量的增加,卡的質(zhì)量將隨著磁場強度的降低以及由于磁卡上的灰塵與刮擦而引起的失真加大而下降。這些因素綜合在一起將降低傳感器信號的幅度。

讀卡頭靈敏度:讀卡頭靈敏度取決于線圈匝數(shù)以及讀卡頭與磁條之間的間距。

由于所有這些參數(shù)的影響,信號幅度可能在幾百個uV至幾十個mV之間變化。這個范圍可以用放大器進行補償。但不能用固定增益放大器。當劃卡速度很高,卡的質(zhì)量又很好時,放大器輸出可以飽和到電源軌電壓。而當信號飽和時,用兩個連續(xù)峰值之間的時間差代表的信息將丟失。因此如實地放大傳感器信號、不至于使波形發(fā)生飽和或改變很重要。這就要求使用增益可配置的放大器,以便我們隨時調(diào)整增益。要做到這一點,系統(tǒng)必須能夠檢測信號變?nèi)醯臅r刻。這可以用跟蹤傳感器信號的ADC尋找近似的信號峰值來實現(xiàn)。

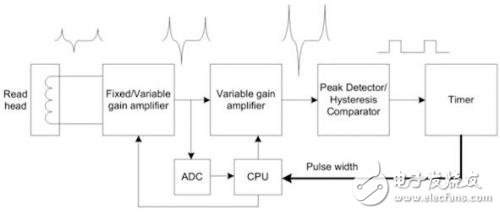

圖6顯示了一個完整的系統(tǒng)。最好將放大電路做成兩級,用ADC接收第一級電路的輸出。這樣就無需高分辨率ADC,8位ADC就足以滿足這種應用需求。第一級可以是固定增益的放大器,也可以是可變增益放大器。第二級是可變增益放大器。CPU讀取ADC結(jié)果,并通過調(diào)整增益使第二級放大器的信號輸出達到最佳。第二級放大器的輸出送到峰值檢測器/磁滯比較器電路進行峰值檢測。來自檢測器的脈沖輸出被饋送至定時器進行時間差測量,然后由CPU解碼出1和0.

圖6:磁卡讀卡器框圖

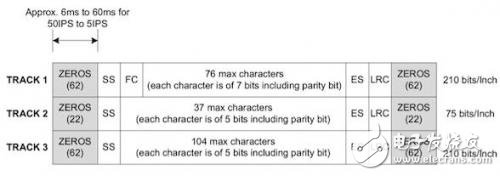

至此仍然存在增益更新之前是否有數(shù)據(jù)丟失的問題。為了避免這個問題,磁卡的兩頭會用前導零進行編碼以實現(xiàn)同步(這樣可以支持雙向劃卡)。這樣做的目的是使解碼器同步于劃卡速度。舉例來說,在磁道1中,共有約62個前導零。磁道1具有210個比特的數(shù)據(jù)密度。因此我們可以估算出劃卡速度為5 IPS時前導零將持續(xù)約60ms時間,劃卡速度為50 IPS時前導零將持續(xù)6ms.對另外兩個磁道來說或多或少是相同的,如圖7所示。在人為劃卡時一開始就是50 IPS的劃卡速度是不可能,因此系統(tǒng)具有比6ms長得多的時間來測量峰值并調(diào)整增益。圖8顯示了增益控制過程。

圖7:磁卡中三個磁道的內(nèi)容

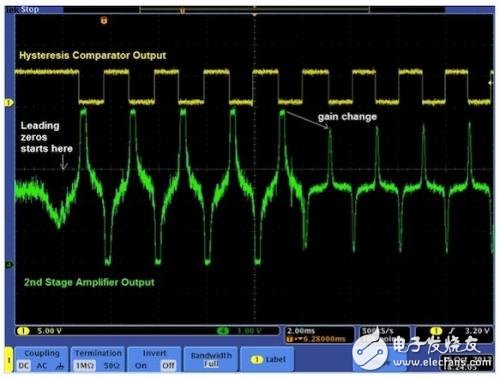

需要注意的是,CPU在劃卡期間可能會持續(xù)精細調(diào)整增益以適應變化的幅度。正常情況下,順著劃卡的方向,劃卡速度會增加,從而增加信號幅度。注意,在使用以恒定速度劃卡的自動劃卡機時這個觀點是不正確的。

圖8:增益改變過程

實現(xiàn)磁卡讀卡器

圖9顯示了基于賽普拉斯PSoC 1的雙磁道磁卡讀卡器實現(xiàn)方案。PSoC 1處理器具有與8位處理器內(nèi)核集成在一起的可配置模擬和數(shù)字塊,在單顆芯片上集成了所有的功能。需要注意的是,圖中所示的無源器件是在處理器的外部。

圖9:PSoC 1磁卡讀卡器

由于傳感器信號可能是負的,因此必須用直流進行偏置。在PSoC 1中,模擬信號可以以不同于電源地的地為參考。這個地被稱為模擬地(AGND),輸入信號被鉗位到這個模擬地。信號隨后用可編程增益放大器(PGA)進行兩級放大。PGA是用連續(xù)時間模擬模塊實現(xiàn)的。它具有一個電阻陣列,當配置為放大器時用于改變增益。增益可以被配置為1至48之間18個選項之一。 CY8C28243 PSoC 1集成了一個最大采樣速率為150ksps的10位SAR ADC.

CPU讀取ADC,然后控制放大器增益。放大后的信號送到磁滯比較器產(chǎn)生邊沿接近信號峰值的數(shù)字信號。CPU隨后必須調(diào)整放大器增益,使其閾值接近峰值但不超過峰值。這有助于避免磁卡發(fā)生抖動時出現(xiàn)定時誤差。磁滯比較器輸出則送到定時器進行脈沖寬度測量。CPU讀取定時器輸出,并解碼為邏輯1或0的數(shù)據(jù)。當劃卡結(jié)束時,CPU打包數(shù)據(jù)比特,檢查是否有錯誤,然后通過I2C、SPI或UART接口將數(shù)據(jù)送給主機。

?

- 第 1 頁:極具成本效益的磁卡讀卡器設計

- 第 2 頁:讀卡頭靈敏度

本文導航

非常好我支持^.^

(0) 0%

不好我反對

(0) 0%

相關閱讀:

- [工業(yè)控制] MOVIPRO:電機初始化Starting up the motor encoder 2023-10-24

- [電子說] 一種用于高精度測量應用的低功耗模數(shù)轉(zhuǎn)換器(ADC)解決方案 2023-10-24

- [電子說] 學習STM32F103的ADC功能 2023-10-24

- [電子說] 無線模擬信號采集器0-10v0-5v 4-20mA數(shù)據(jù)wifi通訊 2023-10-24

- [電子說] 失調(diào)誤差是如何影響單極性ADC傳遞函數(shù)的? 2023-10-24

- [電子說] STM32速成筆記(7)—ADC 2023-10-24

- [電子說] 一文講解ADC模數(shù)轉(zhuǎn)換芯片的原理及轉(zhuǎn)換過程 2023-10-23

- [電子說] 功率分析儀中校零和消零方法 2023-10-23

( 發(fā)表人:廣立 )