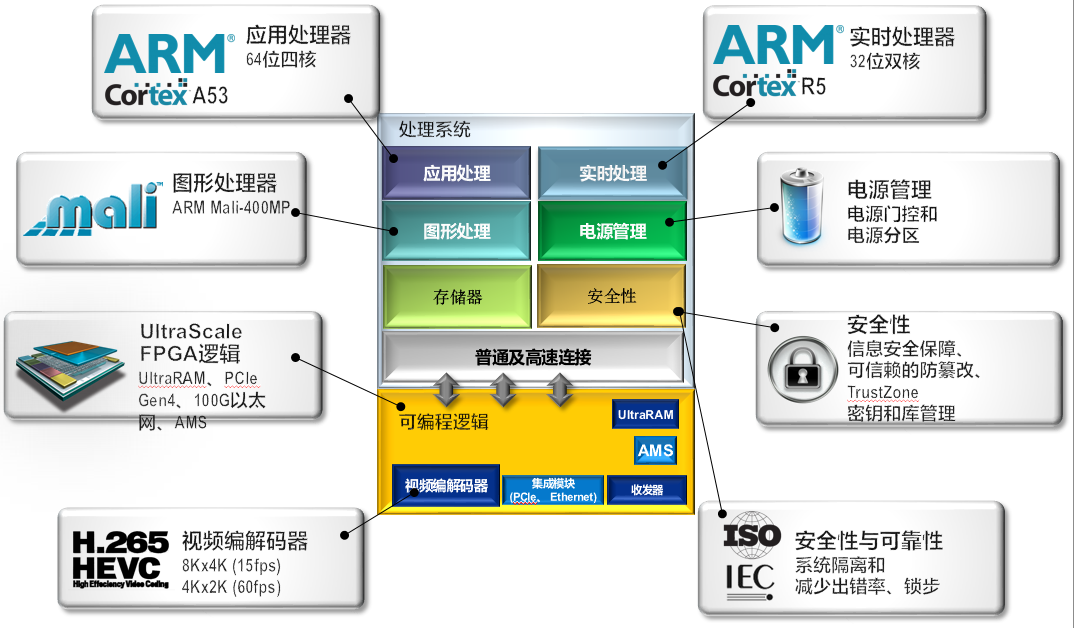

賽靈思 Zynq UltraScale+系列簡介

高級數據中心應用、汽車駕駛員輔助與安全系統以及手持無線電設計都需要可擴展的 SoC IP,因為這種 ....

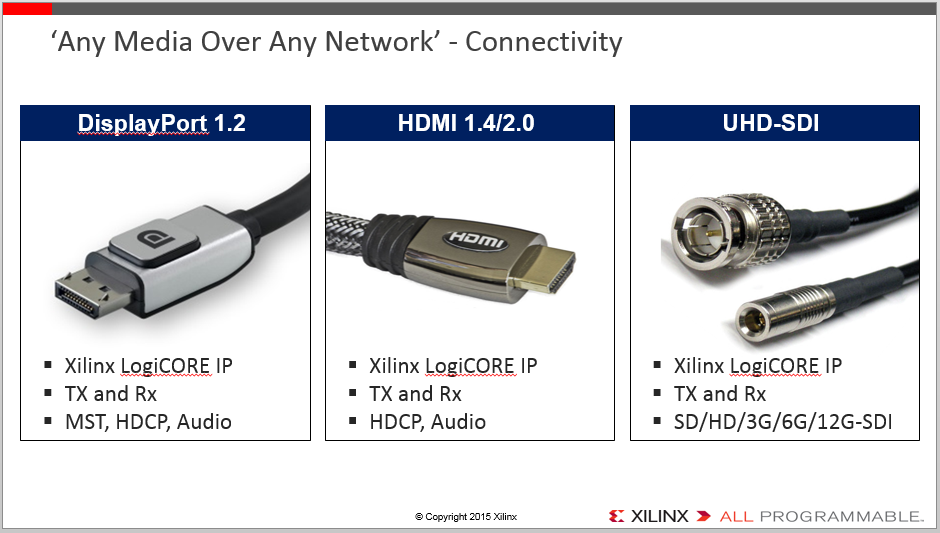

Skreens演示了最新消費集成顯示平臺

當今的消費者正在以多種方式使用電視屏幕來觀看各種內容, 包括線性電視、時移電視、OTT 電視廣播和在....

Vivado--16nm開發最好工具

學習如何執行 UltraFAST 設計方法中的”Checklist“功能來確保您的設計以及設計環境已....

鼎陽科技的發展之初

2002年,一臺最便宜的泰克示波器在中國市場要賣接近10,000RMB,想要擁有一臺屬于自己的數字示....

賽靈思Vivado新手上手教程

了解與學習在 Vivado 中當默認設置無法滿足您的設計目標時,如何設置和嘗試新的布局布線算法。視頻....

Vivado 中時效的處理

UltraFAST設計方法培訓將幫助您時序收斂階段實現“Sign-off” 質量XDC約束。另外,還....

關于FPGA的兩個作品方案演示

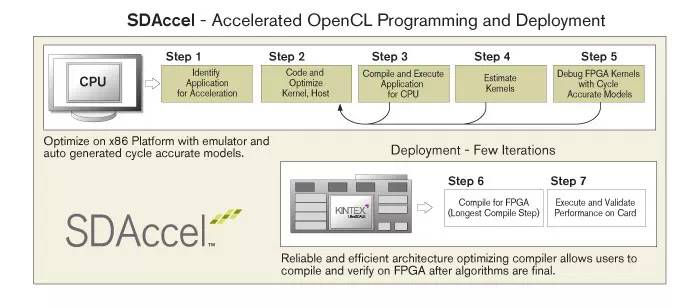

展示了賽靈思 SDAccel 開發環境的運行情況,并演示了一個軟件程序員是如何在OpenCL中捕獲一....

圖像處理加速和100G實例演示

賽靈思認證聯盟成員 Netcope 公司演示了在一個雙CPU服務器主板上,兩個基于Virtex-7的....

FPGA方案作品演示

Ryft 公司在本次展會上展示了他們的 Ryft ONE 產品(具有超快速、簡單易用、可擴展的 FP....

FPGA產品演示

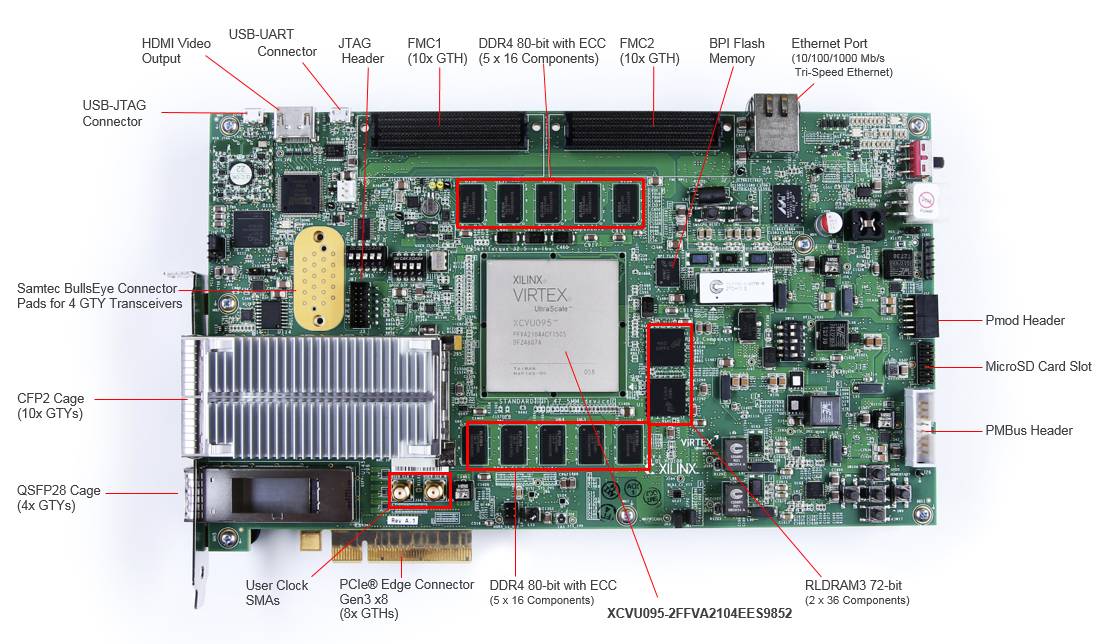

展示了來自 Alpha Data 公司現已公開發售的賽靈思 FPGA 加速卡產品,包括最新的支持10....

展示了基于 FPGA 的超算方案與產品

演示了使用 SDAccel 編譯器技術創建的機器學習(Machine Learning)解決方案。應....

20nm 高性能套件性能介紹

無論您需要描述和評估 Virtex UltraScale FPGA 的 GTH (16Gb/s) 或....

賽靈思宣布支持16nm UltraScale+器件工具與文檔公開支持主流市場

通過與 Vivado 設計套件的協同優化可以完全發揮 UltraScale+ 產品系列的功耗性能比優....

FPGA 和 SoC 架構是最理想的平臺

通過自動化提高生產率至關重要的因素是具有確定時間行為的連接性,以及全廠范圍內的兼容性。以太網工業級交....

關于未來5G無線的應用

5G 可在幾乎任何地方更快、更可靠地連接數十億設備。它將遠遠超越目前的移動體驗,將為 100 倍的互....

賽靈思 Virtex UltraScale VU440 FPGA榮膺“最佳產品獎”

Virtex UltraScale VU440 FPGA 是賽靈思2015年1月率先發貨的全球最大容....

使用全可編程SoC實現完整的射頻單元設計研發會

運營商一直在努力尋求更高的帶寬,兼容多種無線空口標準,并支持更多天線以從MIMO增益中獲益。研討會將....

OpenCL編程環境作用和介紹

Xilinx 已經形成一個聯盟成員的全球生態系統,可提供各種平臺、庫和設計服務幫助全球設計團隊充分利....

Xilinx宣布與TSMC開展7nm工藝合作

“臺積公司是我們在 28nm、20nm 和 16nm 實現‘三連冠(3 Peat)’成功的堅實基礎。....

Vivado:行業首款 SoC 增強型設計套件最新消息

交互式時鐘域的交叉分析:該功能支持設計人員在設計早期階段調試CDC問題。結合Vivado設計套件的交....

賽靈思公司和恩智浦半導體公司宣布,將降低資本支出和運營支出成本

高效功率放大器實現了同樣出色的無線電輸出功率,而且通過使用額定功率較低的設備以及減少冷卻機械裝置數量....

賽靈思公司宣布,其SDAccel開發環境現已通過一致性測試

中國最大的搜索引擎提供商百度現已轉用深度神經網絡(DNN)處理技術來解決語音識別、圖像搜索以及自然語....

Vivado 設計套件使用方法和注意事項

想到要寫這一系列關于工具和方法學的小文章是在半年多前,那時候Vivado已經推出兩年,陸陸續續也接觸....