AMD Vivado Design Suite 2023.2的優(yōu)勢(shì)

由于市場(chǎng)環(huán)境日益復(fù)雜、產(chǎn)品競(jìng)爭(zhēng)日趨激烈,為了加快推出新型自適應(yīng) SoC 和 FPGA 設(shè)計(jì),硬件設(shè)計(jì)....

使用PCIE更新AMD ZYNQ的QSPI Flash參考設(shè)計(jì)

AMD ZYNQ 7000 的 S_AXI 端口提供了外設(shè)訪問(wèn) PS 內(nèi)部外設(shè)控制器的接口,這其中包....

什么是COP?能為開(kāi)發(fā)者帶來(lái)哪些優(yōu)勢(shì)?如何選擇最佳COP器件?

使用可編程邏輯器件進(jìn)行設(shè)計(jì)時(shí),最關(guān)鍵的步驟之一就是為應(yīng)用選擇最佳的器件。

CPRI的數(shù)據(jù)幀結(jié)構(gòu)與初始化流程

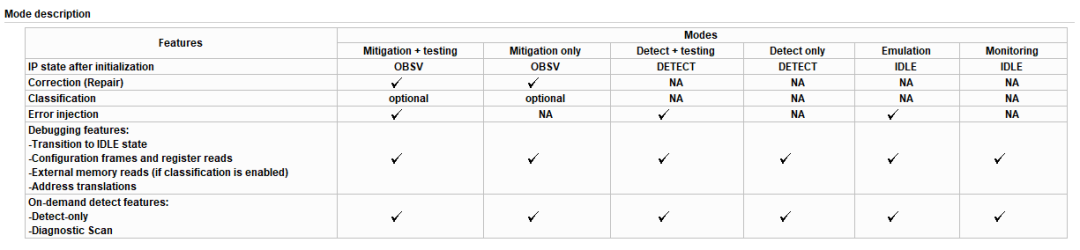

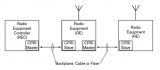

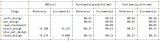

CPRI 是無(wú)線通信里的一個(gè)標(biāo)準(zhǔn)協(xié)議,連接 REC 和 RE 的通信。AMD 有提供 CPRI IP....

節(jié)省編譯時(shí)間的解決方法

影響編譯時(shí)間的因素有很多,包括工具流程、工具設(shè)置選項(xiàng)、RTL 設(shè)計(jì)、約束編輯、目標(biāo)器件以及設(shè)計(jì)實(shí)現(xiàn)期....

為多個(gè)Vivado?工程復(fù)用遠(yuǎn)程IP高速緩存

在設(shè)計(jì)周期中,您可保留多個(gè)版本的工程,這些工程使用相同的 IP 和相同的配置。重新運(yùn)行整個(gè)工程會(huì)導(dǎo)致....

利用Tcl腳本節(jié)省編譯時(shí)間

這篇博文介紹了多種自動(dòng)生成報(bào)告的有效途徑,以便您在嘗試對(duì)設(shè)計(jì)中特定階段所耗用的編譯時(shí)間進(jìn)行調(diào)試時(shí)使用....

使用增量綜合節(jié)省編譯時(shí)間

增量綜合的工作方式與增量實(shí)現(xiàn)流程相似,但僅適用于綜合階段,并且不會(huì)對(duì)緊隨其后的實(shí)現(xiàn)階段給予引導(dǎo)。

Power Design Manager (PDM) 2023.1的新增功能

PDM 已經(jīng)與其它 AMD FPGA 和自適應(yīng) SoC 工具一起集成到統(tǒng)一的安裝程序中。這是一款獨(dú)立....

節(jié)省編譯時(shí)間系列-使用增量實(shí)現(xiàn)

增量實(shí)現(xiàn)自從首次獲得支持以來(lái),不斷升級(jí)演變,在此過(guò)程中已添加了多項(xiàng)針對(duì)性能和編譯時(shí)間的增強(qiáng)功能。

如何獲取和使用Github上的Vitis開(kāi)放資源

自從 Vitis 的發(fā)布,AMD 在 Github 上也開(kāi)源了很多資源,方便開(kāi)發(fā)者進(jìn)行自己的設(shè)計(jì),減....

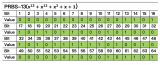

Versal GTM如何用Tcl命令在IBERT生成QPRBS13序列

目前對(duì)于 Vivado 2023.1 版本的 IBERT GUI 界面暫時(shí)不支持 QPRBS13 的....

Vitis HLS相關(guān)問(wèn)答詳解

需要手工在 C++ 代碼里明確指定可并行執(zhí)行的任務(wù)(用 task,添加頭文件 hls_task.h)....

在X86處理器上跑嵌入式應(yīng)用程序的Software Emulation

在 Vitis 流程中,編譯的目標(biāo)分為軟件仿真(software emultion),硬件仿真(ha....

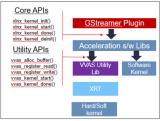

使用VVAS調(diào)用HLS生成硬件加速器的主要流程

本篇博客介紹 VVAS 框架所支持調(diào)用的 H/W(HLS) 內(nèi)核。 H/W 內(nèi)核指的是使用 HLS ....

使用VVAS開(kāi)發(fā)軟件應(yīng)用

Vitis 視頻分析 SDK 是在 AMD 平臺(tái)上構(gòu)建 AI 驅(qū)動(dòng)的智能視頻分析解決方案的完整軟件棧....

在Vivado中利用Report QoR Suggestions提升QoR

Report QoR Suggestions (RQS) 可識(shí)別設(shè)計(jì)問(wèn)題,并提供工具開(kāi)關(guān)和可影響工具....

淺談Vitis AI 3.5發(fā)布亮點(diǎn)

Vitis AI 平臺(tái)是為 AMD 器件、板卡及 Alveo 數(shù)據(jù)中心加速卡提供的一款綜合 AI 推....

視覺(jué)L1重映射函數(shù)Zynq baremetal設(shè)計(jì)實(shí)例

這篇博客展示了在 AMD Zynq 設(shè)計(jì)中,如何用 Vitis Vision Library 中的函....

如何在IBER眼圖上添加模板

標(biāo)準(zhǔn)協(xié)議的規(guī)范中一般都對(duì)眼圖模板都有詳細(xì)的規(guī)定,使用 IBERT 完成眼圖掃描后,通過(guò)設(shè)置一些參數(shù),....

在Vitis中通過(guò)PSU DDR執(zhí)行MicroBlaze應(yīng)用

MicroBlaze CPU 是可修改的拖入式預(yù)設(shè) 32 位/64 位 RISC 微處理器配置系列。

如何解決MPSoC萬(wàn)兆以太網(wǎng)應(yīng)用中UDP接收丟包問(wèn)題

本文介紹如何使能 Linux 網(wǎng)絡(luò)協(xié)議棧中的 RFS(receive flow steering)功....

如何在IP集成器中將單工TX/RX核合并到多個(gè)Quad

要為 Versal 的多個(gè) Quad 創(chuàng)建收發(fā)器設(shè)置,建議從 Transceiver Bridge ....

Versal HBM系列外部參考時(shí)鐘設(shè)計(jì)指南文章

Versal HBM 棧可通過(guò)內(nèi)部 HSM0 參考時(shí)鐘來(lái)進(jìn)行時(shí)鐘設(shè)置,此參考時(shí)鐘是由 CIPS 或外....