摘要:在m序列產生原理的基礎上,利用2片74LS194級聯及少量門電路,采用手動置數和自啟動2種方法設計了2種m序列發生器電路,然后分析比較了2種電路的產生原理.最后分析了實驗結果,驗證了m序列的均衡性、游程分布特性及移位相加性.電路性能穩定可靠,已作為數字信號源成功應用于通信原理實驗中

1、m序列的產生原理

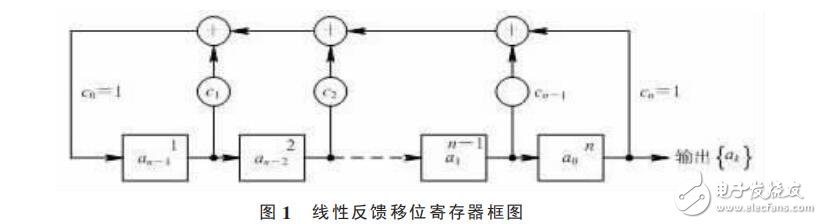

m序列發生器是一種反饋移位型結構的電路,它由n級移位寄存器加異或反饋網絡組成,其生成序列長度p=2n-1,且只有1個冗余狀態即全0狀態,所以稱為最長線性反饋移位寄存器序列.由于帶有反饋,因此在移位脈沖作用下,移位寄存器各級的狀態將不斷變化,通常移位寄存器的最后一級做輸出,輸出序列為邀ak妖=a0a1…an-1…

輸出序列是一個周期序列,其特性由移位寄存器的級數、初始狀態、反饋邏輯以及時鐘速率(決定著輸出碼元的寬度)所決定.

當移位寄存器的級數與時鐘一定時,輸出序列就由移位寄存器的初始狀態和反饋邏輯所完全確定.當初始狀態為全零狀態時,移位寄存器輸出全0序列.為了避免這種情況,需設置全0排除電路。

2、m序列發生器的電路設計

2.1芯片介紹

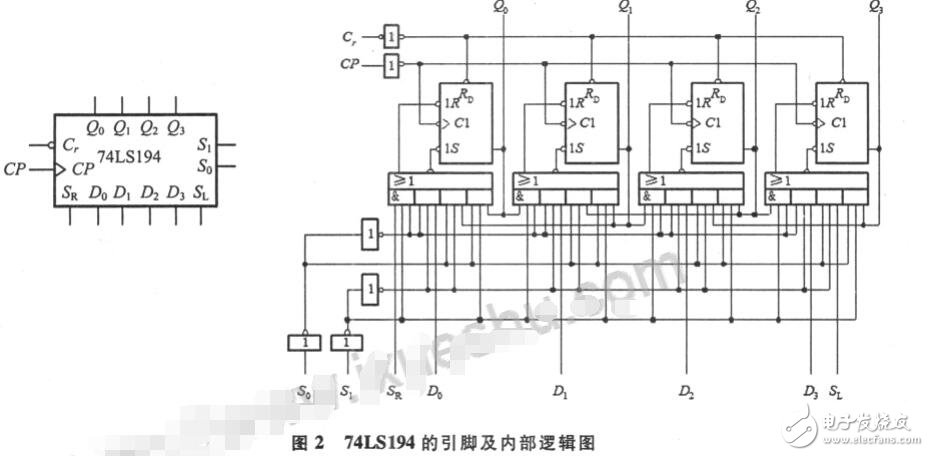

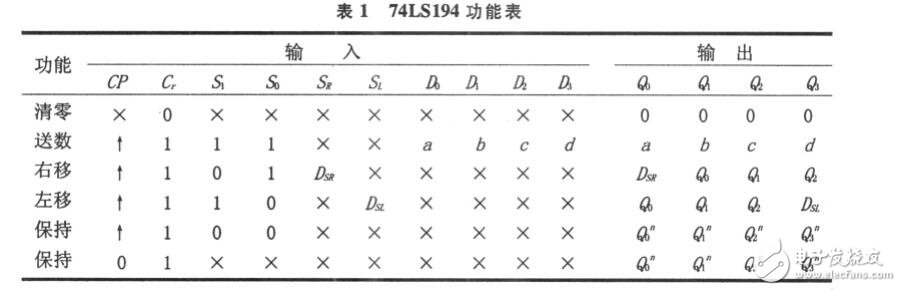

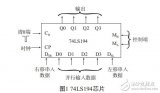

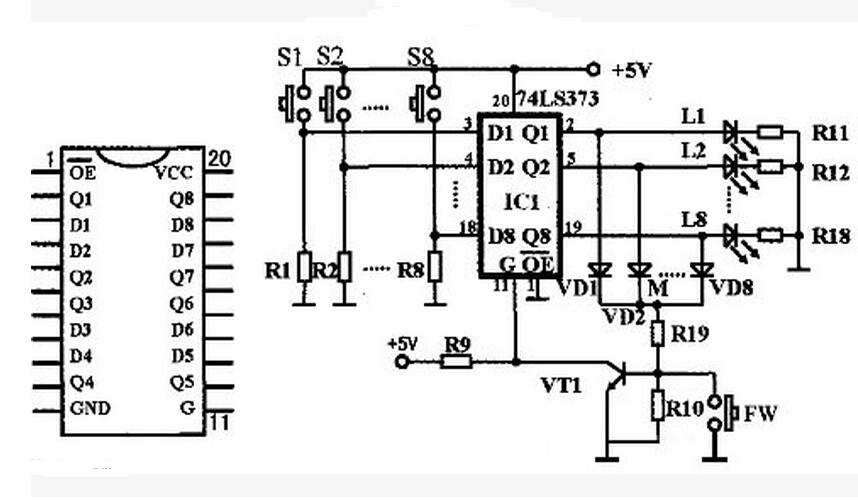

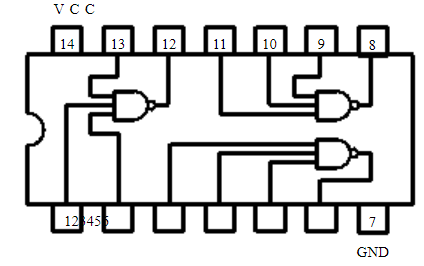

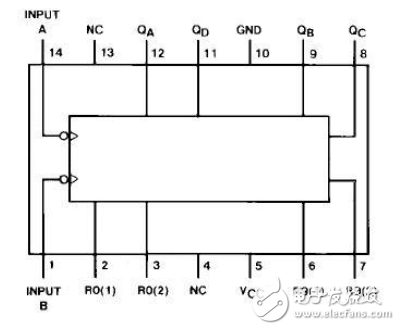

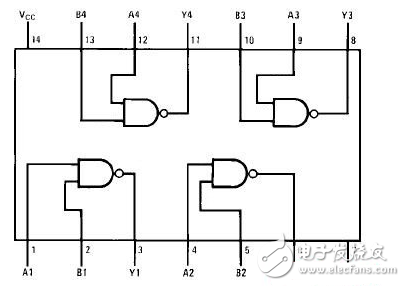

本設計采用2片4級移位寄存器芯片74LS194及少量分立元件構成,74LS194的引腳及內部邏輯圖如圖2所示.

74LS194是一種典型的中規模集成移位寄存器,由4個RS觸發器和一些門電路構成.它是4級雙向移位寄存器,是一種功能很強的通用寄存器,其具體邏輯功能由管腳9和管腳10的S0與S1來確定.它具有并行輸入、并行輸出、左移、右移及保持等5個功能.其中D0,D1,D2和D3為并行數據輸入端;Q0,Q1,Q2和Q3為4個觸發器輸出端;SR為右移串行輸入端;SL為左移串行輸入端;S0與S1為操作模式控制端;Cr為直接無條件清零端;CP為時鐘脈沖輸入端.

當S0S1=00時,為狀態保持;S0S1=01為數據右移;S0S1=10為數據左移;S0S1=11為并行送數.74LS194功能表如表1所示

2.2電路設計與分析

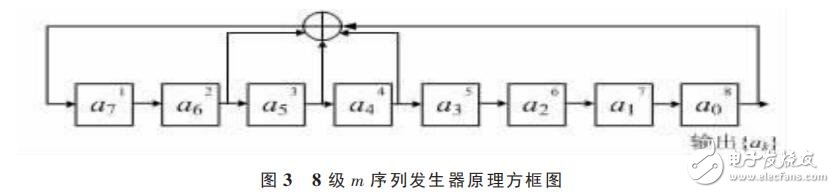

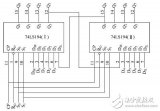

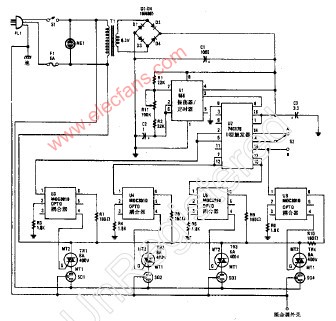

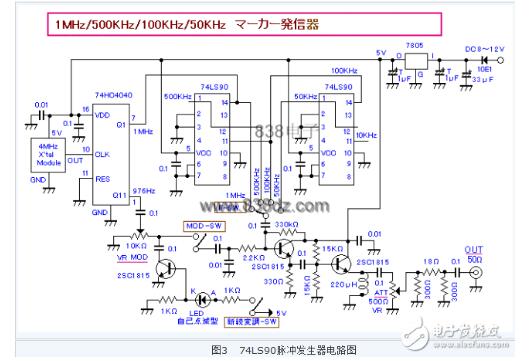

要想產生周期為255的最長序列,要求m序列發生器的特征多項式必須是8次本原多項式,通過查表得到其本原多項式為x8+x4+x3+x2+1,即第8,4,3,2級參與反饋經異或后送入第1級.所設計的8級m序列發生器原理方框圖如圖3所示.

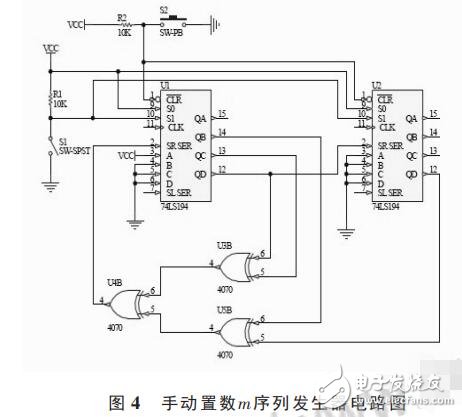

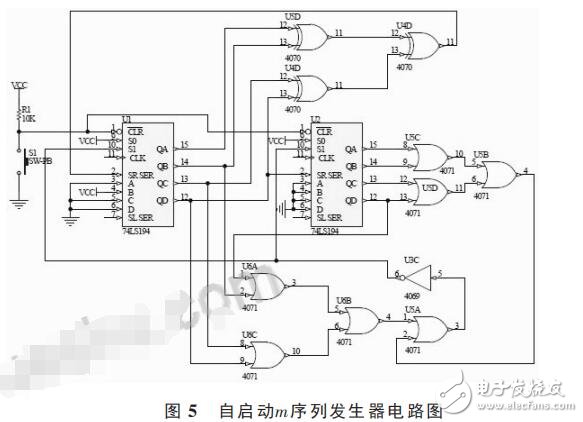

依據上述原理,設計了2種產生電路,分別如圖4和圖5所示.

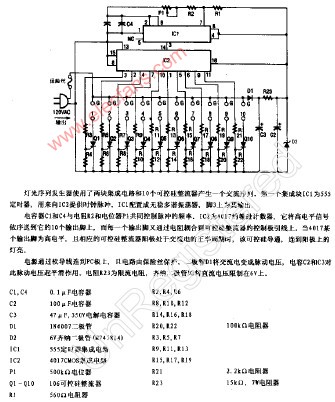

方案1:通過手動置數右移產生m序列.

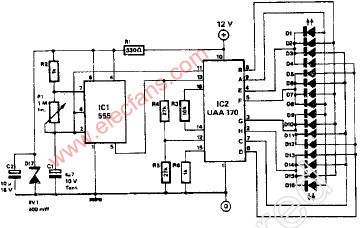

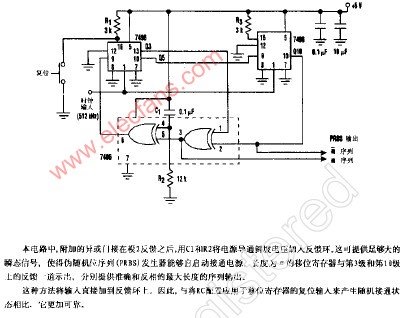

方案2:利用全0狀態重新置數從而實現自啟動

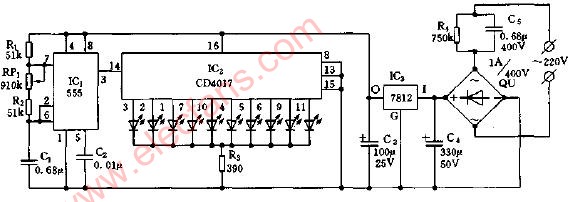

方案1的電路設計如圖4所示.當電路處于全0狀態時,采用此方法設計的m序列發生器不具有自啟動特性.為了使電路啟動,可以斷開開關S1,將74LS194的工作方式控制端S1置高電平,這時S1和S0均為高電平,即S1S0=11,74LS194處于置數狀態,把輸入端的初始狀態10000000置到輸出端.然后再閉合開關S1,使74LS194的工作方式控制端S1處于低電平狀態.這時工作方式控制端S1與S0分別為低電平和高電平,即S1S0=01,74LS194處于右移狀態,在時鐘作用下通過不斷移位產生m序列.

當初始狀態為全零狀態時,移位寄存器輸出全0序列.為了避免這種情況,需設置全0排除電路.方案2的電路設計如圖5所示.利用全0狀態重新置數從而實現自啟動.當電路處于全0狀態時,通過或門和非門電路的作用,S1置高電平,這時候S1和S0均為高電平,即S1S0=11,74LS194處于置數狀態,自動把輸入端的初始狀態01000000置到輸出端.通過或門和非門電路的作用,使S1處于低電平狀態,即S1S0=01,74LS194處于右移狀態,在時鐘作用下通過不斷移位產生m序列.

比較2種方案,通過設置工作方式控制端使之右移都能產生長度為255的m序列.方案1的電路設計簡單,只需手動置數就能產生m序列;方案2的電路設計較方案1復雜,但它能在全0狀態下自啟動,電路性能穩定。

電子發燒友App

電子發燒友App

評論