74ls160數字鐘仿真電路(一)

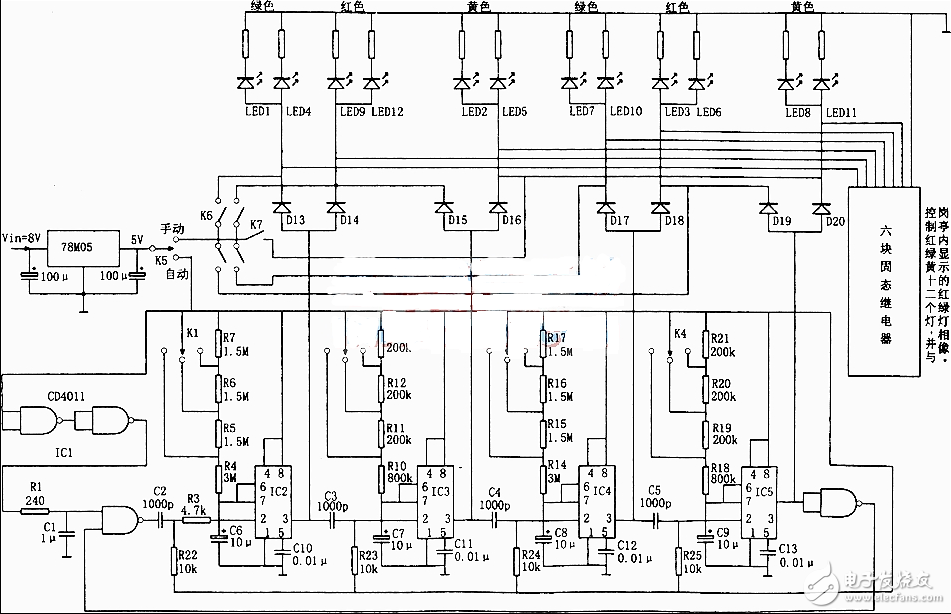

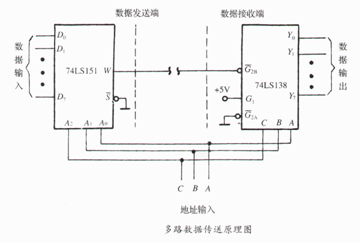

數字鐘是計數電路的一種典型應用,其構成原理框圖如下圖所示。它主要由三部分組成:

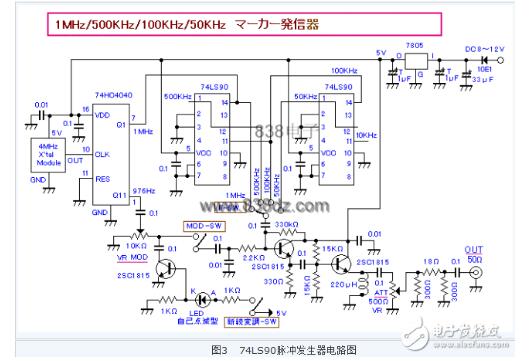

(1)秒脈沖發生電路

它由32768Hz的石英晶體振蕩器和若干級分頻電路構成,振蕩器產生32768Hz的方波,由于使用了晶體,振蕩頻率準確且穩定,經過216=65536分頻后,再經過2倍頻,得到秒脈沖信號,該秒脈沖信號經過控制門進入秒計數器進行計數。

(2)時間校準電路

時間調整由3個開關AN1、AN2、AN3以及3個R-S觸發器構成。當3個開關都撥到右邊時,R-S觸發器的輸出Q1、Q2、Q3都為1,因此控制門的3個右邊門開啟,秒、分、時脈沖可以正常進入相應計數器進行計數。當某開關撥到左邊時,R-S觸發器翻轉,例如當“秒調整”開關撥到左邊,Q1-0、,控制門的右門關、左門開,秒脈沖不能通過,而0.5s的脈沖信號卻可以進入秒計數器實現“秒調整”。分、時的調校原理與此相同,使用R—S觸發器的目的是為了消除開關抖動產生的影響。

(3)時、分、秒計數電路

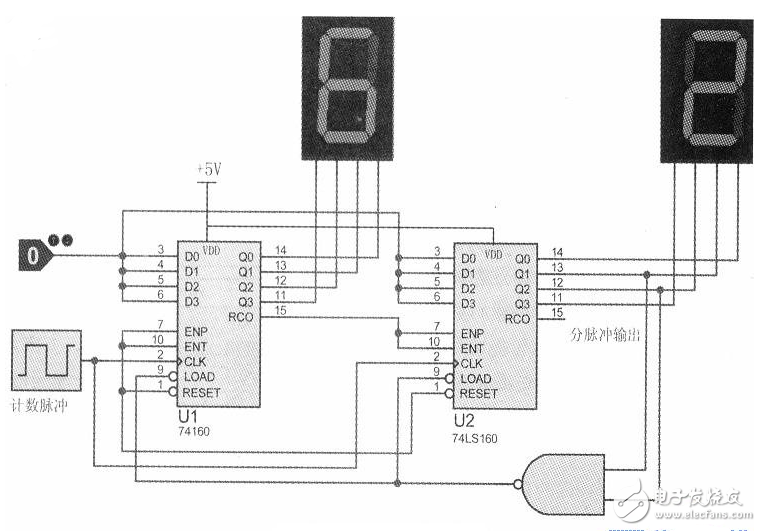

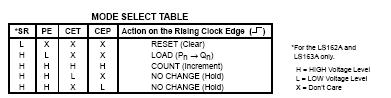

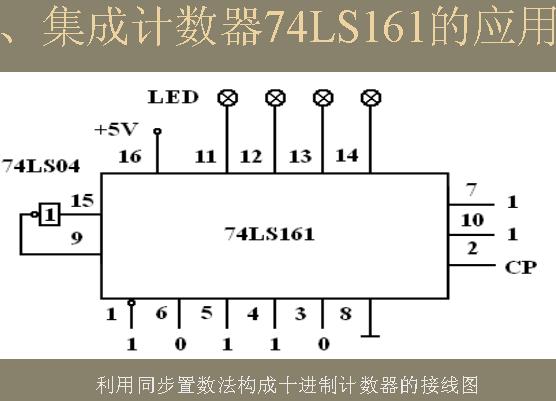

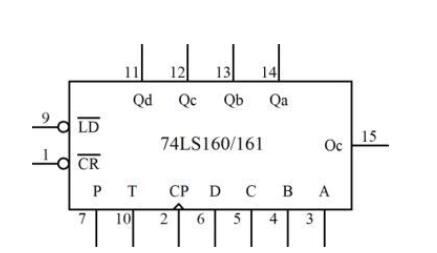

采用兩片74LS160按下圖所示連接,可以構成作60分頻計數,用于數字鐘中的秒計數器。

標準秒脈沖經過控制門進入秒計數器,并顯示其計數值,當計數滿60時得到一個進位“分”脈沖,同時秒計數器自動清零。“分”脈沖經控制門送入“分計數器”又作60分頻計數,當計數滿后得到進位“時”脈沖。“時”脈沖再經控制門送入“時計數器”計數。“分計數器”與“時計數器”的計數、復零和顯示原理與“秒計數器”相同,可以自行設計。

74ls160數字鐘仿真電路(二)

電子鐘計時分為小時、分鐘和秒,其中小時為二十四進制,分鐘和秒均為六十進制,輸出可以用數碼管顯示,所以要求二十四進制為00000000~00100100計數,六十進制為00000000~01100000計數,并且均為8421碼編碼形式。

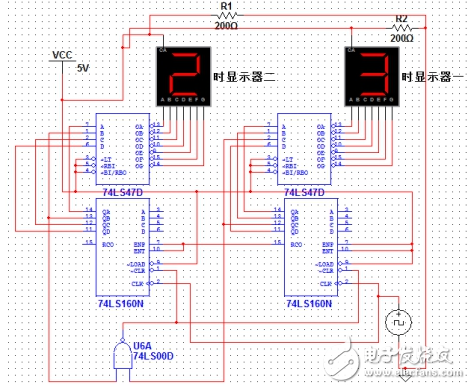

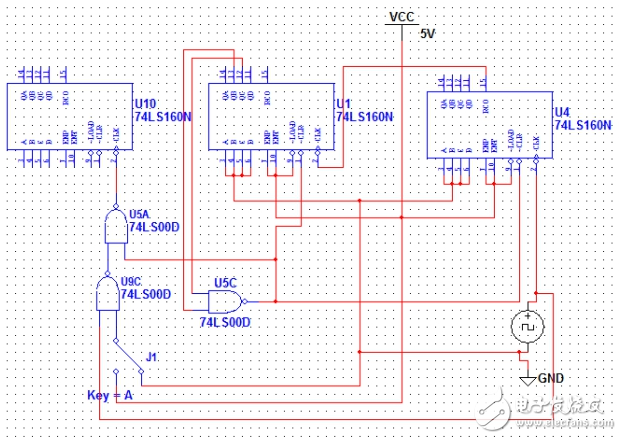

(1)小時計數——二十四進制電路仿真

用兩片74LS160N(分A片、B片)設計一個一百進制的計數器,在24(00100100)處直接取出所有為1的端口,經過輸入與非門74LS00D,再給兩個清零端CLR。使用74LS160N異步清零功能完成二十四進制循環,計數范圍為0~23。然后用七段顯示譯碼器74LS47D將A、B兩片74LS160N的輸出譯碼給LED數碼管。仿真電路如圖九所示。:

圖九24進制——時計數器仿真電路

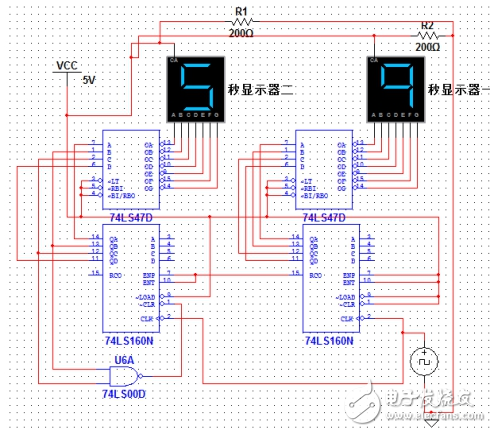

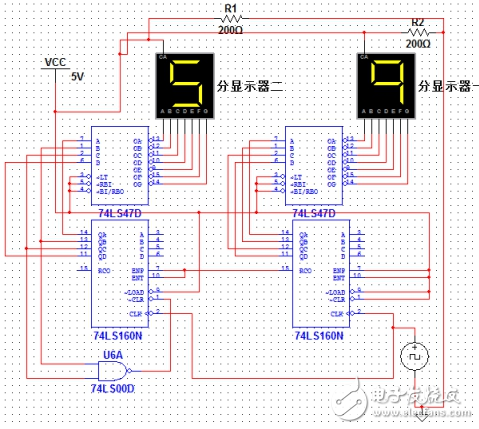

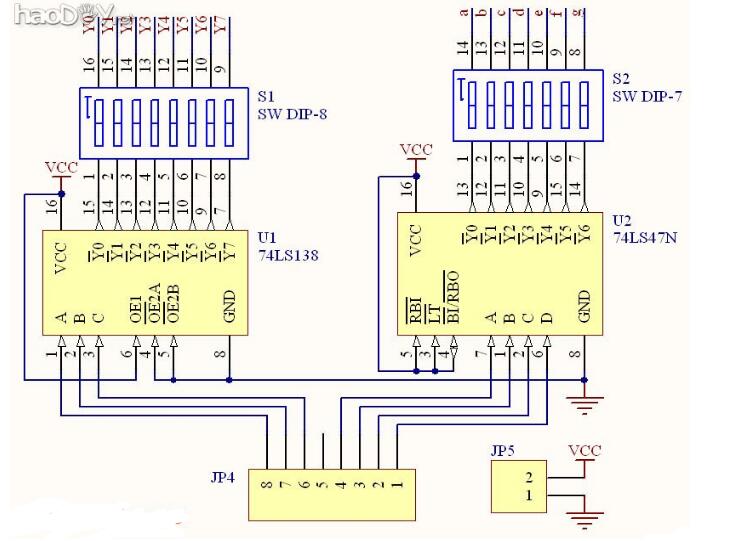

(2)分鐘、秒計數——六十進制電路仿真

此電路類似于二十四進制計數器,采用74LS160N設計出一百進制的計數器,在60(01100000)處直接取出所有為1的端口,經過輸入與非門74LS00D,再給兩個清零端CLR。使用74LS160N異步清零功能完成六十進制循環,計數范圍為0~59。然后用七段顯示譯碼器74LS47D將A、B兩片74LS160N的輸出譯碼給LED數碼管。仿真電路如圖所示:

圖十60進制——秒計數器仿真電路

圖十一60進制——分計數器仿真電路

(四)校時校分(秒)電路。

數字鐘應具有分校正和時校正功能,因此,應截斷分個位和時個位的直接計數通路,并采用正常計時信號與校正信號可以隨時切換的電路接入其中。這里利用兩個與非門加一個單刀雙擲開關來實現校時功能。第一個74LS00D與非門的輸入端一端接清零信號,另一端接第二個與非門的輸入端,第二個74LS00D的輸入端一端接計數脈沖,另一端接一個單刀雙擲開關。開關接通的一段接地,另一端接高電平。當開關打到另一端時,時或分的個位就單獨開始計數,這樣就能實現校時功能。其電路圖如圖所示:

圖十二校分仿真電路

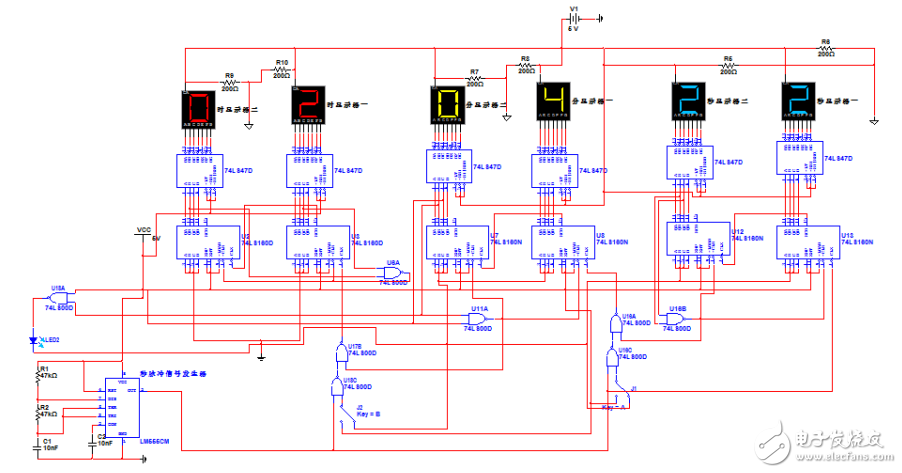

數字時鐘仿真電路圖如下圖所示,在Multisim11.0中進行仿真,可以實現數字時鐘的顯示功能、校時功能。顯示功能中,小時實現的是24進制,分和秒實現的是60進制,通過校時電路能夠分別校對時和分。

圖十三數字時鐘仿真電路

74ls160數字鐘仿真電路(三)

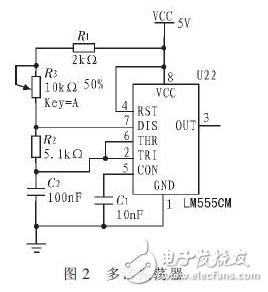

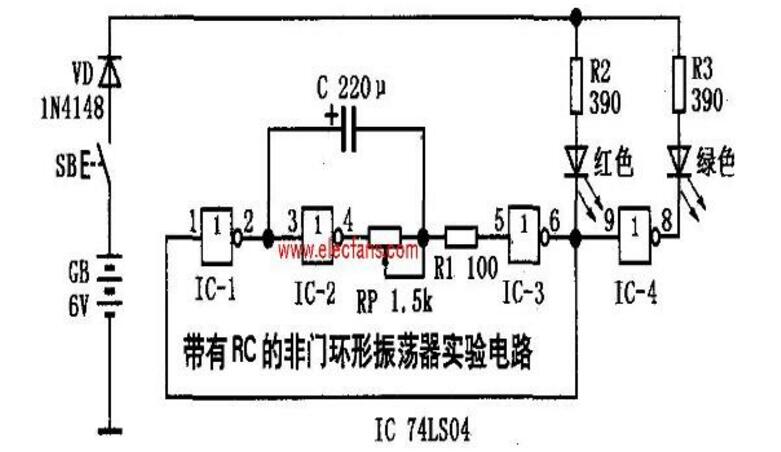

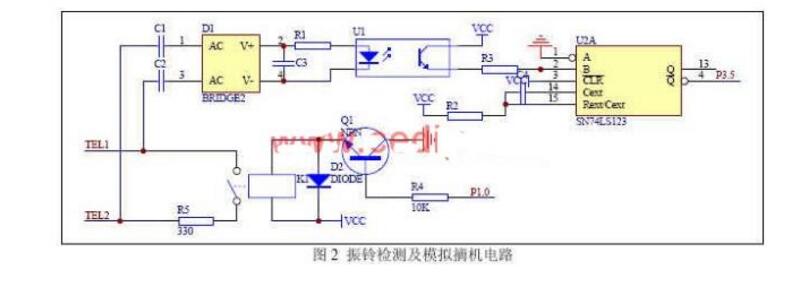

振蕩器

本系統的振蕩器采用由555定時器與RC組成的多諧振蕩器來實現,如圖2所示即為產生1kHz時鐘信號的電路圖。此多諧振蕩器雖然產生的脈沖誤差較大,但設計方案快捷、易于實現、受電源電壓和溫度變化的影響很小[4]。

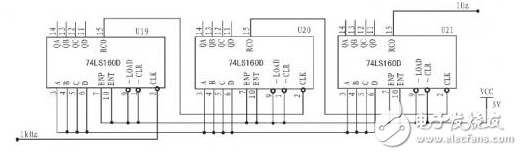

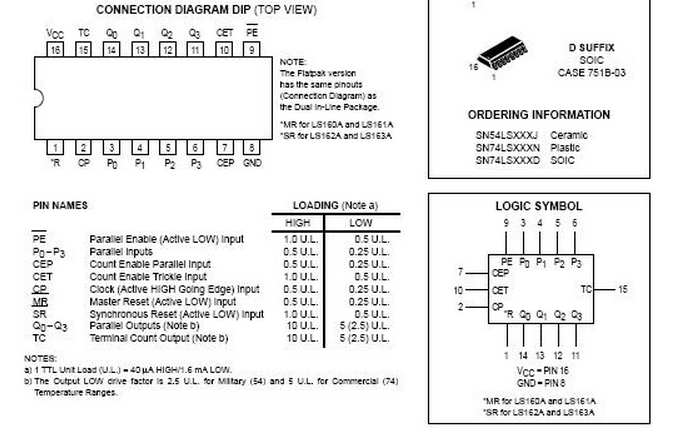

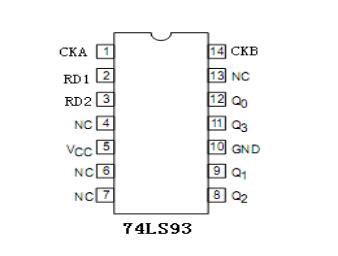

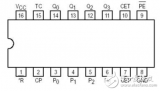

分頻器

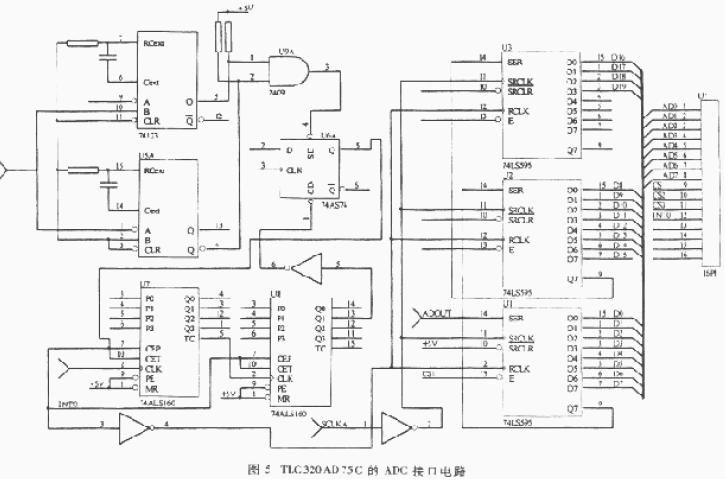

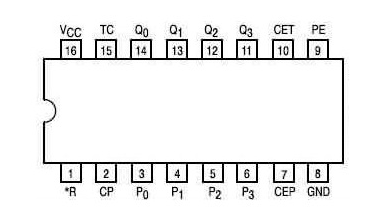

由于振蕩器產生的頻率高,要得到標準的秒信號,就需要對所得到的信號進行分頻。在此電路中,分頻器的功能主要有兩個:1)產生標準脈沖信號;2)提供電路工作需要的信號,比如擴展電路需要的信號。通常實現分頻器的電路是計數器電路,選擇74LS160十進制計數器來完成上述功能[5]。如圖3所示,555定時器產生1kHz的信號,經過3次1/10分頻后得到1Hz的脈沖信號,為秒個位提供標準秒脈沖信號。

時間計數器

計數器是一種計算輸入脈沖的時序邏輯網絡,被計數的輸入信號就是時序網絡的時鐘脈沖,它不僅可以計數而且還可以用來完成其它特定的邏輯功能,如測量、定時控制、數字運算等等。

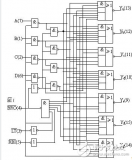

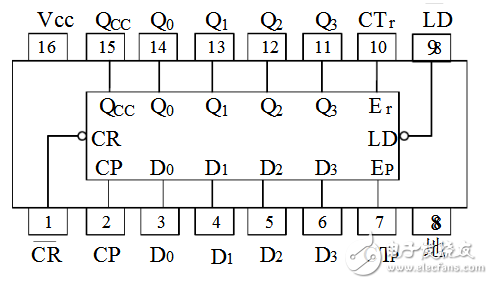

本部分的設計仍采用74LS160作為時間計數器來實現時間計數單元的計數功能。時間計數器由秒個位和秒十位計數器、分個位和分十位計數器、時個位和時十位計數器構成。數字鐘的計數電路的設計可以用反饋清零法,當計數器正常計數時反饋門不起作用,只有當進位脈沖到來時,反饋信號將計數電路清零,實現相應模的循環計數。

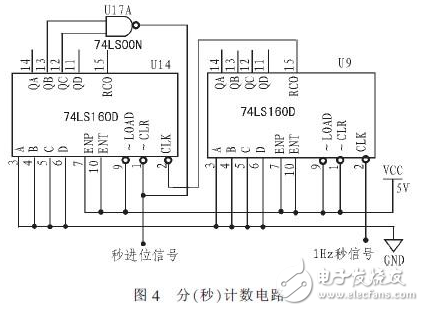

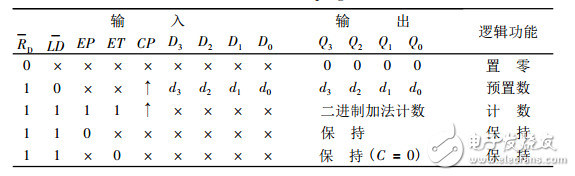

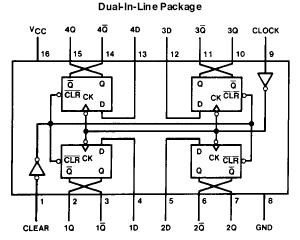

分(秒)計數器

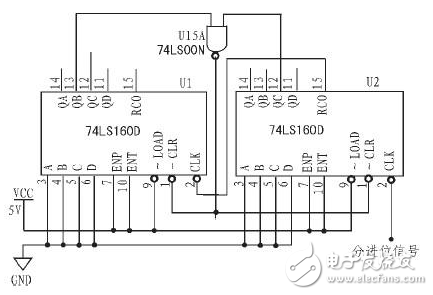

分(秒)計數器均為60進制計數,如圖4所示。它們的個位用十進制計數器74LS160構成,無需進制轉換,信號輸入端CLK與1Hz秒信號相連,進位輸出作為十位的計數輸入信號。十位采用反饋清零法將十進制計數器74LS160變成六進制計數器,因為清零端為低電平有效、所以將QB、QC與非后連接到清零端,即計數器的輸出狀態為“0110”時QB、QC輸出高電平與非后為低電平實現有效清零并對下一級進位。兩級電路組成一位60進制計數器,其計數規律為00→01→…→58→59→00.當秒計數滿60后向分個位提供一個進位信號,同理當分計數滿60后向時個位提供一個進位信號。

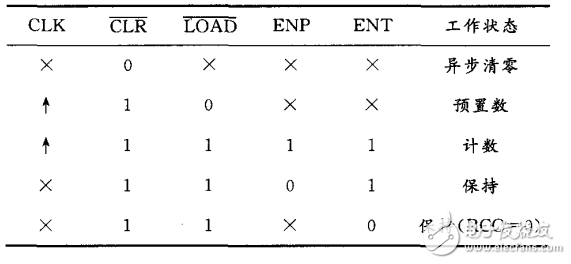

時計數器

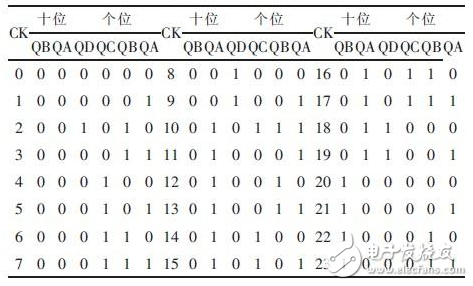

時計數器為24進制計數,其計數規律是00→01→…→23→00,即當數字運行到23時59分59秒時,在下一個秒脈沖的作用下,數字鐘顯示00時00分00秒。計數器的計數狀態轉換表如表1所示。

由表可知,計數器的狀態要發生兩次跳躍:一是計數到9,即個位計數器的狀態為1001后,在下一計數脈沖的作用下向十位計數器進位;二是計數到23后,在下一個計數脈沖的作用下,整個計數器歸零。

用兩片74LS160可實現24進制計數器的設計,如圖5所示。把時個位的QC與時十位的QB與非后送入到時個位和時十位的計數清零端,當時十位計數器的狀態為“0010”時個位計數器的狀態“0100”時,時個位的QC與時十位的QB輸出高電平,它們與非后為低電平分別對時個位和十位進行清零。

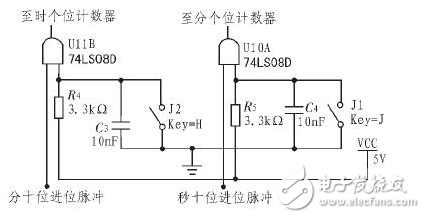

校時電路

校時是數字鐘應具備的基本功能,當數字鐘接通電源或者計時出現錯誤時都需要對時間進行校正。一般數字鐘都具有時、分、秒等校正功能。為使電路簡單,這里只進行分和時的校正。校正電路的要求在校正時位時不影響分和秒的正常計數,在校正分位時不影響秒和時的正常計數。校正電路的方式有快校正和慢校正兩種。由于快校正電路復雜,成本高,而慢校正更經濟一些,所以設計采用慢校正對時鐘進行校正,如圖6所示。慢校正是用手動產生單脈沖做校正脈沖。電路由74LS08及電阻、電容、開關等組成,其中J為校分開關,H為校時開關。

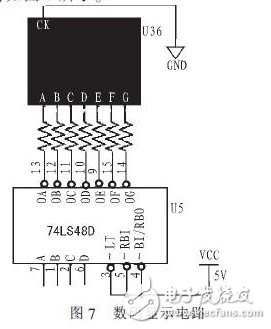

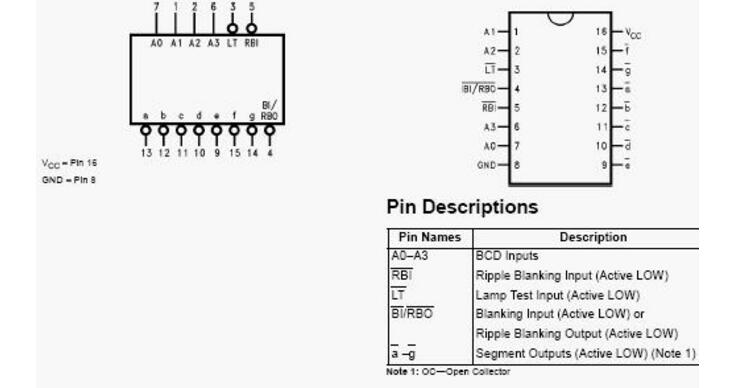

顯示部分

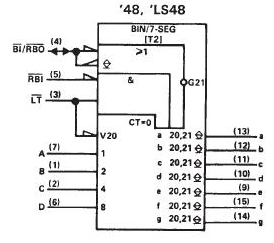

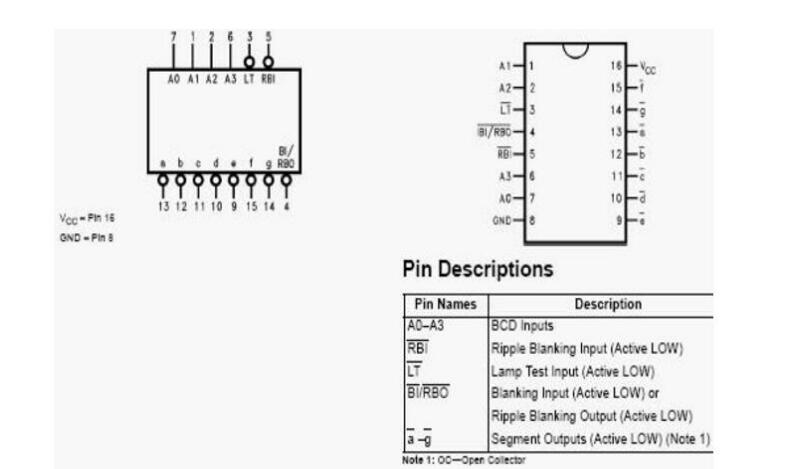

顯示部分采用74LS48來進行譯碼,用于驅動LED-7段共陰極數碼管。由74LS48和LED-7段共陰極數碼管組成數碼顯示電路,如圖7所示。

譯碼驅動電路是將“秒”、“分”、“時”計數器輸出的8421BCD碼進行編譯,轉換為數碼管需要的邏輯狀態,驅動LED-7段數碼管顯示,并且為保證數碼管正常工作提供足夠的工作電流。若將秒、分、時計數器的每位輸出分別與相應七段譯碼器的輸出端連接,在脈沖的作用下,便可進行不同的數字顯示。由于使用的譯碼器74LS48輸出端高電平有效,所以選擇共陰極的數碼管來與之搭配。

電子發燒友App

電子發燒友App

評論