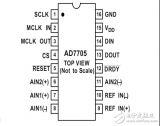

AD7705為完整16位低成本、Σ-Δ型ADC。采用SP IQ SPI兼容的三線串行接口,能夠方便地與各種微控制器和DSP連接,也比并行接口方式大大節(jié)省了CPU的 I O口。本文主要以ad7705應(yīng)用經(jīng)驗(yàn)及應(yīng)用所需注意的事項(xiàng)為中心而展開的討論。

ad7705應(yīng)用經(jīng)驗(yàn)總結(jié)

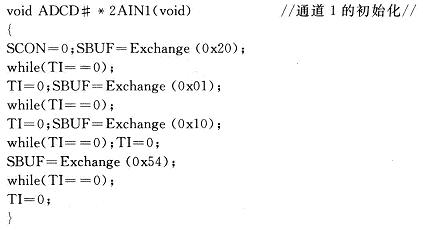

1.時(shí)序注意要點(diǎn):數(shù)字接口迷失的時(shí)候可以通過ADIN輸入持續(xù)32個(gè)脈沖周期(DCLK)以上的高電平將復(fù)位AD7705的數(shù)字接口,復(fù)位之后要等待500us以上才能訪問AD7705芯片,這種復(fù)位方式不會(huì)影響AD7705內(nèi)部的任何寄存器,所有的寄存器將保持復(fù)位之前的內(nèi)容,但所有的寄存器在數(shù)字接口迷失的狀態(tài)下內(nèi)容是不確定的,因此強(qiáng)烈建議在復(fù)位之后重新設(shè)置AD7705內(nèi)部所有的寄存器,防止錯(cuò)誤。而芯片管腳RESET的復(fù)位將使片內(nèi)所有的寄存器恢復(fù)到上電的默認(rèn)值。時(shí)鐘輸入信號(hào)DCLK是一種施密特出發(fā)信號(hào),能夠適應(yīng)光耦合器的慢速邊沿,其他數(shù)字輸入信號(hào)的上升和下降時(shí)間不應(yīng)超過1us。

2.AD7705時(shí)鐘大于2M時(shí),時(shí)鐘設(shè)置寄存器的CLK位應(yīng)置1,小于2M時(shí)應(yīng)置0。DCLK的脈沖寬度要滿足最小的脈寬要求。在時(shí)鐘DCLK下降之后的低電平期間讀取數(shù)據(jù)ADOUT。在時(shí)鐘DCLK的低電平期間設(shè)置要寫入數(shù)據(jù)ADIN,然后在DCLK的上升沿寫入到7705。寫入數(shù)據(jù)以及讀取數(shù)據(jù)的時(shí)鐘DCLK的數(shù)目要與(被寫入或被讀取的寄存器)的位數(shù)長度一致,多于或少于(寄存器位長度)的時(shí)鐘DCLK數(shù)目都將導(dǎo)致操作錯(cuò)誤。在兩次寫操作之間,ADIN應(yīng)最好保持在高電平:因?yàn)槿魏危ㄗx或?qū)懀┎僮鞫急仨殢膶?a href="http://www.1cnz.cn/v/tag/1301/" target="_blank">通信寄存器開始,而且寫入通信寄存器的8個(gè)位中的第1位必須為0,后續(xù)的位才能被寫入到通信寄存器。所以當(dāng)ADIN為0的時(shí)候,萬一時(shí)鐘DCLK受到干擾導(dǎo)致0寫入通信寄存器,AD7705會(huì)誤認(rèn)為是寫通信寄存器的操作開始而等待后續(xù)的7位位串,發(fā)生這種干擾之后會(huì)導(dǎo)致AD7705的數(shù)字接口迷失,從而導(dǎo)致內(nèi)部寄存器的內(nèi)容也許會(huì)變得未知狀態(tài)。此外,時(shí)鐘信號(hào)DCLK在兩次操作AD7705之間要保持高電平。即:在不訪問AD7705的空閑時(shí)刻,或者兩次操作之間的空閑時(shí)刻,ADIN、DCLK都最好保持高電平為最可靠。

3.DRDY信號(hào)為數(shù)據(jù)AD轉(zhuǎn)換完成的指示信號(hào),低電平期間表示AD轉(zhuǎn)換完成,可以讀取數(shù)據(jù)寄存器的內(nèi)容,高電平期間表示AD轉(zhuǎn)換正在進(jìn)行,這時(shí)不能訪問數(shù)據(jù)寄存器。對(duì)于系統(tǒng)校準(zhǔn)和內(nèi)部校準(zhǔn)也一樣,低電平期間表示校準(zhǔn)完成,可以讀取校準(zhǔn)寄存器的內(nèi)容,高電平期間表示校準(zhǔn)正在進(jìn)行,這時(shí)不能訪問校準(zhǔn)寄存器。違反這些規(guī)定的操作,結(jié)果時(shí)未知的。此外程序中千萬不能把DRDY的邏輯搞反,否則結(jié)果不可預(yù)料。

4.不管是校準(zhǔn)還是數(shù)據(jù)AD轉(zhuǎn)換,數(shù)字濾波器同步位FSYNC都要置為0,這樣AD7705的校準(zhǔn)或者數(shù)據(jù)AD轉(zhuǎn)換工作才能進(jìn)行,否則校準(zhǔn)和AD轉(zhuǎn)換不會(huì)進(jìn)行,DRDY信號(hào)也不會(huì)變低。當(dāng)FSYNC=0時(shí),在校準(zhǔn)或AD轉(zhuǎn)換結(jié)束后DRDY信號(hào)將變低,此時(shí)可以讀取校準(zhǔn)系數(shù)或者數(shù)據(jù)寄存器。

5.采用非緩沖模式時(shí),AD7705模擬輸入前端的電阻電容的變化對(duì)AD轉(zhuǎn)換精度影響很大。若系統(tǒng)工作時(shí)的信號(hào)源、溫度環(huán)境、器件參數(shù)變化很大,導(dǎo)致AD7705模擬輸入前端電路的參數(shù)跟系統(tǒng)校準(zhǔn)時(shí)的參數(shù)不一致,誤差會(huì)非常大。緩沖模式能解決這種問題,當(dāng)使能緩沖模式時(shí),AD7705會(huì)在模擬輸入端和AD轉(zhuǎn)換器之間接入一個(gè)緩沖器Buffer,這樣AD7705就能適應(yīng)模擬輸入前端信號(hào)源的大阻抗、器件參數(shù)(電阻電容)的變化、溫度環(huán)境的變化等各種與系統(tǒng)校準(zhǔn)時(shí)的不一致情況(即器件工作條件的變化)。所以,AD7705的校準(zhǔn)和正常工作最好都要在緩沖模式下進(jìn)行。

6.電壓輸入范圍:對(duì)于非緩沖模式,模擬輸入信號(hào)范圍是GND-30mV至VDD+30mV之間。對(duì)于緩沖模式,模擬輸入信號(hào)范圍是GND+50mV至VDD-1.5V之間。

7.非緩沖模式、單極性、增益為GAIN:此時(shí)AD7705的反相輸入端VIN-的范圍是GND-30mV至VDD+30mV-VREF/GAIN之間,其中VREF為AD7705的參考電壓。正相輸入端VIN+的范圍是V-至V-+VREF/GAIN。如右圖,即V+和V-都必須大于GND小于VDD,同時(shí)還要考慮單極性的輸入范圍,即V-還必須小于VDD+30mV-VREF/GAIN,才不至于模擬輸入為V+max=V-+VREF/GAIN時(shí)大于VDD+30mV。

8.非緩沖、雙極性、增益為GAIN:此時(shí)V+和V-都必須大于GAN小于VDD,V-還必須小于VDD+30V-VREF/GAIN,這樣輸入V+max=V-+VREF/GAIN不至于大于VDD+30mV。V-還必須大于GND-30mV +VREF/GAIN,才不至于輸入V+min=V――VREF/GAIN時(shí)小于GND-30mV。正相輸入端VIN+的正信號(hào)輸入范圍是V-至V-+VREF/GAIN,正相輸入端VIN+的負(fù)信號(hào)輸入范圍是V-至V--REF/GAIN。

9.緩沖模式、單極性、增益為GAIN:此時(shí)AD7705的反相輸入端VIN-的范圍是【GND+50mV】至【VDD-1.5V-VREF/GAIN】之間,其中VREF為AD7705的參考電壓。正相輸入端VIN+的范圍是【V-】至【V-+VREF/GAIN】。如右圖,即V+和V-都必須大于GND+50mV小于VDD-1.5V,同時(shí)還要考慮單極性的輸入范圍,即V-還必須小于VDD-1.5V-VREF/GAIN,才不至于輸入V+max=【V-+VREF/GAIN】時(shí)大于VDD-1.5V。

10.緩沖模式、雙極性、增益為GAIN:此時(shí)AD7705的反相輸入端VIN-的范圍是【GND+50mV+VREF/GAIN】至【VDD-1.5V-VREF/GAIN】之間,這樣才不至于輸入VIN+max=【V-+VREF/GAIN】時(shí)導(dǎo)致VIN+大于VDD-1.5V、輸入VIN+min=【V――VREF/GAIN】時(shí)導(dǎo)致VIN+小于GND+50mV。其中VREF為AD7705的參考電壓。正相輸入端VIN+的正信號(hào)輸入范圍是【V-】至【V-+VREF/GAIN】,正相輸入端VIN+的負(fù)信號(hào)輸入范圍是【V-】至【V--REF/GAIN】。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論