您的位置:電子發(fā)燒友網(wǎng) > 電子技術(shù)應(yīng)用 > 嵌入式技術(shù) > 嵌入式設(shè)計應(yīng)用 >

SOC中多片嵌入式SRAM的DFT實(shí)現(xiàn)方法

2011年12月15日 10:25 來源:本站整理 作者:葉子 我要評論(0)

本文基于MBIST的一般測試方法來對多片SRAM的可測試設(shè)計進(jìn)行優(yōu)化,提出了一種通過一個MBIST控制邏輯來實(shí)現(xiàn)多片SRAM的MBIST測試的優(yōu)化方法。

1 MBIST介紹

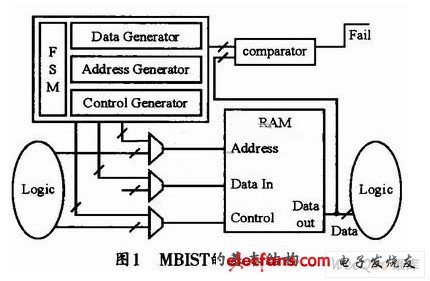

MBIST意即存儲器內(nèi)建自測試(Memory Build In Self Test),是目前業(yè)界用來測試存儲器的一種常見方法,其原理是通過多次反復(fù)讀寫SRAM來確定其是否存在制造中的缺陷。MBIST的EDA工具可針對內(nèi)嵌存儲器自動創(chuàng)建BIST邏輯,它支持多種測試算法的自動實(shí)現(xiàn)(常用算法為March C+),并可完成BIST邏輯與存儲器的連接。此外,MBIST結(jié)構(gòu)中還可包括故障自動診斷功能,方便故障定位和特定測試向量的開發(fā)。MB-IST的基本結(jié)構(gòu)如圖1所示。

整個SRAM和MBIST控制邏輯構(gòu)成的整體只是在原有SRAM端口的基礎(chǔ)上增加了復(fù)位信號rst_n和bist_start信號(為高表示開始測試)兩個輸入信號,同時增加了test_dONe(為高表示測試完成)、fail_h(為高表示出現(xiàn)故障)、addr_er(fail_h為高時輸出的故障地址有效)等三個輸出信號。

2 多片SRAM的MBIST測試結(jié)構(gòu)

基于SMIC 0.13um工藝的OSD (On Screen Display)顯示芯片需嵌入地址位寬為8-bit、數(shù)據(jù)位寬為512-bit。即大小為256x512bit的SRAM來存儲大量的客戶定制字符。由于Artisan的SPSRAM Generator支持的SRAM模型的最大數(shù)據(jù)位寬為64 bit,故可通過8片大小為256×64 bit的SRAM來實(shí)現(xiàn)。

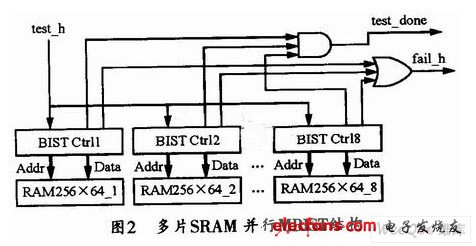

利用Mentor公司的MBIST Architect選取March3算法可產(chǎn)生兩種MBIST結(jié)構(gòu)。其一為每片256x64 bit的SRAM各生成一套MBIST邏輯,以構(gòu)建MBIST并行結(jié)構(gòu),圖2所示為其并行結(jié)構(gòu)示意圖。該方法可對所有MBIST的test_done(完成標(biāo)志)進(jìn)行“與”操作,以保證所有SRAM都測試結(jié)束;fail_h(失效標(biāo)志)可進(jìn)行“或”操作來實(shí)現(xiàn)(高有效),只要有一個SRAM出現(xiàn)故障即停止測試,否則表明所有SRAM測試都通過。

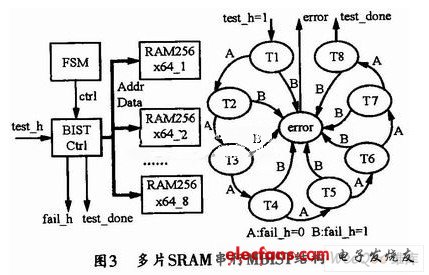

第二種方法是針對256×64bit大小的SRAM只生成一套MBIST,然后通過附加的狀態(tài)機(jī)和數(shù)字邏輯來對多片SRAM逐一進(jìn)行測試,即構(gòu)建如圖3所示的MBIST串行結(jié)構(gòu)。當(dāng)所測的某一個SRAM出現(xiàn)故障即停止測試,若所有SRAM測試結(jié)束都未有error信號輸出,則表明所有SRAM測試均通過。

本文導(dǎo)航

- 第 1 頁:SOC中多片嵌入式SRAM的DFT實(shí)現(xiàn)方法(1)

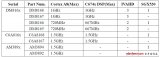

- 第 2 頁:結(jié)果比較