對于設計人員而言,根據應用的效能、電源、記憶體及介面等需求,尋找特定的嵌入式處理器,不是件容易的事,即便是相似的系統也存在顯著的差異。儘管ARM處理器提供十多種選擇,系統設計人員仍然很難找到完美搭配的解決方案。

本文將重點介紹各種標準介面,并說明不同嵌入式晶片廠商的差異。瞭解基本介面有助于設計人員優先考量,哪些介面應該整合于晶片。雖然標準介面具有很高的使用價值,但為提供額外的單晶片資源,也需要可客製化的單晶片介面,本文將介紹此兩種周邊區塊。

通用序列匯流排(USB)介面最初的開發目的,是用以連接個人電腦與周邊。隨著時間推移,已經成為工業與基礎架構應用的常用介面。鍵盤、滑鼠及示波器等人機介面設備(HID),通常採用USB介面,這表示必須獲得系統嵌入式處理器的支援。實現此一目標的最有效方法,是採用單晶片周邊。

除了HID之外,工業與基礎架構應用也可使用另外兩種裝置類別。USB通訊裝置類(CDC)不但適用于數據機與傳真機,也透過提供用于乙太網路封包傳輸的介面,來支援簡單的網路功能。同樣地,USB大量儲存裝置(MSD)主要針對硬碟驅動器及其他儲存媒體。

USB 2.0規格需要主機進行所有入埠及出埠的傳輸。此規格也定義叁種基本裝置:主機控制器、集線器及周邊。

USB 2.0的實體互連,是在各個星型配置使用一個集線器的分層星型拓樸。各個線段都是一個主機與集線器或功能之間的點對點連接,或連接至其他集線器與其他功能的集線器。

USB 2.0系統中,用于裝置的定址機制,可供單一主機連接多達127個裝置,可以是集線器或周邊的任何組合。復合或組合裝置可以是選自于其中兩個或兩個以上的裝置。

雖然USB 2.0很可能是工業和許多基礎架構應用的首選,但周邊裝置在不使用主機的情況下相互通訊時,仍需要部署USB On-the-Go(OTG)。為了實作點對點通訊,USB OTG 引入一種新的裝置,這種裝置包含使兩個周邊共享資料的有限主機功能。

OTG 補充定義主機協商通訊協定(HNP)的新交握方式(handshake)。使用HNP,能夠預設周邊進行連接的裝置,并請求成為主機,為現有USB 2.0主機裝置範例提供點對點通訊。另外也定義階段作業要求通訊協定(SRP)。

USB標準的普及與穩定的狀態,嵌入式處理器廠商皆針對特定USB功能提供軟體程式庫,大幅縮短開發時間。系統設計人員不需要自行撰寫程式碼,只需要執行函式唿叫 (function call)即可進行介面操作。

這些程式庫需通過認證,證明已通過USB設計論壇USB裝置及嵌入式主機規範測試。德州儀器(TI)等多家廠商,皆為自家嵌入式處理器提供廣泛的USB程式庫。

2007年,高速USB推廣團隊成立,這種USB類型不僅向下相容以前的USB標準,而且資料速率比USB 2.0快10倍。USB 3.0採用新的訊號處理機制,并透過保留USB 2.0雙線式介面,達到向下相容的效果。

EMAC

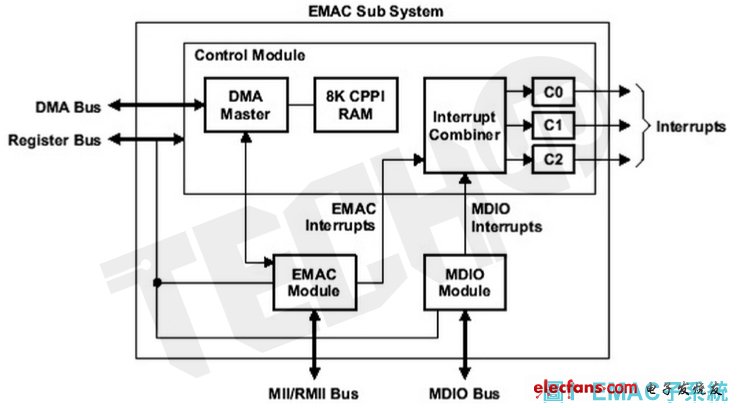

符合IEEE 802.3乙太網路標準的介面,一般會被誤認為乙太網路媒體存取控制器(EMAC),但完整的EMAC子系統介面實際上包括叁個區塊,這叁個區塊可能已整合或未整合于晶片:實體層介面(PHY)、2.乙太網路MAC,這可實作通訊協定的EMAC層、3.一般稱為MAC控制模組的自訂介面。

EMAC模組可控制從系統到PHY的封包資料流。MDIO模組可執行PHY的配置以及狀態監控。這兩個模組均可透過MAC控制模組存取系統核心,并且優化資料流。在TI嵌入式處理器等完全整合式解決方案中,自訂介面被視為EMAC/MDIO周邊不可或缺的組成部分。

完整的EMAC子系統如圖1所示。

EMAC控制模組不僅可控制裝置中斷,也整合一個8K位元組內部隨機存取記憶體(RAM),用以存留EMAC緩衝區描述元。MDIO模組採用802.3序列管理介面,來檢視和控制多達32個共用雙線式匯流排連接至裝置的乙太網路PHY。

主機軟體使用MDIO模組,來配置連接至EMAC的各個PHY的自動協商參數、擷取協商結果,并在EMAC模組中配置所需的參數,以進行正確的操作。此模組可使得MDIO介面達到幾乎透明的操作,不需要核心處理器的維護。

EMAC模組可在網路與處理器之間提供高效率的介面。EMAC模組通常可提供10Base-T(10Mbps)與100BaseTX(100Mbps)、半雙工與全雙工模式,以及硬體流控制與服務品質(QoS)支援。部份處理器現在也支援高達1000Mbps資料速率的GB EMAC容量。

由于乙太網路受到廣泛運用,嵌入式處理器一般都在單晶片整合一個或多個EMAC介面。不同的廠商在實作上述完整的EMAC子系統時,採用的方法各有不同。實作乙太網路介面時,所需軟體支援與程式庫的品質和範圍,是選擇嵌入式處理器廠商必須考量的另一個問題。

路由器或交換機等應用,所需的EMAC有時不止一個。這些應用能夠透過多個EMAC進行同步通訊,同時與多個裝置通訊。

序列ATA(SATA)可將主機匯流排轉接器,與硬碟機與光碟機等大量儲存裝置連接。這個規格已經幾乎取代之前的平行ATA(PATA)。PATA需要長度不超過18英吋的40/80線平行纜線。PATA的最大資料傳輸率為133MBps,而SATA序列資料格式,則使用兩個差動支援連接資料儲存裝置的介面,線路速率為1.5Gbps(SATA版本1)、3.0Gbps(SATA版本2)與6.0Gbps(SATA版本3)。SATA 1和SATA 2現已問世,SATA 3將在不久的將來推出。

SATA控制器需要的纜線較細,而且長達3英呎。細纜線的靈活度較高,一方面可達到更簡便的佈線,另一方面更有利于大量儲存裝置機殼內部的空氣流通。

序列連結可達到高效能的部份塬因,是採用進階系統記憶體結構,來儲存高速序列資料。這種進階主機控制器介面(AHCI)記憶體結構,可為控制、狀態及命令清單資料表提供通用區域。命令清單的每筆記錄均包含SATA裝置程式設計的資訊,以及在系統記憶體與裝置之間傳輸資料的描述符表(discriptor table)。

大多數SATA控制器均支援熱抽換(hot swapping),也採用連接埠倍增器(port multiplier),來增加可連接至單一HBA連接埠的裝置數量。SATA標準支援許多功能,但少有SATA控制器支援所有功能。較為常見功能包括:

? 支援AHCI控制器規格1.1版

? 整合SERDES PHY

? 整合接收與傳輸資料緩衝區

? 支援SATA電源管理功能

? 各連接埠內部?DMA引擎

? 多達32筆記錄的硬體輔助塬生命令佇列(NCQ)

? 32位元定址

? 支援連接埠倍增器

? 支援活動LED

? 機械控制開關

由于SATA能夠儲存高達兆位元(terabyte)範圍的大量資料,因此應用相當廣泛,其中包括小筆電、筆記型電腦、桌上型電腦、多媒體裝置及可攜式資料終端等。此外,SATA也可用于需要感測器或系統監控器儲存大量資料,以供后續分析的工業應用。

DDR2/行動DDR

DDR2是雙倍資料速率(DDR)SDRAM規格的后繼標準,這兩個標準并不相容。DDR2在匯流排時脈訊號的上升與下降邊緣傳輸資料,并以更高的匯流排速度運作,再進行各個內部時脈週期四次的資料傳輸。

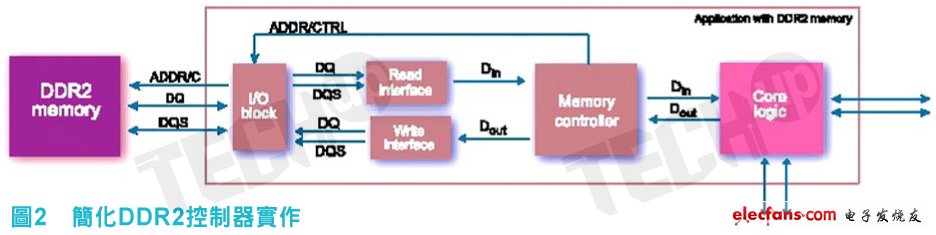

簡化型DDR2控制器包括以下設計區塊:

? 記憶體控制

? 讀取介面

? 寫入介面

? I/O區塊

???????

???????

這些區塊及其與DDR2記憶體晶片和核心邏輯的關係如圖2所示。

記憶體控制區塊從記憶體存取應用特定核心邏輯,或從應用特定核心邏輯存取記憶體。讀取實體區塊負責處理在各個讀取週期中,擷取資料的外部訊號時序,而寫入實體區塊,則使用適當的外部訊號時序來管理時脈與資料的發出。

位元組寬雙向資料回應(DQS)隨資料(DQ)透過對外傳輸,用以進行擷取。DQS在讀取記憶體時,由控制器透過邊緣對齊的方式傳輸,在寫入記憶體時,則採取中央對齊的方式。單晶片延遲鎖相迴路(DLL),用以鎖定DQS及對應的DQ。可在電壓及溫度發生變化時確保能夠相互追蹤。

DDR2 SRAM具有差動時脈輸入,可降低時脈輸入負載週期變化所造成的影響。DDR2 SRAM也支援資料遮罩訊號(data mask signal),可在各個寫入週期中為資料位元加入遮罩。

行動DDR(MDDR)也稱低功耗雙倍資料傳輸率記憶體(LPDDR),傳統記憶體運作電壓為2.5V或3.3V,而其運作電壓為1.8V,通常用于可攜式電子產品。行動DDR記憶體也支援傳統DDR2記憶體不具備的低功耗狀態。與所有DDR記憶體一樣,雙倍資料傳輸率是透過裝置時脈上下邊緣同時傳輸資料而達成。

uPP

由于單晶片周邊的數量受成本或其他限制條件約束,系統設計人員通常尋求將資料傳入與傳出晶片的新方法。其中一種是利用未使用的視訊連接埠資源,高速收發非視訊資料。這種方法的其中一個缺點是資料必須轉為視訊格式(video frame),在運作中需要部份處理器MIPS的支援,而在設計週期中則需要佔用寶貴的程式設計時間。

其他的方法存在類似的困難,而且大多數標準單晶片資料介面都是序列連接埠,無法執行高速傳輸。

因此,許多系統設計人員認識到,將不符合特定介面標準但能夠以多種方式配置的彈性高速周邊專用于資料傳輸,可達到顯著的優勢。如果系統處理器必須與高速DAC、ADC、DSP及FPGA連接而達到250MBps的高速資料傳輸,則此類知識就相當有助益。

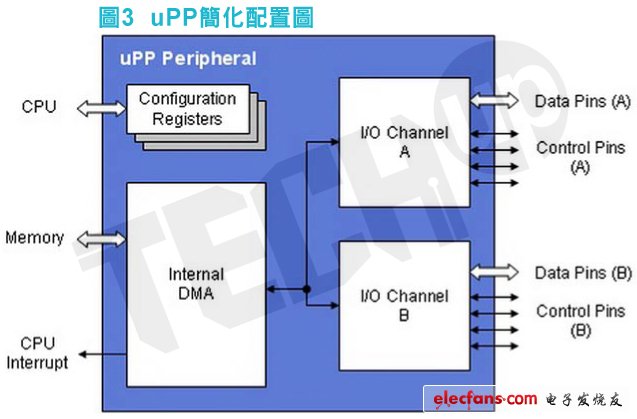

這種周邊的基本架構很簡單,具有許多個別平行匯流排的通道,經過配置可容納超過一個字元長度(word length)以上。其中也有內部DMA區塊,其運作不需要佔用核心的 MIPS。單倍或雙倍資料速率以及多種資料封包格式也適用。

TI各種嵌入式處理器均提供通用平行連接埠(uPP),包括Sitara ARM9 AM1808與AM1806微處理器(MPU),以及包含TMS320C674x核心與ARM9核心的OMAP-L138處理器。與SPI及UART等序列周邊不同,uPP可為設計人員提供平行資料匯流排的優勢,各通道資料寬度為8位元及16位元。

uPP在以75MHz的最高時脈速率運作時,能以遠遠高于序列連接埠周邊的速度傳輸資料。例如,以75MHz速率運作的單一16位元uPP通道,比以50MHz速率運作的SPI周邊快24倍。圖3顯示簡化的配置圖。

uPP最重要的功能包括:

?具有個別資料匯流排的兩個獨立通道:通道可同時以相同或相反方向運作

?I/O速度高達75MHz,各通道資料寬度為8至16位元

?內部DMA-可釋放CPU EDMA

?具有極少控制接腳的簡單通訊協定(可配置:各通道2至4個)

?單倍及雙倍資料速率(使用時脈訊號的單邊或兩邊):雙倍資料速率需要37.5MHz的最高時脈速率

?支援9至15位元資料寬度的多種資料封包格式

?資料交錯模式(限單通道)

uPP與另一種專用于可配置資料處理的TI周邊「主機連接埠介面」(HPI)有某些相似處。HPI是一種可供外部主機直接存取處理器內部記憶體的平行介面。然而,不同于HPI,uPP不允許外部裝置直接存取記憶體,而需要裝置軟體對I/O傳輸進行佇列。最大的差異在于uPP比HPI更快速,而且通訊協定也更簡單。

uPP主要用于FPGA或DSP等需要晶片外即時處理的應用,能夠為醫療領域等立即需要資料的市場帶來極大的優勢。透過uPP,決策處理器能夠運用最新資訊做出結論。

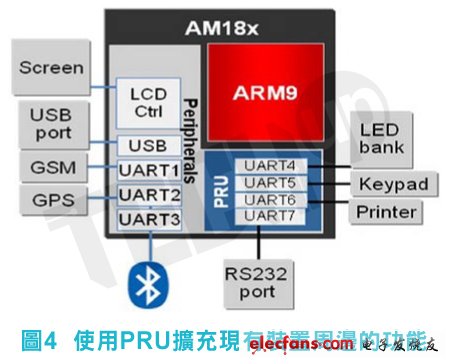

PRU

可程式即時單元(PRU)是一種小型32位元處理引擎,可為單晶片即時處理提供更多的資源。PRU專門用于AM1x MPU與OMPAP-L138解決方案中的TI嵌入式處理器,能為系統設計人員提供具有高彈性的額外措施,可降低元件成本。

PRU的四匯流排架構,隨著資料傳輸同步提取和執行指令。此外也提供輸入暫存器,讓外部狀態資訊反映在內部處理器的狀態暫存器內。

PRU設計的其中一個重要目的,就是儘可能達到彈性,以便執行各種功能。PRU的高彈性有助于開發人員在終端產品(無論是觸控螢幕、整合式顯示器或儲存功能)中整合更多的介面,進一步擴展產品功能或其本身專屬介面的功能。此目標主要是透過提供包括所有系統記憶體、I/O及中斷在內的PRU全面系統能見度而達成。

雖然PRU能夠全面存取系統資源,但內部資源相對而言屬于中等程度,PRU具有4KB的指令記憶體和512位元組的資料記憶體,具有本身的GPIO,延遲僅為數奈秒(nanosecond)。

PRU可透過使用簡單組合語言程式碼的程式設計來實作自訂邏輯。此指令集分為四大類:

?將資料移入或移出處理器內部暫存器

?執行演算運算

?執行邏輯運算

?控制程序流程

在工業應用中,通常將PRU配置為I/O區塊,用以補足處理器未提供的I/O。例如,在需要UART區塊組合的可攜式資料終端中,以連接GSM、GPS與Bluetooth、鍵盤、印表機、LED排燈及RS232連接埠。雖然此處理器系列中的最佳選擇僅整合叁個UART,不過PRU可提供更多的UART介面,充分滿足不斷發展的終端裝置對于處理各種功能的需求。

除了補足I/O之外,PRU經過程式設計之后也可執行各種控制、監控或其他單晶片未提供的功能。對于本身的控制需求與標準處理器配置的控制需求不相同的應用而言,如此的彈性特別有助益。

ARM子系統與周邊整合

在評估ARM處理器的周邊介面時,了解周邊與ARM子系統整合方式相當重要。

ARM處理器適合復雜多工的一般用途控制,不僅為大型程式提供記憶體空間,而且也具有良好的環境切換功能,這適合用于運作即時作業系統(RTOS)及精密的高階作業系統。ARM負責系統配置與控制,包括周邊配置與控制、時脈控制、記憶體初始化、中斷處理及電源管理等。ARM子系統包含ARM處理器,以及ARM處理器,進行整體處理器系統主控制器功能所需的其他元件。

一般ARM子系統包括下列元件組合:

?ARM核心(例如:ARM926EJ-S或ARM Cortex-A8)-協同處理器15(CP15)、MMU、寫入緩衝器、指令快取、資料快取、Java加速器、Neon單一指令多重資料(SIMD)協同處理器、向量浮點協同處理器(VFP)

?ARM內部記憶體-RAM、ROM(ARM開機載入器)

?匯流排仲裁器(bus arbiter)-用以存取內部記憶體的匯流排仲裁器、用以存取系統及周邊控制暫存器的匯流排仲裁器、用以存取外部記憶體的匯流排仲裁器

?除錯、追蹤及模擬模組-JTAG、ICECrusher、嵌入式追蹤巨集單元(ETM)

?系統控制周邊-ARM中斷控制模組、PLL(鎖相迴路)及時脈控制模組、電源管理模組、系統控制模組

圖 5 ARM 子系統配置圖

對于 USB、EMAC、SATA、uPP 及 PRU 等周邊而言,ARM 子系統可存取周邊的控制與配置暫存器、時脈及電源管理控制。

結論

雖然標準介面在設計系統的過程中發揮重要的作用,能夠達到互通性與低成本,并減少設計時間,但是對于需要達到產品差異化的設計團隊而言,實用性較為有限。設計人員也尋求晶片廠商提供各種多重組合的標準介面。對于晶片廠商而言,有助于有效實作介面的高品質軟體程式庫,是達到差異化的重要因素。提供更高的彈性也相當有助益,只要透過 TI PRU 與 uPP 等可配置介面即可達成。系統設計人員利用工具套件中的這些選項,即可發揮創意,并且維持元件的低成本。

電子發燒友App

電子發燒友App

評論