編譯碼的原理是什么?如何對編譯碼算法進行仿真測試?

2021-04-28 06:54:22

BCD碼的硬件實現,采用左移加3的算法,具體描述如下:(此處以8-bit 二進制碼為例) 1、左移要轉換的二進制碼1位2、左移之后,BCD碼分別置于百位、十位、個位3、如果移位后所在的BCD碼列大于或

2017-05-11 16:21:02

一、G.711音頻協議二、G.722.1音頻協議三、G.722.2音頻協議四、G.723.1音頻協議五、G.726音頻協議六、G.729音頻協議

2021-12-24 06:31:19

我最近在學習用matalb生成dsp6748使用的算法,按照創龍給的資料中使用 這篇pdf的做法,前面幾步都沒有問題,在最后一步編譯的時候報錯如下:想請問下創龍工程師,這個interface文件夾下的程序是什么功能,還有就是這樣的報錯應該怎么解決?

2020-03-26 11:21:21

本帖最后由 mr.pengyongche 于 2013-4-30 03:24 編輯

[共享] 基于DSP的電壓補償算法及實現 from hellodsp[url=www.7773.cc]

2011-08-23 18:20:53

的不足,同時也方便在現場可編程門陣列(FPGA)中增加一些其他相關的應用功能,因此在FPGA中實現CVSD語音編譯碼調制功能的前景將是非常廣闊的。這里將詳細介紹什么是CVSD?其算法分析如何在FPGA中實現?

2019-08-07 07:04:27

什么是Turbo碼的迭代譯碼算法?Turbo 碼獲得優異性能的第二個重要因素是應用了基于最大后驗概率準則 (MAP) 的迭代譯碼算法。當前Turbo譯碼算法有哪些?(1) 標準算法(MAP)它對

2008-05-30 16:24:49

Viterbi 譯碼算法可以簡單概括為“相加-比較-保留”,譯碼器運行是前向的、無反饋的,實現過程并不復雜。我們來分析Viterbi 算法的復雜度: (n, k, N) 卷積碼的狀態數為 條幸存

2008-05-30 16:11:37

使用dsp c5517 實現viterbi (2,1,7)譯碼?譯碼的波特率是115200bps,有誰會的,可以私聊,有償的。

2017-05-02 16:20:09

本帖最后由 mr.pengyongche 于 2013-4-30 02:23 編輯

基于DSP的FFT算法實現[url=www.6668.cc]

2012-08-17 13:56:25

由于卷積碼優良的性能,被廣泛應用于深空通信、衛星通信和2G、3G移動通信中。卷積碼有三種譯碼方法:門限譯碼、概率譯碼和Viterbi算法,其中Viterbi算法是一種基于網格圖的最大似然譯碼算法,是卷積碼的最佳譯碼方式,具有效率高、速度快等優點。

2019-11-01 08:05:38

【摘要】:Viterbi譯碼器在通信系統中應用非常普遍,針對采用DSP只能進行相對較低速率的Vit-erbi譯碼的問題,人們開始采用FPGA實現高速率Viterbi譯碼。本文首先簡單描述了

2010-04-26 16:08:39

本文將討論其中的前兩項:具體地說,首ff先是介紹如何實現OFDMA的核心DSP算法,然后是被LTE用來實現上行鏈路的新技術,最后簡要介紹用于WiMAX和LTE的MIMO(所有IP方面的內容不在本文討論范圍內)。本文討論的前提條件是采用軟件定義的架構。

2021-06-01 06:49:13

一種在FPGA中實現的基于軟判決的Viterbi譯碼算法,并以一個(2,1,2)、回溯深度為10的軟判決Viterbi譯碼算法為例驗證該算法,在Xilinx的XC3S500E芯片上實現了該譯碼器,最后對其性能做了分析。 關鍵詞: OFDM;Viterbi譯碼;軟判決;FPGA

2009-09-19 09:41:24

本文研究了RS碼的實現方法,并基于Xilinx的FPGA芯片Spartan-6 XC6SLX45完成了RS編譯碼器的設計,同時對其進行了仿真和在線調試,并給出了功能仿真圖和測試結果。時序仿真結果表明,該編譯碼器能實現預期功能。

2021-06-21 06:23:53

。Turbo碼現已成為深空通信的標準,即第三代移動通信(3G)信道編碼方案[2]。Turbo碼雖然具有優異的譯碼性能,但是由于其譯碼復雜度高,譯碼延時大等問題,嚴重制約了Turbo碼在高速通信系統中的應用。因此,如何設計一個簡單有效的譯碼器是目前Turbo碼實用化研究的重點。

2019-08-22 07:28:46

本文介紹了基于FPGA的CVSD語音編譯碼的設計思路、具體實現以及和專用芯片CMX639之間的互相通信。

2021-04-30 06:32:01

截短Reed-Solomon碼譯碼器的FPGA實現提出了一種改進的BM算法,并在此基礎上提出了一種大量采用并行結構的截短RS碼譯碼器的實現方式。驗證表明,該算法能顯著提高基于FPGA的RS譯碼

2009-09-19 09:39:43

我是初學者,我需要用DSP做一個G代碼編譯器。需要實現的功能是輸入一行G代碼,一個個將它讀入、分析。求大神們幫幫幫。謝謝了。

2014-05-27 12:22:35

Turbo碼編碼器的FPGA實現Turbo碼譯碼器的FPGA實現Turbo碼編譯碼器的性能有哪些?

2021-05-07 06:06:23

不規則重復累計碼BP譯碼算法具有接近Shannon限優越性能,但具有較高的復雜度。為了降低復雜度,提出了IRA碼最小和算法和曲線折線化算法。最小和算法具有簡單、容易實現的特

2008-11-20 12:12:20 9

9 在DSP 上移植算法,代碼優化程度成為提高系統性能、縮短開發周期的瓶頸。同時針對復雜算法在DSP 上的實現, 也產生很多優化策略、方法。本文以在數字通信系統中應用廣泛的Viter

2009-04-15 11:15:44 18

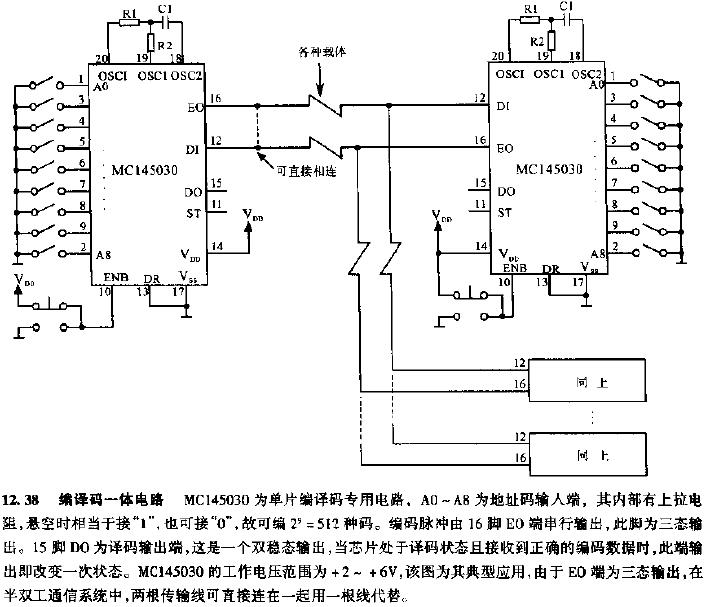

18 簡易編譯碼電路圖

2009-05-19 10:47:26 9

9 面向IEEE 802.16e 中 LDPC 碼,分析了各種譯碼算法的譯碼性能,歸一化最小(NMS)算法具備較高譯碼性能和實現復雜度低的特點。提出一種基于部分并行方式的LDPC 譯碼器結構,可以滿

2009-08-05 08:46:59 24

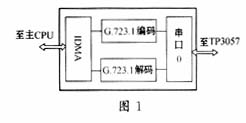

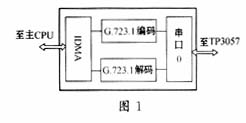

24 本文首先闡述了G.723.1語音編解碼標準的流程。根據低功耗、高性能的16位定點的數字信號處理芯片TMS320DM642的特點對源代碼中運算量較大的模塊進行了代碼優化。最后,在DSP硬

2009-08-10 10:00:11 31

31 RS 碼以其強大的糾正隨機錯誤和突發錯誤的能力,被廣泛地應用于各種數字通信系統中,本文首先敘述了RS 碼譯碼的基本原理,給出了實現RS 碼軟判決譯碼的方法和用DSP 實現譯碼的

2009-08-19 10:26:07 22

22 基于可靠性更新的低復雜度B譯碼算法:基于部分符號更新策略的BP (Belief Propagation)譯碼算法減少了LDPC (Low-Density Parity-Check)碼的譯碼運算量,提高了譯碼效率。然而在其譯碼過程中,由

2009-10-29 13:09:21 16

16 3G測試系統中的Viterbi譯碼及其DSP實現及優化

摘要 介紹了一種用于測試TD-SCDMA手機終端測試平臺中的關鍵技術——Viterbi譯碼。研究用約束度K=9的卷積編碼和最大似然Viterbi譯

2009-11-13 18:51:25 18

18 該文從譯碼速率、硬件實現的復雜度和誤碼率3 個方面對比研究了兩種典型的高速譯碼算法:Turbo 型和積算法與并行加權比特翻轉算法。以準循環LDPC 碼為對象,給出了Turbo 型和積算

2009-11-25 15:26:58 9

9 Turbo 碼的工程應用與實現是近年來研究工作的熱點。Turbo 碼采用反饋迭代譯碼結構,成員譯碼器使用最大后驗概率(MAP)譯碼算法譯碼,由于MAP 算法含有大量的指數運算與對數運算,

2009-11-27 15:15:31 7

7 ITU-T G.723.1 是一種用于多媒體通信的雙碼率語音編碼標準。本文在簡單介紹其編解碼算法和浮點數字信號處理器TMS320C6713 之后,著重介紹了該編解碼算法在TMS320C6713 DSK 上的軟件和硬

2009-11-27 15:31:23 10

10 本文利用可編程邏輯的靈活性和Nios 的強大處理能力,將多種編譯碼模塊和微處理器模塊集成到一片FPGA 內部,方便地實現了通用編譯碼器的設計。由于采用了VHDL 語言,使系統具有可移

2009-11-30 14:27:56 22

22 在ITU-T 的G.723.1 語音編解碼算法基礎上,本文詳細介紹了該算法在定點 C 語言程序和全匯編程序實現時的關鍵技術和優化策略,使優化后的 G.723.1 編碼器在內存占用率和運算復雜

2009-12-18 14:40:37 9

9 介紹了 TI 的TMS320C6416 DSP 片上Viterbi 譯碼協處理器(VCP)的結構與原理。給出了一種使用鏈式EDMA 結構和“乒乓”緩沖技術提高VCP 譯碼過程并行性的方法。設計出基于MATLAB 的Link for

2009-12-23 15:19:48 19

19 文章分析了Turbo 碼的MAP 類譯碼算法后,針對傳統Log—MAP 譯碼算法的特性,提出了一種改進的Log—MAP 譯碼算法。仿真結果表明,新的算法在降低譯碼復雜度的同時較好地保持了譯

2010-01-15 11:51:47 13

13 數字光纖通信系統的原理框圖如圖1所示(其中調制器與解調器包括電光轉換與光電轉換功能),我們所做的工作是設計信道編譯碼部分的電路,在通信系統中所處的位置如圖中虛線

2010-04-20 22:33:12 83

83 IRA碼的譯碼通常是利用BP譯碼算法來實現的,但是BP譯碼算法的硬件電路復雜。為了讓譯碼算法在復雜度和譯碼性能之間取得較好的折衷,提出一種改進型IRA譯碼算法,該算法采用偏

2010-07-05 16:23:56 21

21 基于TMS320C6416高性能通用DSP,實現了對AWGN信道的信噪比(SNR)估計,并以此估計值設計了一種低密度奇偶校驗(LDPC)碼的譯碼系統;詳盡介紹了集成SNR估計的譯碼系統的實現方案和流程;仿真

2010-07-27 16:28:32 11

11 針對固定碼長Turbo碼適應性差的缺點,以LTE為應用背景,提出了一種幀長可配置的Turbo編譯碼器的FPGA實現方案。該設計可以依據具體的信道環境和速率要求調節信息幀長,平衡譯碼性

2010-11-11 16:07:59 26

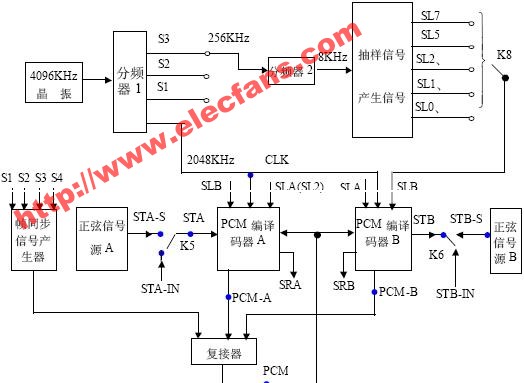

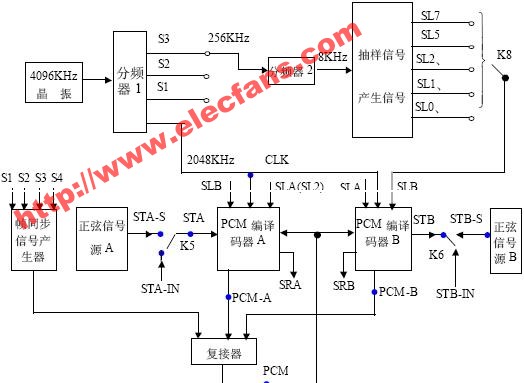

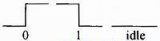

26 PCM編譯碼模塊原理

本模塊的原理方框圖圖5-2所示,模塊內部使用+5V和-5V電壓,其中-5V電壓由-12V電源經7905變換得到。

2008-10-21 13:31:10 7114

7114

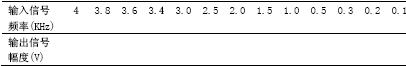

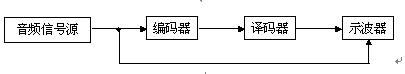

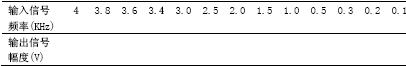

PCM編譯碼實驗

一、實驗目的1. 掌握PCM編譯碼

2008-10-21 13:35:45 8339

8339

基于BIST的編譯碼器IP核測

隨著半導體工藝的發展,片上系統SOC已成為當今一種主流技術。基于IP復用的SOC設計是通過用戶自定義邏輯(UDL)和連線將IP核整合

2008-12-27 09:25:39 794

794

LDPC編譯碼LDPC碼是一種線性分組奇偶校驗碼,它采用基于因子圖的置信傳播(Belief Propagation,BP)迭代譯碼算法進行譯碼。其性能接近Turbo碼,不規則LDPC碼甚至超過Tur

2009-03-01 17:36:05 1798

1798

實驗九 PCM編譯碼 一、實驗目的

1. 掌握PCM編譯碼原理。 2. 掌握PCM基帶信號的形成過程

2009-04-01 14:44:49 10289

10289

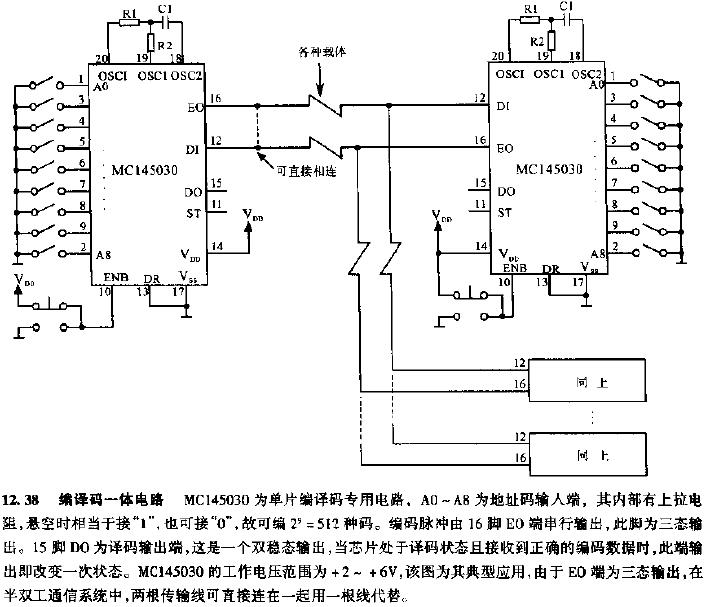

編譯碼一體電路圖

2009-04-18 15:34:48 752

752

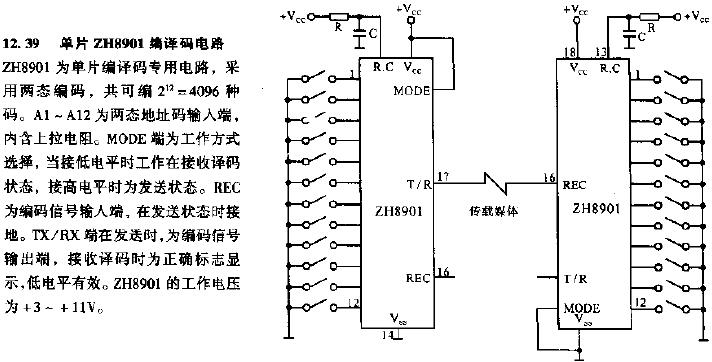

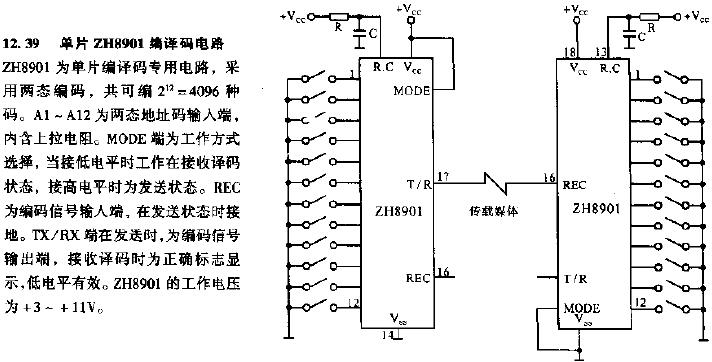

單片ZH8901編譯碼電路

2009-04-18 15:36:11 910

910

【摘 要】 介紹了ITU-TG.723.1標準語音編譯碼器的算法及其在ADSP-2181芯片上的實現 。軟硬件結合實現了語音信號的采樣和實時編譯碼,完全符合ITU-TG.723.1標準的定點算法

2009-05-10 19:54:11 1283

1283

摘要:提出了基于歐氏算法和頻譜分析相結合的RS碼硬件編譯碼方法;利用FPGA芯片實現了GF(2 8)上最高速率為50Mbps、最大延時為640ns的流式譯碼方案,滿足了高速

2009-06-20 14:19:33 856

856

ADPCM編譯碼系統電路

模擬信號

2009-10-11 11:07:30 1365

1365

噪聲消除的DSP算法研究

在語音傳輸的過程中,語音增強方案經常被采用。它使用FEC編碼技術(由卷積編碼和維特比譯碼算法組成)進行數據傳輸,有著大批量的數據運

2009-11-19 10:49:51 2466

2466

G.723.1算法在DSP上的優化

1 引言

G.723.1是刪組織于1996年推出的一種低碼率的語音編碼算法標準,也是目前該組織頒布的語音壓縮標準中碼率最低的一種標

2010-04-12 15:19:35 721

721 1 引言G.723.1是刪組織于1996年推出的一種低碼率的語音編碼算法標準,也是目前該組織頒布的語音壓縮標準中碼率最低的一種標準。G.723.1主要用于對語音及其它多媒體聲音信

2010-06-03 09:23:41 705

705 G.723.1是刪組織于 1996年推出的一種低碼率的語音編碼算法標準,也是目前該組織頒布的語音壓縮標準中碼率最低的一種標準。

G.723.1主要用于對語音及其它多媒體聲音信號的

2010-07-02 09:06:57 946

946 針對低密度奇偶校驗(LDPC)譯碼算法性能低的問題,提出一種基于最小和的高效譯碼算法。該算法從概率的角度分析消息的傳遞過程中校驗節點的更新過程,得到近似的最小和算法等式,

2011-05-18 18:54:20 0

0 基于Log_MAP 算法, 提出了一種TURBO 碼DSP 實現方案。利用內聯函數、循環展開, 軟件流水線技術對算法進行了優化, 在TMS320C6416 芯片上實現了36Mbps 的編碼速率及1.6Mbps 譯碼速率(5 次迭代)。該

2011-05-24 17:29:10 33

33 該文介紹了兩種Viterbi 譯碼器回溯譯碼算法,通過對這兩種算法硬件實現結構上的優化,給出了這兩種算法的FPGA 實現方法,比較了兩種實現方法的優缺點。最后將其應用在實際的Viter

2011-05-28 15:18:48 33

33 雙網傳真系統完成與Internet和PSTN網絡的傳真通信,采用嵌入式系統的設計思路劃分軟硬件。其中,傳真協議采用軟件實現,傳真編譯碼和外圍設備控制器采用硬件實現,以降低設計復雜

2011-07-12 11:19:59 1523

1523

Turbo碼是近年來通信系統糾錯編碼領域的重大突破,他以其接近Shannon限的優越性能博得眾多學者的青睞。本文采用基于Max-Log-Map的優化譯碼算法,對狀態量度歸一化計算和滑動窗算法等

2011-09-13 09:38:55 1438

1438

從赫夫曼樹定義及算法出發,介紹了一個赫夫曼編譯碼系統的設計與實現過程。這對于深入理解數據結構、程序設計有益。

2011-10-19 14:44:01 31

31 針對Turbo乘積碼(TPC)譯碼復雜度高、運算量大的缺點,分析了一種改進的TPC譯碼算法。該算法以Chase迭代算法為基礎,通過對錯誤圖樣重新排序產生新的測試序列,其伴隨式可從前次伴

2011-12-05 14:07:55 20

20 本文提出了一種基于STM32F103RET6的編譯碼系統方案,利用了STM32F103RET6強大的定時器功能,采用靈活的編譯碼方式,傳輸速率和數據幀格式都可以根據需要完全自行定義。

2012-03-04 14:38:45 6523

6523

本文介紹了 RS[ 255, 223 ]編譯碼器的 FPGA設計和基于線形反饋移位寄存器的編碼器設計 , 以及由伴隨式計算、關鍵方程求解、錢氏搜索、Forney算法等功能模塊組成的譯碼器。為了實現簡單

2012-05-22 10:43:40 45

45 針對傳統的Max-Log-Map譯碼算法時效性差、存儲空間開銷大的特點,本文對傳統的Max-Log-Map譯碼算法進行了改進。改進的算法對前、后向度量使用了蝶形結構圖,便于DSP實現;將原始幀均分

2012-07-27 17:55:16 42

42 介紹了符合CCSDS標準的RS(255,223)碼譯碼器的硬件實現結構。譯碼器采用8位并行時域譯碼算法,主要包括了修正后的無逆BM迭代譯碼算法,錢搜索算法和Forney算法。采用了三級流水線結構實現

2013-01-25 16:43:46 68

68 DSP算法的c語言實現,又需要的朋友下來看看。

2016-05-09 10:59:26 0

0 基于DSP的BOC信號捕獲算法實現_陳昌川

2017-01-08 10:30:29 3

3 基于FPGA的3B4B編譯碼電路

2017-02-07 14:58:18 11

11 本文從研究應用于AOS系統的RS(255,223)編譯碼接口卡出發,深入地分析和研究了糾錯碼原理、RS編譯碼算法與設計、PCI總線標準與設計和FPGA技術。 隨著科技的發展,糾錯碼技術在通信領域

2017-08-31 14:50:39 4

4 基于定點DSP的ART算法實現研究

2017-10-19 11:13:35 14

14 DSP最小系統設計及基本算法的實現

2017-10-20 09:45:45 11

11 為了降低非規則低密度奇偶校驗(low-densityparity-check,LDPC)碼譯碼算法的復雜度,提出一種適合數字信號處理囂(digital signal processor,DSP)實現

2017-10-20 10:41:11 0

0 DSP嵌入式系統開發典型案例,第9章 Viterbi譯碼及其實現

2017-10-20 14:23:37 4

4 效率,已成為當前急需解決的問題之一。DSP數字信號處理器的運算能力越來越強,本設計采用TI公司的通用定點DSP TMS320C5509A作為基帶系統的處理器,主要對G.723.1語音壓縮編碼在頻帶、DSP資源有限的數字對講機基帶系統中的具體應用進行

2017-10-24 10:22:42 0

0 2Mbps視頻數據流的Viterbi算法的移植與優化策略、技巧。 1 Viterbi算法原理簡介 Viterbi譯碼算法是由Viterbi于1967年提出的一種最大似然譯碼方法,譯碼器根據接收序列R按最大

2017-10-24 11:41:30 0

0 語音壓縮處理方法,G.723.1 語音編碼 算法 便是ITU-T(國際電信聯盟電信標準化部門)制定的H.324協議簇首推的標準算法,主要用于低比特率多媒體業務的話音或其他音頻信號分量的壓縮。它是一種雙速率語音編碼標準,其中6.3 kb/s的速率提供了

2017-10-25 10:05:22 1

1 1 引言 G.723.1是刪組織于1996年推出的一種低碼率的語音編碼算法標準,也是目前該組織頒布的語音壓縮標準中碼率最低的一種標準。G.723.1主要用于對語音及其它多媒體聲音信號的壓縮,目前

2017-10-25 11:13:56 0

0 1 引言 G.723.1是刪組織于1996年推出的一種低碼率的語音編碼算法標準,也是目前該組織頒布的語音壓縮標準中碼率最低的一種標準。G.723.1主要用于對語音及其它多媒體聲音信號的壓縮,目前

2017-11-01 16:03:40 0

0 1 引言 G.723.1是刪組織于1996年推出的一種低碼率的語音編碼算法標準,也是目前該組織頒布的語音壓縮標準中碼率最低的一種標準。G.723.1主要用于對語音及其它多媒體聲音信號的壓縮,目前

2017-11-02 10:43:04 0

0 優化方法以降低計算量,最后給出了各個主要模塊的性能指標。該實現能夠在200MHz的C6201 DSP上實現16路語音信號的實時編解碼,完全符合ITU-T G.723.1標準的定點算法,通過了ITU-T的所有測試

2017-11-06 14:55:13 1

1 在二進制離散無記憶信道中極化碼可以達到其信道極限容量,并且實現的復雜度較低,這在通信領域無疑是一個重大突破,因此在FPGA中實現極化碼的譯碼有著非常重要的研究意義。首先介紹了SC

2017-11-15 16:50:25 4335

4335

了硬件資源的消耗量。該方法適合于采用校驗矩陣進行編碼和譯碼的情況,不僅適用于全并行的編譯碼器結構,同時也適用于目前廣泛采用的部分并行結構,且能夠使用和積、最小和等多種譯碼算法。

2017-11-22 07:34:01 3928

3928

中小長度的數據報文業務為主,所以突發通信中的Turbo碼的碼長也是中等長度以下的。本文面向突發數據通信中的信道編碼應用,研究了短幀長Turbo碼編譯碼算法的FPGA實現。實現中采用了優化的編譯碼算法,以降低譯碼復雜度和譯碼延時。最后仿真和測試了Turbo譯碼器的糾錯性能和吞吐量。

2018-07-12 08:15:00 3246

3246

不規則重復累積碼(IRA)的譯碼通常采用置信傳播(BP)譯碼算法,然而BP譯碼算法需進行雙曲正切函數計算,復雜度高,不利于硬件實現。為此,提出一種基于分段函數修正和預檢測機制結合的譯碼算法,通過對折

2018-01-08 15:52:39 0

0 coding,RS-CC碼)以構造等效刪除信道,并采用實時性高的短I_T碼實現糾刪功能。設計了一種適合短I.T碼的譯碼算法,同時給出了編碼度分布的選取方法。仿真結果表明,與已有短噴泉碼相比,文中短I_T碼成功譯碼時所需編碼冗余更少,應用到級聯方案后的數據傳輸可靠性明顯提高

2018-03-20 16:19:12 0

0 第三代移動通信系統多種方案中,考忠將Turbo碼作為無線信道的編碼標準之- ~。 本文討論了Turbo碼的編譯碼基本原理,對Turbo碼的幾種常用的編譯碼算法進行了分析,并在給出編譯碼器模型的基礎上,用MATLAB語言實現了整個系統的計算機仿真并給出參

2019-01-04 10:40:42 19

19 極化碼的譯碼算法研究近年來發展迅速,其中成為研究熱點的連續刪除(Successive Cancellation,SC)譯碼算法的基本思想是通過對信息位的比特似然概率值的判斷來進行譯碼。

2019-01-06 11:19:55 4845

4845

當用Matlab完成數字信號處理算法仿真后,如何在DSP芯片上實時實現,是電氣信息類大學生需要掌握的一項重要的工程實踐能力。在仿真過程中,有算法移植、DSP工程建立和算法實現這三個關鍵環節。本文介紹

2020-09-10 16:08:12 32

32 本文檔的主要內容詳細介紹的是如何進行DSP的軟件編程及使用算法實現的學習教程說明包括了: DSP應用系統的一般開發流程,DSP與MCS51、PC硬件結構對算法的影響,針對不同的算法來選擇DsP與編程語言,DSP常用算法簡介,DSP算法的仿真,DSP算法的移植與實現。

2020-09-16 17:49:00 17

17 本系統使用TI公司浮點型DSP TMS320C6713實現G.723.1等語音編解碼,為G.723.1、G.729等常用的低碼率語音壓縮標準提供運行及測試硬件平臺。有別于大多數編解碼系統,本設計采用

2020-09-21 09:58:07 3122

3122

結構化LDPC碼可進行相應擴展通過對編譯碼算法,優化編譯碼結構進行調整,降低了編譯碼囂硬件實現中的關鍵路徑遲延,并采用Xilinx公司的Virtex一4 VLX80 FPGA芯片實現了一個碼長10 240,碼率1/2的非正則結構化LDPC碼編碼器和譯碼器。實現結果表明:該編碼器信息吞吐量為1.878 Gb/

2021-03-26 15:58:00 12

12 基于軟件無線電的NRLDPC編譯碼設計與實現。

2021-05-28 10:07:04 5

5 DSP軟件編程與算法實現的過程說明。

2021-05-28 14:34:44 24

24 電子發燒友網站提供《基于VHDL語言的循環碼編譯碼系統的設計.pdf》資料免費下載

2023-10-13 14:31:37 1

1 電子發燒友網站提供《漢明碼編譯碼文檔.doc》資料免費下載

2023-11-17 16:04:06 0

0

![]()

![]()

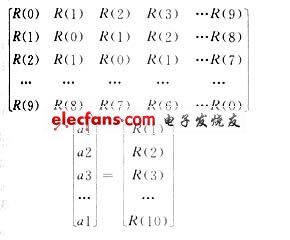

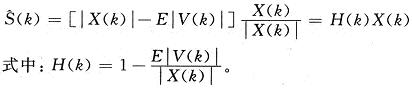

![]() =1,2,...10),由此可得到以

=1,2,...10),由此可得到以![]() k為變量的方程組:

k為變量的方程組:

電子發燒友App

電子發燒友App

評論