我最近在學(xué)習(xí)用matalb生成dsp6748使用的算法,按照創(chuàng)龍給的資料中使用 這篇pdf的做法,前面幾步都沒有問題,在最后一步編譯的時(shí)候報(bào)錯(cuò)如下:想請(qǐng)問下創(chuàng)龍工程師,這個(gè)interface文件夾下的程序是什么功能,還有就是這樣的報(bào)錯(cuò)應(yīng)該怎么解決?

2020-03-26 11:21:21

Viterbi 譯碼算法可以簡單概括為“相加-比較-保留”,譯碼器運(yùn)行是前向的、無反饋的,實(shí)現(xiàn)過程并不復(fù)雜。我們來分析Viterbi 算法的復(fù)雜度: (n, k, N) 卷積碼的狀態(tài)數(shù)為 條幸存

2008-05-30 16:11:37

使用

dsp c5517

實(shí)現(xiàn)viterbi (2,1,7)

譯碼?

譯碼的波特率是115200bps,有誰會(huì)的,可以私聊,有償?shù)摹?/div>

2017-05-02 16:20:09

本帖最后由 mr.pengyongche 于 2013-4-30 02:23 編輯

基于DSP的FFT算法實(shí)現(xiàn)[url=www.6668.cc]

2012-08-17 13:56:25

由于卷積碼優(yōu)良的性能,被廣泛應(yīng)用于深空通信、衛(wèi)星通信和2G、3G移動(dòng)通信中。卷積碼有三種譯碼方法:門限譯碼、概率譯碼和Viterbi算法,其中Viterbi算法是一種基于網(wǎng)格圖的最大似然譯碼算法,是卷積碼的最佳譯碼方式,具有效率高、速度快等優(yōu)點(diǎn)。

2019-11-01 08:05:38

【摘要】:Viterbi譯碼器在通信系統(tǒng)中應(yīng)用非常普遍,針對(duì)采用DSP只能進(jìn)行相對(duì)較低速率的Vit-erbi譯碼的問題,人們開始采用FPGA實(shí)現(xiàn)高速率Viterbi譯碼。本文首先簡單描述了

2010-04-26 16:08:39

本文將討論其中的前兩項(xiàng):具體地說,首ff先是介紹如何實(shí)現(xiàn)OFDMA的核心DSP算法,然后是被LTE用來實(shí)現(xiàn)上行鏈路的新技術(shù),最后簡要介紹用于WiMAX和LTE的MIMO(所有IP方面的內(nèi)容不在本文討論范圍內(nèi))。本文討論的前提條件是采用軟件定義的架構(gòu)。

2021-06-01 06:49:13

一種在FPGA中實(shí)現(xiàn)的基于軟判決的Viterbi譯碼算法,并以一個(gè)(2,1,2)、回溯深度為10的軟判決Viterbi譯碼算法為例驗(yàn)證該算法,在Xilinx的XC3S500E芯片上實(shí)現(xiàn)了該譯碼器,最后對(duì)其性能做了分析。 關(guān)鍵詞: OFDM;Viterbi譯碼;軟判決;FPGA

2009-09-19 09:41:24

本文研究了RS碼的實(shí)現(xiàn)方法,并基于Xilinx的FPGA芯片Spartan-6 XC6SLX45完成了RS編譯碼器的設(shè)計(jì),同時(shí)對(duì)其進(jìn)行了仿真和在線調(diào)試,并給出了功能仿真圖和測(cè)試結(jié)果。時(shí)序仿真結(jié)果表明,該編譯碼器能實(shí)現(xiàn)預(yù)期功能。

2021-06-21 06:23:53

。Turbo碼現(xiàn)已成為深空通信的標(biāo)準(zhǔn),即第三代移動(dòng)通信(3G)信道編碼方案[2]。Turbo碼雖然具有優(yōu)異的譯碼性能,但是由于其譯碼復(fù)雜度高,譯碼延時(shí)大等問題,嚴(yán)重制約了Turbo碼在高速通信系統(tǒng)中的應(yīng)用。因此,如何設(shè)計(jì)一個(gè)簡單有效的譯碼器是目前Turbo碼實(shí)用化研究的重點(diǎn)。

2019-08-22 07:28:46

本文介紹了基于FPGA的CVSD語音編譯碼的設(shè)計(jì)思路、具體實(shí)現(xiàn)以及和專用芯片CMX639之間的互相通信。

2021-04-30 06:32:01

截短Reed-Solomon碼譯碼器的FPGA實(shí)現(xiàn)提出了一種改進(jìn)的BM算法,并在此基礎(chǔ)上提出了一種大量采用并行結(jié)構(gòu)的截短RS碼譯碼器的實(shí)現(xiàn)方式。驗(yàn)證表明,該算法能顯著提高基于FPGA的RS譯碼

2009-09-19 09:39:43

我是初學(xué)者,我需要用DSP做一個(gè)G代碼編譯器。需要實(shí)現(xiàn)的功能是輸入一行G代碼,一個(gè)個(gè)將它讀入、分析。求大神們幫幫幫。謝謝了。

2014-05-27 12:22:35

Turbo碼編碼器的FPGA實(shí)現(xiàn)Turbo碼譯碼器的FPGA實(shí)現(xiàn)Turbo碼編譯碼器的性能有哪些?

2021-05-07 06:06:23

不規(guī)則重復(fù)累計(jì)碼BP譯碼算法具有接近Shannon限優(yōu)越性能,但具有較高的復(fù)雜度。為了降低復(fù)雜度,提出了IRA碼最小和算法和曲線折線化算法。最小和算法具有簡單、容易實(shí)現(xiàn)的特

2008-11-20 12:12:20 9

9 在DSP 上移植算法,代碼優(yōu)化程度成為提高系統(tǒng)性能、縮短開發(fā)周期的瓶頸。同時(shí)針對(duì)復(fù)雜算法在DSP 上的實(shí)現(xiàn), 也產(chǎn)生很多優(yōu)化策略、方法。本文以在數(shù)字通信系統(tǒng)中應(yīng)用廣泛的Viter

2009-04-15 11:15:44 18

18 簡易編譯碼電路圖

2009-05-19 10:47:26 9

9 面向IEEE 802.16e 中 LDPC 碼,分析了各種譯碼算法的譯碼性能,歸一化最小(NMS)算法具備較高譯碼性能和實(shí)現(xiàn)復(fù)雜度低的特點(diǎn)。提出一種基于部分并行方式的LDPC 譯碼器結(jié)構(gòu),可以滿

2009-08-05 08:46:59 24

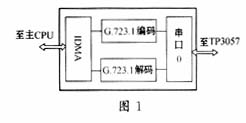

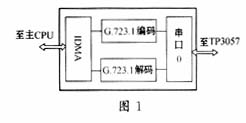

24 本文首先闡述了G.723.1語音編解碼標(biāo)準(zhǔn)的流程。根據(jù)低功耗、高性能的16位定點(diǎn)的數(shù)字信號(hào)處理芯片TMS320DM642的特點(diǎn)對(duì)源代碼中運(yùn)算量較大的模塊進(jìn)行了代碼優(yōu)化。最后,在DSP硬

2009-08-10 10:00:11 31

31 RS 碼以其強(qiáng)大的糾正隨機(jī)錯(cuò)誤和突發(fā)錯(cuò)誤的能力,被廣泛地應(yīng)用于各種數(shù)字通信系統(tǒng)中,本文首先敘述了RS 碼譯碼的基本原理,給出了實(shí)現(xiàn)RS 碼軟判決譯碼的方法和用DSP 實(shí)現(xiàn)譯碼的

2009-08-19 10:26:07 22

22 基于可靠性更新的低復(fù)雜度B譯碼算法:基于部分符號(hào)更新策略的BP (Belief Propagation)譯碼算法減少了LDPC (Low-Density Parity-Check)碼的譯碼運(yùn)算量,提高了譯碼效率。然而在其譯碼過程中,由

2009-10-29 13:09:21 16

16 3G測(cè)試系統(tǒng)中的Viterbi譯碼及其DSP實(shí)現(xiàn)及優(yōu)化

摘要 介紹了一種用于測(cè)試TD-SCDMA手機(jī)終端測(cè)試平臺(tái)中的關(guān)鍵技術(shù)——Viterbi譯碼。研究用約束度K=9的卷積編碼和最大似然Viterbi譯

2009-11-13 18:51:25 18

18 該文從譯碼速率、硬件實(shí)現(xiàn)的復(fù)雜度和誤碼率3 個(gè)方面對(duì)比研究了兩種典型的高速譯碼算法:Turbo 型和積算法與并行加權(quán)比特翻轉(zhuǎn)算法。以準(zhǔn)循環(huán)LDPC 碼為對(duì)象,給出了Turbo 型和積算

2009-11-25 15:26:58 9

9 Turbo 碼的工程應(yīng)用與實(shí)現(xiàn)是近年來研究工作的熱點(diǎn)。Turbo 碼采用反饋迭代譯碼結(jié)構(gòu),成員譯碼器使用最大后驗(yàn)概率(MAP)譯碼算法譯碼,由于MAP 算法含有大量的指數(shù)運(yùn)算與對(duì)數(shù)運(yùn)算,

2009-11-27 15:15:31 7

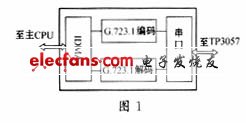

7 ITU-T G.723.1 是一種用于多媒體通信的雙碼率語音編碼標(biāo)準(zhǔn)。本文在簡單介紹其編解碼算法和浮點(diǎn)數(shù)字信號(hào)處理器TMS320C6713 之后,著重介紹了該編解碼算法在TMS320C6713 DSK 上的軟件和硬

2009-11-27 15:31:23 10

10 本文利用可編程邏輯的靈活性和Nios 的強(qiáng)大處理能力,將多種編譯碼模塊和微處理器模塊集成到一片F(xiàn)PGA 內(nèi)部,方便地實(shí)現(xiàn)了通用編譯碼器的設(shè)計(jì)。由于采用了VHDL 語言,使系統(tǒng)具有可移

2009-11-30 14:27:56 22

22 在ITU-T 的G.723.1 語音編解碼算法基礎(chǔ)上,本文詳細(xì)介紹了該算法在定點(diǎn) C 語言程序和全匯編程序實(shí)現(xiàn)時(shí)的關(guān)鍵技術(shù)和優(yōu)化策略,使優(yōu)化后的 G.723.1 編碼器在內(nèi)存占用率和運(yùn)算復(fù)雜

2009-12-18 14:40:37 9

9 介紹了 TI 的TMS320C6416 DSP 片上Viterbi 譯碼協(xié)處理器(VCP)的結(jié)構(gòu)與原理。給出了一種使用鏈?zhǔn)紼DMA 結(jié)構(gòu)和“乒乓”緩沖技術(shù)提高VCP 譯碼過程并行性的方法。設(shè)計(jì)出基于MATLAB 的Link for

2009-12-23 15:19:48 19

19 文章分析了Turbo 碼的MAP 類譯碼算法后,針對(duì)傳統(tǒng)Log—MAP 譯碼算法的特性,提出了一種改進(jìn)的Log—MAP 譯碼算法。仿真結(jié)果表明,新的算法在降低譯碼復(fù)雜度的同時(shí)較好地保持了譯

2010-01-15 11:51:47 13

13 數(shù)字光纖通信系統(tǒng)的原理框圖如圖1所示(其中調(diào)制器與解調(diào)器包括電光轉(zhuǎn)換與光電轉(zhuǎn)換功能),我們所做的工作是設(shè)計(jì)信道編譯碼部分的電路,在通信系統(tǒng)中所處的位置如圖中虛線

2010-04-20 22:33:12 83

83 IRA碼的譯碼通常是利用BP譯碼算法來實(shí)現(xiàn)的,但是BP譯碼算法的硬件電路復(fù)雜。為了讓譯碼算法在復(fù)雜度和譯碼性能之間取得較好的折衷,提出一種改進(jìn)型IRA譯碼算法,該算法采用偏

2010-07-05 16:23:56 21

21 基于TMS320C6416高性能通用DSP,實(shí)現(xiàn)了對(duì)AWGN信道的信噪比(SNR)估計(jì),并以此估計(jì)值設(shè)計(jì)了一種低密度奇偶校驗(yàn)(LDPC)碼的譯碼系統(tǒng);詳盡介紹了集成SNR估計(jì)的譯碼系統(tǒng)的實(shí)現(xiàn)方案和流程;仿真

2010-07-27 16:28:32 11

11 針對(duì)固定碼長Turbo碼適應(yīng)性差的缺點(diǎn),以LTE為應(yīng)用背景,提出了一種幀長可配置的Turbo編譯碼器的FPGA實(shí)現(xiàn)方案。該設(shè)計(jì)可以依據(jù)具體的信道環(huán)境和速率要求調(diào)節(jié)信息幀長,平衡譯碼性

2010-11-11 16:07:59 26

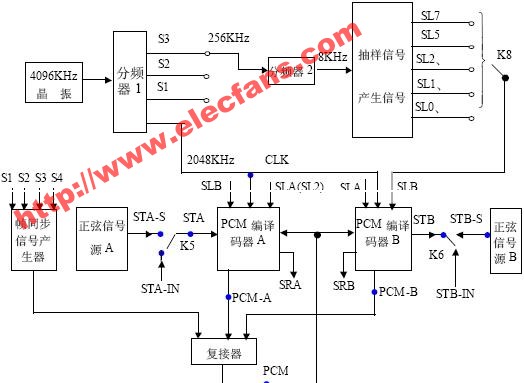

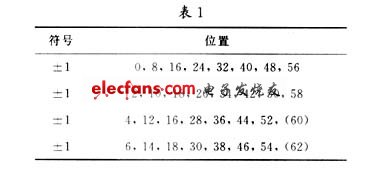

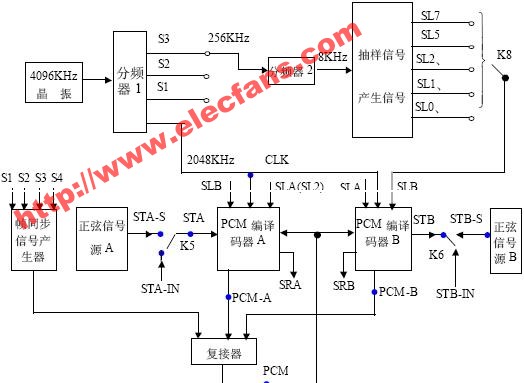

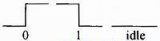

26 PCM編譯碼模塊原理

本模塊的原理方框圖圖5-2所示,模塊內(nèi)部使用+5V和-5V電壓,其中-5V電壓由-12V電源經(jīng)7905變換得到。

2008-10-21 13:31:10 7114

7114

PCM編譯碼實(shí)驗(yàn)

一、實(shí)驗(yàn)?zāi)康?. 掌握PCM編譯碼

2008-10-21 13:35:45 8339

8339

基于BIST的編譯碼器IP核測(cè)

隨著半導(dǎo)體工藝的發(fā)展,片上系統(tǒng)SOC已成為當(dāng)今一種主流技術(shù)。基于IP復(fù)用的SOC設(shè)計(jì)是通過用戶自定義邏輯(UDL)和連線將IP核整合

2008-12-27 09:25:39 794

794

LDPC編譯碼LDPC碼是一種線性分組奇偶校驗(yàn)碼,它采用基于因子圖的置信傳播(Belief Propagation,BP)迭代譯碼算法進(jìn)行譯碼。其性能接近Turbo碼,不規(guī)則LDPC碼甚至超過Tur

2009-03-01 17:36:05 1798

1798

實(shí)驗(yàn)九 PCM編譯碼 一、實(shí)驗(yàn)?zāi)康?

1. 掌握PCM編譯碼原理。 2. 掌握PCM基帶信號(hào)的形成過程

2009-04-01 14:44:49 10289

10289

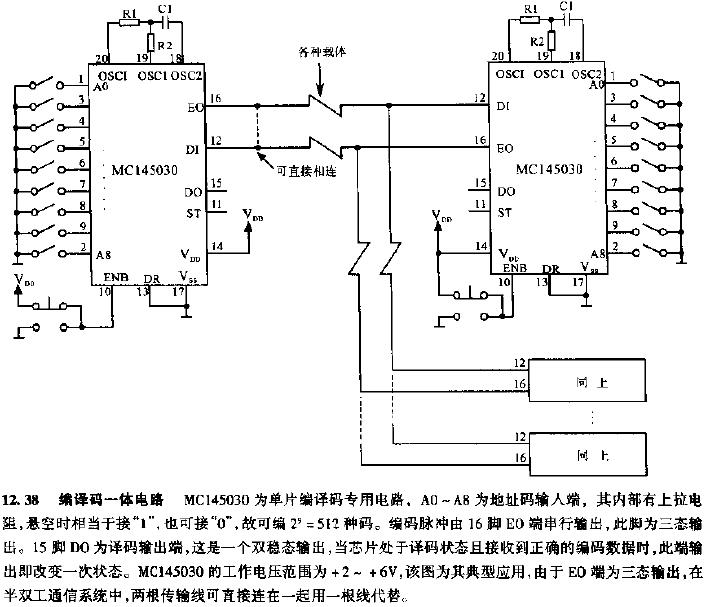

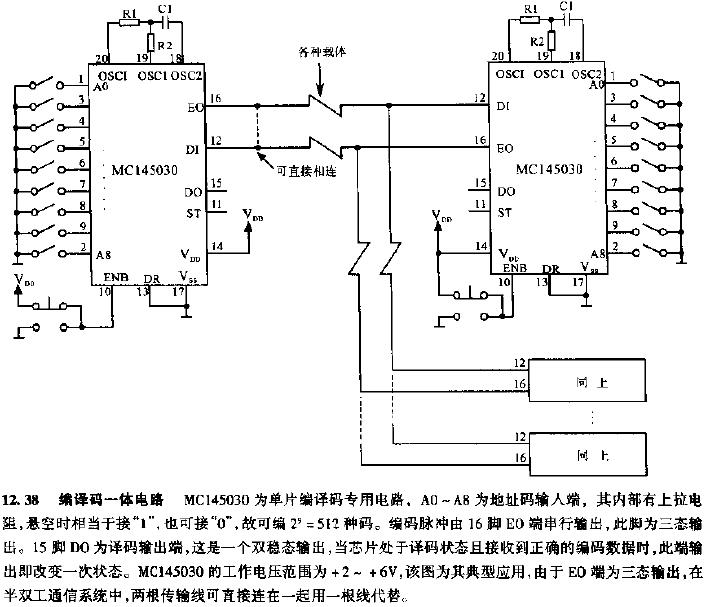

編譯碼一體電路圖

2009-04-18 15:34:48 752

752

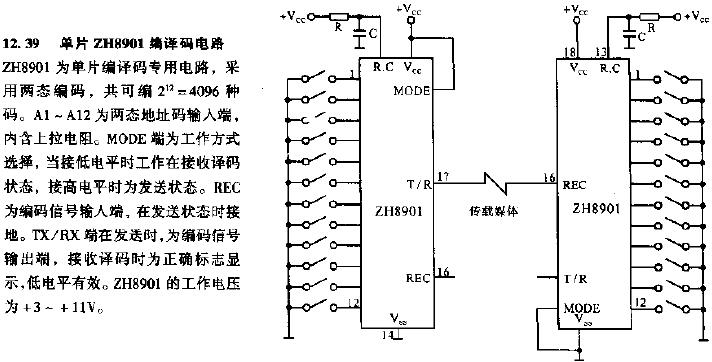

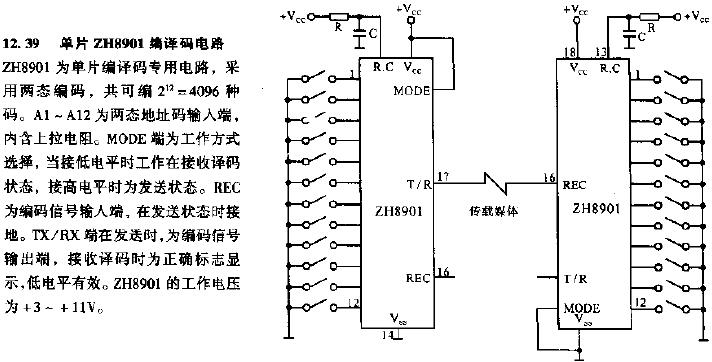

單片ZH8901編譯碼電路

2009-04-18 15:36:11 910

910

【摘 要】 介紹了ITU-TG.723.1標(biāo)準(zhǔn)語音編譯碼器的算法及其在ADSP-2181芯片上的實(shí)現(xiàn) 。軟硬件結(jié)合實(shí)現(xiàn)了語音信號(hào)的采樣和實(shí)時(shí)編譯碼,完全符合ITU-TG.723.1標(biāo)準(zhǔn)的定點(diǎn)算法

2009-05-10 19:54:11 1283

1283

摘要:提出了基于歐氏算法和頻譜分析相結(jié)合的RS碼硬件編譯碼方法;利用FPGA芯片實(shí)現(xiàn)了GF(2 8)上最高速率為50Mbps、最大延時(shí)為640ns的流式譯碼方案,滿足了高速

2009-06-20 14:19:33 856

856

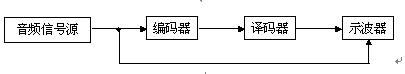

ADPCM編譯碼系統(tǒng)電路

模擬信號(hào)

2009-10-11 11:07:30 1365

1365

噪聲消除的DSP算法研究

在語音傳輸?shù)倪^程中,語音增強(qiáng)方案經(jīng)常被采用。它使用FEC編碼技術(shù)(由卷積編碼和維特比譯碼算法組成)進(jìn)行數(shù)據(jù)傳輸,有著大批量的數(shù)據(jù)運(yùn)

2009-11-19 10:49:51 2466

2466

G.723.1算法在DSP上的優(yōu)化

1 引言

G.723.1是刪組織于1996年推出的一種低碼率的語音編碼算法標(biāo)準(zhǔn),也是目前該組織頒布的語音壓縮標(biāo)準(zhǔn)中碼率最低的一種標(biāo)

2010-04-12 15:19:35 721

721 1 引言G.723.1是刪組織于1996年推出的一種低碼率的語音編碼算法標(biāo)準(zhǔn),也是目前該組織頒布的語音壓縮標(biāo)準(zhǔn)中碼率最低的一種標(biāo)準(zhǔn)。G.723.1主要用于對(duì)語音及其它多媒體聲音信

2010-06-03 09:23:41 705

705 G.723.1是刪組織于 1996年推出的一種低碼率的語音編碼算法標(biāo)準(zhǔn),也是目前該組織頒布的語音壓縮標(biāo)準(zhǔn)中碼率最低的一種標(biāo)準(zhǔn)。

G.723.1主要用于對(duì)語音及其它多媒體聲音信號(hào)的

2010-07-02 09:06:57 946

946 針對(duì)低密度奇偶校驗(yàn)(LDPC)譯碼算法性能低的問題,提出一種基于最小和的高效譯碼算法。該算法從概率的角度分析消息的傳遞過程中校驗(yàn)節(jié)點(diǎn)的更新過程,得到近似的最小和算法等式,

2011-05-18 18:54:20 0

0 基于Log_MAP 算法, 提出了一種TURBO 碼DSP 實(shí)現(xiàn)方案。利用內(nèi)聯(lián)函數(shù)、循環(huán)展開, 軟件流水線技術(shù)對(duì)算法進(jìn)行了優(yōu)化, 在TMS320C6416 芯片上實(shí)現(xiàn)了36Mbps 的編碼速率及1.6Mbps 譯碼速率(5 次迭代)。該

2011-05-24 17:29:10 33

33 該文介紹了兩種Viterbi 譯碼器回溯譯碼算法,通過對(duì)這兩種算法硬件實(shí)現(xiàn)結(jié)構(gòu)上的優(yōu)化,給出了這兩種算法的FPGA 實(shí)現(xiàn)方法,比較了兩種實(shí)現(xiàn)方法的優(yōu)缺點(diǎn)。最后將其應(yīng)用在實(shí)際的Viter

2011-05-28 15:18:48 33

33 雙網(wǎng)傳真系統(tǒng)完成與Internet和PSTN網(wǎng)絡(luò)的傳真通信,采用嵌入式系統(tǒng)的設(shè)計(jì)思路劃分軟硬件。其中,傳真協(xié)議采用軟件實(shí)現(xiàn),傳真編譯碼和外圍設(shè)備控制器采用硬件實(shí)現(xiàn),以降低設(shè)計(jì)復(fù)雜

2011-07-12 11:19:59 1523

1523

Turbo碼是近年來通信系統(tǒng)糾錯(cuò)編碼領(lǐng)域的重大突破,他以其接近Shannon限的優(yōu)越性能博得眾多學(xué)者的青睞。本文采用基于Max-Log-Map的優(yōu)化譯碼算法,對(duì)狀態(tài)量度歸一化計(jì)算和滑動(dòng)窗算法等

2011-09-13 09:38:55 1438

1438

從赫夫曼樹定義及算法出發(fā),介紹了一個(gè)赫夫曼編譯碼系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)過程。這對(duì)于深入理解數(shù)據(jù)結(jié)構(gòu)、程序設(shè)計(jì)有益。

2011-10-19 14:44:01 31

31 針對(duì)Turbo乘積碼(TPC)譯碼復(fù)雜度高、運(yùn)算量大的缺點(diǎn),分析了一種改進(jìn)的TPC譯碼算法。該算法以Chase迭代算法為基礎(chǔ),通過對(duì)錯(cuò)誤圖樣重新排序產(chǎn)生新的測(cè)試序列,其伴隨式可從前次伴

2011-12-05 14:07:55 20

20 本文提出了一種基于STM32F103RET6的編譯碼系統(tǒng)方案,利用了STM32F103RET6強(qiáng)大的定時(shí)器功能,采用靈活的編譯碼方式,傳輸速率和數(shù)據(jù)幀格式都可以根據(jù)需要完全自行定義。

2012-03-04 14:38:45 6523

6523

本文介紹了 RS[ 255, 223 ]編譯碼器的 FPGA設(shè)計(jì)和基于線形反饋移位寄存器的編碼器設(shè)計(jì) , 以及由伴隨式計(jì)算、關(guān)鍵方程求解、錢氏搜索、Forney算法等功能模塊組成的譯碼器。為了實(shí)現(xiàn)簡單

2012-05-22 10:43:40 45

45 針對(duì)傳統(tǒng)的Max-Log-Map譯碼算法時(shí)效性差、存儲(chǔ)空間開銷大的特點(diǎn),本文對(duì)傳統(tǒng)的Max-Log-Map譯碼算法進(jìn)行了改進(jìn)。改進(jìn)的算法對(duì)前、后向度量使用了蝶形結(jié)構(gòu)圖,便于DSP實(shí)現(xiàn);將原始幀均分

2012-07-27 17:55:16 42

42 介紹了符合CCSDS標(biāo)準(zhǔn)的RS(255,223)碼譯碼器的硬件實(shí)現(xiàn)結(jié)構(gòu)。譯碼器采用8位并行時(shí)域譯碼算法,主要包括了修正后的無逆BM迭代譯碼算法,錢搜索算法和Forney算法。采用了三級(jí)流水線結(jié)構(gòu)實(shí)現(xiàn)

2013-01-25 16:43:46 68

68 DSP算法的c語言實(shí)現(xiàn),又需要的朋友下來看看。

2016-05-09 10:59:26 0

0 基于DSP的BOC信號(hào)捕獲算法實(shí)現(xiàn)_陳昌川

2017-01-08 10:30:29 3

3 基于FPGA的3B4B編譯碼電路

2017-02-07 14:58:18 11

11 本文從研究應(yīng)用于AOS系統(tǒng)的RS(255,223)編譯碼接口卡出發(fā),深入地分析和研究了糾錯(cuò)碼原理、RS編譯碼算法與設(shè)計(jì)、PCI總線標(biāo)準(zhǔn)與設(shè)計(jì)和FPGA技術(shù)。 隨著科技的發(fā)展,糾錯(cuò)碼技術(shù)在通信領(lǐng)域

2017-08-31 14:50:39 4

4 基于定點(diǎn)DSP的ART算法實(shí)現(xiàn)研究

2017-10-19 11:13:35 14

14 DSP最小系統(tǒng)設(shè)計(jì)及基本算法的實(shí)現(xiàn)

2017-10-20 09:45:45 11

11 為了降低非規(guī)則低密度奇偶校驗(yàn)(low-densityparity-check,LDPC)碼譯碼算法的復(fù)雜度,提出一種適合數(shù)字信號(hào)處理囂(digital signal processor,DSP)實(shí)現(xiàn)

2017-10-20 10:41:11 0

0 DSP嵌入式系統(tǒng)開發(fā)典型案例,第9章 Viterbi譯碼及其實(shí)現(xiàn)

2017-10-20 14:23:37 4

4 效率,已成為當(dāng)前急需解決的問題之一。DSP數(shù)字信號(hào)處理器的運(yùn)算能力越來越強(qiáng),本設(shè)計(jì)采用TI公司的通用定點(diǎn)DSP TMS320C5509A作為基帶系統(tǒng)的處理器,主要對(duì)G.723.1語音壓縮編碼在頻帶、DSP資源有限的數(shù)字對(duì)講機(jī)基帶系統(tǒng)中的具體應(yīng)用進(jìn)行

2017-10-24 10:22:42 0

0 2Mbps視頻數(shù)據(jù)流的Viterbi算法的移植與優(yōu)化策略、技巧。 1 Viterbi算法原理簡介 Viterbi譯碼算法是由Viterbi于1967年提出的一種最大似然譯碼方法,譯碼器根據(jù)接收序列R按最大

2017-10-24 11:41:30 0

0 語音壓縮處理方法,G.723.1 語音編碼 算法 便是ITU-T(國際電信聯(lián)盟電信標(biāo)準(zhǔn)化部門)制定的H.324協(xié)議簇首推的標(biāo)準(zhǔn)算法,主要用于低比特率多媒體業(yè)務(wù)的話音或其他音頻信號(hào)分量的壓縮。它是一種雙速率語音編碼標(biāo)準(zhǔn),其中6.3 kb/s的速率提供了

2017-10-25 10:05:22 1

1 1 引言 G.723.1是刪組織于1996年推出的一種低碼率的語音編碼算法標(biāo)準(zhǔn),也是目前該組織頒布的語音壓縮標(biāo)準(zhǔn)中碼率最低的一種標(biāo)準(zhǔn)。G.723.1主要用于對(duì)語音及其它多媒體聲音信號(hào)的壓縮,目前

2017-10-25 11:13:56 0

0 1 引言 G.723.1是刪組織于1996年推出的一種低碼率的語音編碼算法標(biāo)準(zhǔn),也是目前該組織頒布的語音壓縮標(biāo)準(zhǔn)中碼率最低的一種標(biāo)準(zhǔn)。G.723.1主要用于對(duì)語音及其它多媒體聲音信號(hào)的壓縮,目前

2017-11-01 16:03:40 0

0 1 引言 G.723.1是刪組織于1996年推出的一種低碼率的語音編碼算法標(biāo)準(zhǔn),也是目前該組織頒布的語音壓縮標(biāo)準(zhǔn)中碼率最低的一種標(biāo)準(zhǔn)。G.723.1主要用于對(duì)語音及其它多媒體聲音信號(hào)的壓縮,目前

2017-11-02 10:43:04 0

0 優(yōu)化方法以降低計(jì)算量,最后給出了各個(gè)主要模塊的性能指標(biāo)。該實(shí)現(xiàn)能夠在200MHz的C6201 DSP上實(shí)現(xiàn)16路語音信號(hào)的實(shí)時(shí)編解碼,完全符合ITU-T G.723.1標(biāo)準(zhǔn)的定點(diǎn)算法,通過了ITU-T的所有測(cè)試

2017-11-06 14:55:13 1

1 在二進(jìn)制離散無記憶信道中極化碼可以達(dá)到其信道極限容量,并且實(shí)現(xiàn)的復(fù)雜度較低,這在通信領(lǐng)域無疑是一個(gè)重大突破,因此在FPGA中實(shí)現(xiàn)極化碼的譯碼有著非常重要的研究意義。首先介紹了SC

2017-11-15 16:50:25 4335

4335

了硬件資源的消耗量。該方法適合于采用校驗(yàn)矩陣進(jìn)行編碼和譯碼的情況,不僅適用于全并行的編譯碼器結(jié)構(gòu),同時(shí)也適用于目前廣泛采用的部分并行結(jié)構(gòu),且能夠使用和積、最小和等多種譯碼算法。

2017-11-22 07:34:01 3928

3928

中小長度的數(shù)據(jù)報(bào)文業(yè)務(wù)為主,所以突發(fā)通信中的Turbo碼的碼長也是中等長度以下的。本文面向突發(fā)數(shù)據(jù)通信中的信道編碼應(yīng)用,研究了短幀長Turbo碼編譯碼算法的FPGA實(shí)現(xiàn)。實(shí)現(xiàn)中采用了優(yōu)化的編譯碼算法,以降低譯碼復(fù)雜度和譯碼延時(shí)。最后仿真和測(cè)試了Turbo譯碼器的糾錯(cuò)性能和吞吐量。

2018-07-12 08:15:00 3246

3246

不規(guī)則重復(fù)累積碼(IRA)的譯碼通常采用置信傳播(BP)譯碼算法,然而BP譯碼算法需進(jìn)行雙曲正切函數(shù)計(jì)算,復(fù)雜度高,不利于硬件實(shí)現(xiàn)。為此,提出一種基于分段函數(shù)修正和預(yù)檢測(cè)機(jī)制結(jié)合的譯碼算法,通過對(duì)折

2018-01-08 15:52:39 0

0 coding,RS-CC碼)以構(gòu)造等效刪除信道,并采用實(shí)時(shí)性高的短I_T碼實(shí)現(xiàn)糾刪功能。設(shè)計(jì)了一種適合短I.T碼的譯碼算法,同時(shí)給出了編碼度分布的選取方法。仿真結(jié)果表明,與已有短噴泉碼相比,文中短I_T碼成功譯碼時(shí)所需編碼冗余更少,應(yīng)用到級(jí)聯(lián)方案后的數(shù)據(jù)傳輸可靠性明顯提高

2018-03-20 16:19:12 0

0 第三代移動(dòng)通信系統(tǒng)多種方案中,考忠將Turbo碼作為無線信道的編碼標(biāo)準(zhǔn)之- ~。 本文討論了Turbo碼的編譯碼基本原理,對(duì)Turbo碼的幾種常用的編譯碼算法進(jìn)行了分析,并在給出編譯碼器模型的基礎(chǔ)上,用MATLAB語言實(shí)現(xiàn)了整個(gè)系統(tǒng)的計(jì)算機(jī)仿真并給出參

2019-01-04 10:40:42 19

19 極化碼的譯碼算法研究近年來發(fā)展迅速,其中成為研究熱點(diǎn)的連續(xù)刪除(Successive Cancellation,SC)譯碼算法的基本思想是通過對(duì)信息位的比特似然概率值的判斷來進(jìn)行譯碼。

2019-01-06 11:19:55 4845

4845

當(dāng)用Matlab完成數(shù)字信號(hào)處理算法仿真后,如何在DSP芯片上實(shí)時(shí)實(shí)現(xiàn),是電氣信息類大學(xué)生需要掌握的一項(xiàng)重要的工程實(shí)踐能力。在仿真過程中,有算法移植、DSP工程建立和算法實(shí)現(xiàn)這三個(gè)關(guān)鍵環(huán)節(jié)。本文介紹

2020-09-10 16:08:12 32

32 本文檔的主要內(nèi)容詳細(xì)介紹的是如何進(jìn)行DSP的軟件編程及使用算法實(shí)現(xiàn)的學(xué)習(xí)教程說明包括了: DSP應(yīng)用系統(tǒng)的一般開發(fā)流程,DSP與MCS51、PC硬件結(jié)構(gòu)對(duì)算法的影響,針對(duì)不同的算法來選擇DsP與編程語言,DSP常用算法簡介,DSP算法的仿真,DSP算法的移植與實(shí)現(xiàn)。

2020-09-16 17:49:00 17

17 本系統(tǒng)使用TI公司浮點(diǎn)型DSP TMS320C6713實(shí)現(xiàn)G.723.1等語音編解碼,為G.723.1、G.729等常用的低碼率語音壓縮標(biāo)準(zhǔn)提供運(yùn)行及測(cè)試硬件平臺(tái)。有別于大多數(shù)編解碼系統(tǒng),本設(shè)計(jì)采用

2020-09-21 09:58:07 3122

3122

結(jié)構(gòu)化LDPC碼可進(jìn)行相應(yīng)擴(kuò)展通過對(duì)編譯碼算法,優(yōu)化編譯碼結(jié)構(gòu)進(jìn)行調(diào)整,降低了編譯碼囂硬件實(shí)現(xiàn)中的關(guān)鍵路徑遲延,并采用Xilinx公司的Virtex一4 VLX80 FPGA芯片實(shí)現(xiàn)了一個(gè)碼長10 240,碼率1/2的非正則結(jié)構(gòu)化LDPC碼編碼器和譯碼器。實(shí)現(xiàn)結(jié)果表明:該編碼器信息吞吐量為1.878 Gb/

2021-03-26 15:58:00 12

12 基于軟件無線電的NRLDPC編譯碼設(shè)計(jì)與實(shí)現(xiàn)。

2021-05-28 10:07:04 5

5 DSP軟件編程與算法實(shí)現(xiàn)的過程說明。

2021-05-28 14:34:44 24

24 電子發(fā)燒友網(wǎng)站提供《基于VHDL語言的循環(huán)碼編譯碼系統(tǒng)的設(shè)計(jì).pdf》資料免費(fèi)下載

2023-10-13 14:31:37 1

1 電子發(fā)燒友網(wǎng)站提供《漢明碼編譯碼文檔.doc》資料免費(fèi)下載

2023-11-17 16:04:06 0

0

![]()

![]()

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論