深入理解AES算法的底層原理。

2017-10-26 14:40:07 45505

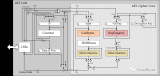

45505 AES加密算法流程圖如下圖所示: 明文P:未加密的原始數據;密鑰K:加密原始數據密碼,對稱算法中,加密與解密所需的密鑰相同,該密鑰不能直接進行傳輸,否則會造成密鑰泄露; 常規的做法是使用非對稱算法

2022-11-21 19:29:45 1858

1858

牢不可破。 AES加密核能同時用于FPGA核本身以及獨特 FlashROM (FROM) 內存的加密中。每個FPGA都被分成兩部分:FPGA陣列和FlashROM,兩者都可獨立編程,容許在不改

2019-07-09 09:11:44

AES算法包括哪些?AES算法的流程是怎樣的?AES 256算法是如何被破解的?

2021-11-12 07:56:55

本帖最后由 發燒友LV 于 2014-12-29 20:13 編輯

在FPGA中實現PID算法,面臨著小數的計算,請問大家一般是怎么處理的?

2014-12-03 21:59:29

設備替換功能是浩辰CAD電氣軟件中的一個基礎功能,此功能可以完成不同種類設備之間的相互替換。之前的CAD新手教程中給大家介紹了強電平面的設備替換功能使用技巧,那么你知道弱電平面設計中設備替換功能

2022-05-11 14:05:30

LT1963AES8

2023-03-28 13:19:59

1、M487芯片CRYPTO模塊中對稱加密AES功能測試本次測評主要測試新唐M487芯片CRYPTO模塊中對稱加密AES功能及其性能,性能方面會使用硬件加速和純軟件實現直接的效率差異。M487中

2022-04-22 17:52:48

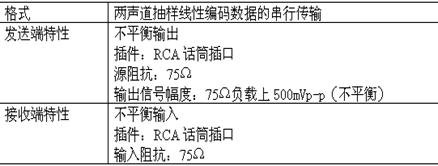

`廣播專業AES系列數字音頻光端機,采用先進的廣播和通信專業芯片。使用先進的FPGA、多路時分復用和時鐘恢復技術。輸入自動均衡,時鐘恢復,低抖動,透明傳輸完整AES格式信息。在1芯光纖上,傳輸10路

2011-03-13 22:54:43

正文 AES(Advanced Encryption Standard,高級加密標準)算法,是一種最常見的對稱加密算法。AES 在密碼學中又稱 Rijndael 加密法,是美國聯邦政府采用的一種區塊

2022-10-28 08:06:00

我從OpenCores下載了vhdl中的aes代碼但有些代碼我不明白這里的所有代碼aes_pkg.vhdl aes_enc.vhd key_expansion.vhdl aes_dec.vhd你

2019-02-21 11:13:01

字節傳輸的具體實現流程如圖 4-6 所示。圖 4-6 字節傳輸控制模塊流程圖字節傳輸控制模塊控制以字節為單位的數據傳輸。它根據命令寄存器的設置將數據傳輸寄存器中的內容傳輸到外部節點,將外部節點的數據

2018-10-10 10:34:14

。本方案以FPGA實現AES加密算法為目的,硬件角度加速AES加密。不知道這個方案有沒有吸引力,如果有的話就繼續寫設計方案了

2012-06-12 23:12:59

字節的數據。大多數的液晶顯示模塊HD44780的芯片或兼容的基礎上。提供一個良好的信息頁。【FPGA設計實例】FPGA接口實現文本液晶顯示模塊[hide] [/hide]`

2012-03-14 11:11:15

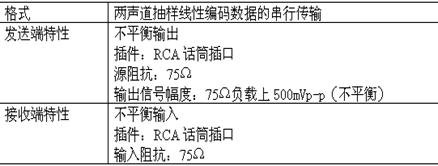

非常重要。通道狀態存儲器描述了在AES/EBU數據流通道中比特分配及其含義。例如的字節0的比 特0表示是家用級還是專業級,如果通道用于消費,字節0中比特0置0;用于專業時置1。奇偶校驗比特(P):通常為

2009-08-01 08:17:09

什么是AES算法?如何對AES算法進行優化?怎樣快速實現AES算法?

2021-04-28 06:51:19

本人想雇人用VHDL編寫一個用AES對一段文字或者圖像進行加密和解密。再實現的同時想看一下加密和解密所用的時間和速度。有哪位前輩有意,可以回復 價格再議。

2014-02-19 15:04:49

過程算不算是一種系統調用?在這篇博客中,我們會先簡單探究AES加解密的原理,然后對比ruby和golang的實現過程。產生的疑問在項目開發的過程中,我們時常會用戶會用到AES加解密, 但也僅僅是利...

2021-07-22 08:25:36

基于FPGA的可編程AES加解密IP

2021-01-21 07:39:11

嗨,我是一名本科生,也是使用FPGA套件的新手。在我的最后一個學期項目中,我使用Spartan 3A-3400 DSP套件實現AES,但我在查找AES-192和AES-256的verilog代碼

2019-09-11 11:24:58

在FPGA中遇到的一個疑難問題,求解答!我在Stratix II GX 中要實現這樣一個功能:用20M時鐘采集100路數據,然后將這些數據組成每字節10bit,每11字節一幀的數據,其中包括一個幀頭

2014-11-17 14:45:36

1、在FPGA中實現串口協議的設計在FPGA中實現串口協議,通過Anlogic_FPGA開發板上的“UART2USB”口接收從計算機發來的數據。實驗設計思路UART串口是一種類似于USB、VGA

2022-07-19 11:09:48

加密。庫中的示例代碼“aes”不在 ESP 上運行,因為它涉及源代碼中包含的一些 avr 庫,但我隔離了庫的主要加密和解密部分,并設法編譯和運行代碼。使用我的代碼,我能夠定義純文本字符串,使用預定

2023-02-27 09:21:41

如圖,在custom_aes函數中,得到的結果是一個128位的數據,但是C卻不能定義這么大的數據,從而只定義32位的變量來接收這個結果,但是只能接收到低位的32位,請教各位大神,有沒有什么方法可以實現呢?

2023-08-16 07:53:24

Programmable AES Encryption IP可編程AES加密IP可以集成到FPGA中,實現了AES(Advanced Encryption Standard) Rijndael加解密

2018-11-15 09:28:49

我在 S32K118 硬件上啟用了 Csec 模塊。上位機需要執行軟件AES128-CMAC算法,然后將CMAC值發送給ECU進行校驗。但是我不知道如何實現AES128-CMAC,你能給我一些建議嗎?

2023-05-04 08:06:21

大家好, 我使用Ultrascale Virtex Devices和Vivado工具, 在ASIC RAM中,ther是一個單獨的奇偶校驗寫使能位,但在FPGA RAM中沒有單獨的Pariaty寫使能位。 如何實現ASIC RAM奇偶校驗寫入啟用ino FPGA RAM。謝謝娜文G K.

2020-04-24 09:37:05

大家好,我正在研究Spartan 6(xc6slx45csg324-2)評估板,我正在嘗試從xapp1014實現AES3串行數字音頻接口。AES3輸入和輸出按照AES3-Spec中的規定連接。我

2019-08-08 10:03:48

美國國家標準與技術局(National Institute ofStandard and Technology,NIST)于1997年1月提出發展AES(Advanced Encryption

2019-08-06 06:19:10

為了系統的擴展性和構建良好的人機交互,如何利用FPGA的硬件描述語言來實現AES的加解密算法?

2021-04-08 06:01:05

如何去實現AES算法走D1芯片硬件CE模塊補丁呢?有哪些步驟?如何去測試?

2021-12-28 06:59:42

在FPGA中,動態相位調整(DPA)主要是實現LVDS接口接收時對時鐘和數據通道的相位補償,以達到正確接收的目的。那么該如何在低端FPGA中實現DPA的功能呢?

2021-04-08 06:47:08

這一樣本代碼展示了如何實施軟件AES(高級加密標準)以及AES加密/解密如何運作。

您可以在下列時間下載樣本代碼http://www.nuvoton.com/resources-downlo.1218180400。

nuvoton 核

2023-08-22 06:41:26

應用程序:示例代碼是進行 AES 加密和解密,將 AES 的私人密鑰儲存在 SPROM 中 。

BSP 版本:M480系列BSP CMSIS V3.03.001

硬件

2023-08-22 06:58:43

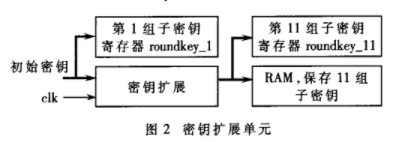

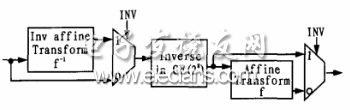

方面不支持64位操作,于是RC6修正這個錯誤,使用4個32位寄存器而不是2個64位寄存器,以更好地實現加解密。利用FPGA來實現RC6算法,可以提高運算速度。芯片設計為RC6算法處理器,輔助計算機處理器完成加解密操作,可以方便地實現對加解密的分析和研究。因此,此芯片可以作為協處理器來看待。

2019-08-19 07:27:09

目錄背景AES加密的幾種模式基本運算AES加密原理Matlab實現Verilog實現Testbench此文重點講述了AES加密算法的加密模式和原理,用MATLAB和Verilog進行加解密的實現。美

2021-07-28 07:34:30

V3.00.0003

硬件:NuMaker-M2354 VER1.1

M2354系列MCU具有超低功率消耗特征,并有一個適合具有安全通信的IoT裝置的加密加速器。

該示例代碼用于在 AES GCM 中

2023-08-29 07:05:28

請問matlab如何實現文本內容批量替換?

2021-11-19 08:08:53

如何使用Verilog硬件描述語言實現AES密碼算法?

2021-04-14 06:29:10

密鑰生成方案產生。大多數AES計算是在一個特別的有限域完成的。AES加密過程是在一個4×4的字節矩陣上運作,這個矩陣又稱為“狀態(state)”,其初值就是一個明文區塊(矩陣中一個元素大小就是明文區塊中

2016-08-12 11:58:43

,縮寫:AES),在密碼學中又稱Rijndael加密法,是美國聯邦***采用的一種區塊加密標準。這個標準用來替代原先的DES,已經被多方分析且廣為全世界所使用。經過五年的甄選流程,高級加密標準由美國

2016-07-09 17:24:33

接口:標準I2C協議接口算法: 標準AES256 / KAS算法特殊接口:Random Stream Cipher for Interface溫度: 工業級 -40°c ~ +85°c擦寫次數

2022-04-29 08:56:08

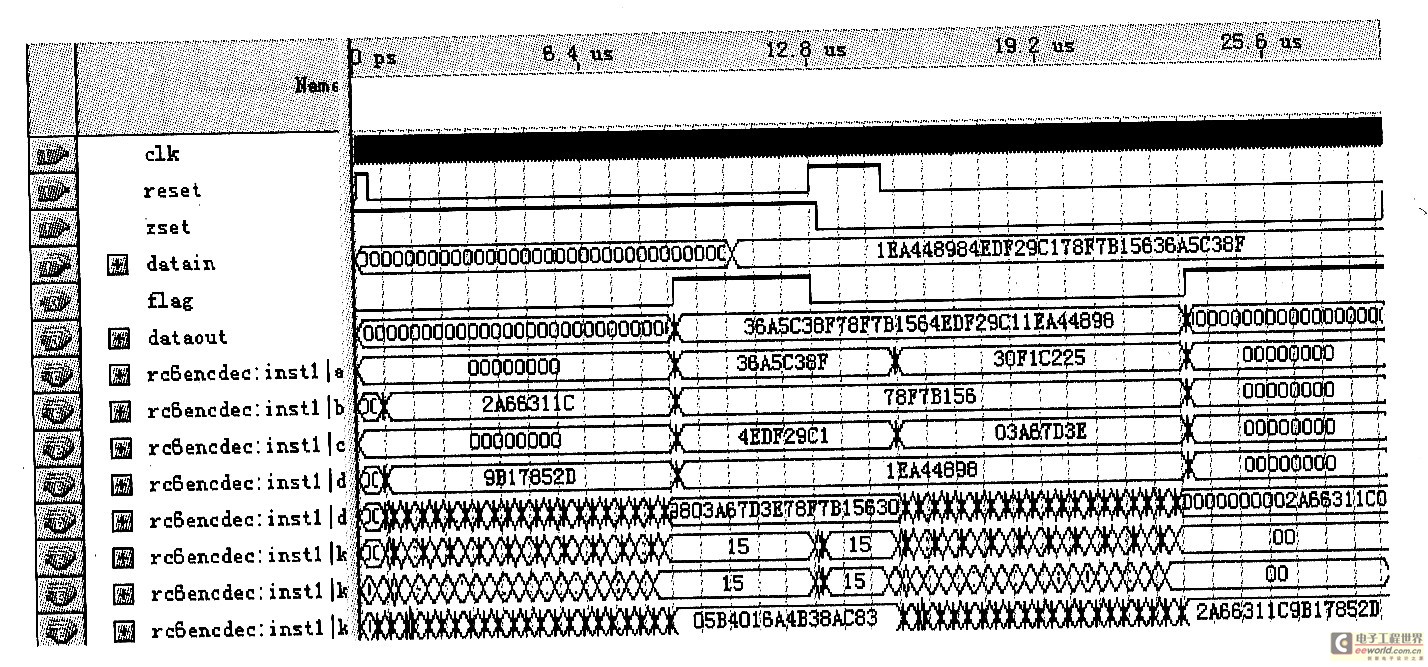

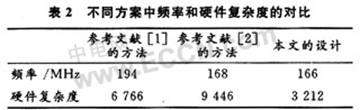

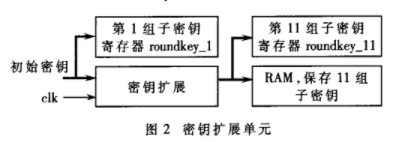

分析AES算法原理,構建基于FPGA的硬件實現框架,描述數據加解密單元和密鑰擴展單元的工作機制和硬件結構,引入核心運算模塊復用的設計思想,在不影響系統效率的前提下降低芯

2009-04-13 09:48:58 21

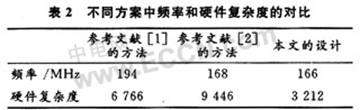

21 針對商業加密引擎中硬件資源和電路性能平衡問題,提出一種基于AES的低成本可重構的高速加密引擎的設計方案。該方案在AES加密算法的基礎上,根據FPGA內在的結構特點,利用VHDL語

2009-04-16 09:53:49 18

18 AES加密快速實現中利用了查表操作,查表的索引值會影響Cache命中率和加密時間,而查表的索引值和密鑰存在密切關系。通過分析AES最后一輪加密過程中查表索引值與密文和最后一輪

2009-04-18 09:42:35 32

32 本文提出了一種基于AES 實現的口令認證方法。該算法不使用公開密鑰算法,僅采用AES 進行遠程用戶的身份認證。該方法具有速度快,安全性高的特點,易于采用令牌(Token)或IC 卡

2009-08-05 10:43:03 14

14 本系統以AES 加密算法為例,使用Xilinx SPARTAN 3E 為開發平臺,以xilinx 的嵌入式軟核microblaze 為主控制器,調用FPGA 的硬件VHDL 編程實現的AES 加解密和控制CC2420 來實現高速有效的

2009-11-30 14:01:08 18

18 文章簡單的介紹了GPON 的體系結構與下行幀的結構,并著重介紹了AES 加密的流程、方法與具體算法,最后對GPON 中的AES 加密,解密方法,AES 計數器模式在GPON中的使用進行了詳細

2009-12-14 10:23:11 16

16 AES 算法是新一代加密標準算法,文中對OpenSSL 中AES 算法的基本原理和性能進行了分析,針對其速度慢的缺點,提出了一些改進AES 算法的策略,改進的算法能有效提高加密算法操

2009-12-25 16:06:32 12

12 用硬件實現數據加密已成為信息安全的主流方向。本文提出了一種基于FPGA 的低成本的AES IP核的實現方案。該方案輪內部系統資源共用,減少了系統資源的占用。輸入密鑰與輸入數據

2010-01-06 15:11:03 10

10 本文實現了一種基于AES 算法的無線加密數字傳輸系統,給出了該系統的結構,完成了AES 算法在FPGA 上的實現,將音頻接口集成到FPGA,并用GPRS 網絡進行音視頻等數據的實時傳

2010-01-22 15:09:39 5

5 介紹AES 算法的原理以及基于FPGA 的高速實現。結合算法和FPGA 的特點,采用查表法優化處理了字節代換運算、列混合運算。同時,為了提高系統工作速度,在設計中應用了內外結合

2010-01-25 14:26:51 29

29 介紹AES算法的原理以及基于FPGA的高速實現。結合算法和FPGA的特點,采用查表法優化處理了字節代換運算、列混合運算。同時,為了提高系統工作速度,在設計中應用了內外結合的流水線

2010-07-17 18:09:43 44

44 介紹了AES中,SubBytes算法在FPGA的具體實現.構造SubBytes的S-Box轉換表可以直接查找ROM表來實現.通過分析SubBytes算法得到一種可行性硬件邏輯電路,從而實現SubBytes變換的功能.

2010-11-09 16:42:48 25

25 AES/EBU接口標準

AES和EBU一起開發的數字音頻傳輸接口標準:AES/EBU標準,即AES3-1992,ANSI S4.40-1992,或IEC-958標準。它是傳輸和

2009-08-01 08:15:54 14734

14734

利用FPGA來實現RC6算法的設計與研究

引 言

RC6是作為AES(Advanced Encryption Standard)的候選算法提交給NIST(美國國家標準局)的一種新的分組密碼。它是在RC5的基礎上

2009-12-28 09:20:15 1022

1022

AES算法中S-box和列混合單元的優化及FPGA技術實現

由于其較高的保密級別,AES算法被用來替代DES和3-DES,以適應更為嚴苛的數

2010-04-23 09:34:22 2692

2692

本系統以AES加密算法為例,使用Xilinx SPARTAN 3E為開發平臺,以Xilinx的嵌入式軟核Microblaze為主控制器,調用FPGA的硬件VHDL編程實現的AES加解密和控制CC2420來實現高速有效的數據通信

2011-04-23 11:22:17 1477

1477

本文在分析AES加密算法原理的基礎上,著重說明算法的實現步驟,用C語言完整地實現了AES算法的加/解密操作,并在PVR機頂盒中實現應用。

2011-09-24 01:00:58 1831

1831

差分功耗分析是破解AES密碼算法最為有效的一種攻擊技術,為了防范這種攻擊技術本文基于FPGA搭建實驗平臺實現了對AES加密算法的DPA攻擊,在此基礎上通過掩碼技術對AES加密算法進行優

2011-12-05 14:14:31 52

52 基于AES的加密算法具有速度快、強度高、便于實現等優點和ECC加密算法具有密鑰分配與管理簡單、安全強度高等優點,采用AES加密算法加密大數據塊,而用ECC加密算法管理AES密鑰,通過

2012-03-20 10:24:39 42

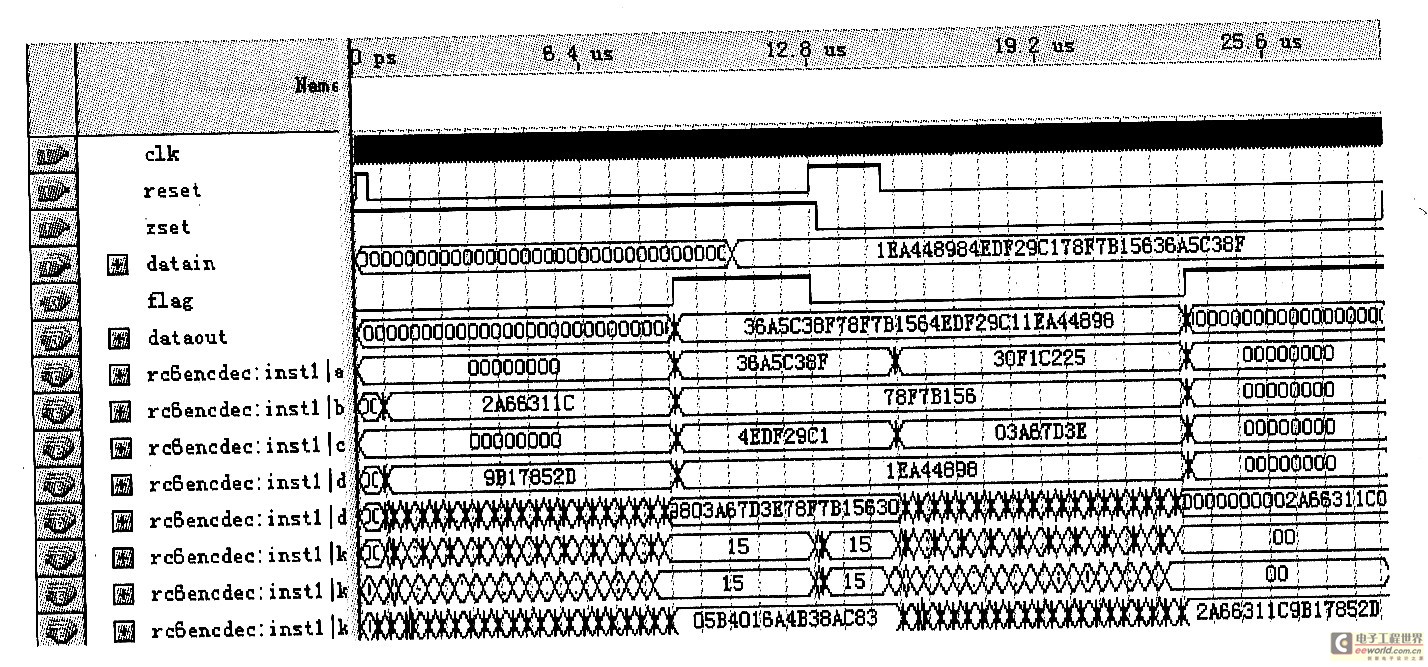

42 文中介紹了高級加密算法(AES)的基本原理,并給出了基于AES算法硬件加密模塊設計方案。通過Modelsim6.le對其進行仿真實現,仿真結果表明,該加密模塊能夠很好的實現AES算法

2013-02-21 15:52:41 0

0 基于AES加密算法的S盒優化設計_胡春燕

2017-03-19 11:31:31 2

2 AES是一種區塊加密標準算法,它的提出是為了升級替換原有的DES加密算法。因此它的安全強度高于DES算法。但不應片面理解,系統和數據的安全不僅與應用的加密算法有關,更與加密應用方案有關。和DES算法一樣,AES也屬于對稱加密算法,對密鑰的存儲與保護,直接決定了整個系統的安全。

2018-06-29 12:06:00 159716

159716 LORA6500AES 5w LORA AES加密無線數傳模塊 的資料

2017-09-05 17:46:49 26

26 介紹了AES加密標準的Rijndael實現方法,設計了一種適合應用于嵌入式系統32位數據界面時序緊湊的AES加密IP核。該IP核能以較低的資源消耗實現在低端FPGA上速度為256Mb/s的AES加密,且可將數據位寬擴展為64位或128位等,滿足多種數據位寬應用的要求。

2017-09-07 19:14:58 13

13 根據AES算法的特點,從3方面對算法硬件實現進行改進:列混合部分使用查找表代替矩陣變換,降低算法實現的運算復雜度,采用流水線結構優化關鍵路徑一密鑰拓展,提升加密速度,利用FPGA定制RAM

2017-11-02 10:59:59 0

0 CC2541是一款基于BLE開發的芯片,該芯片白帶的AES協處理器(AES Coproc:essor)可以實現CBC、CFB、OFB、CTR、ECB、CBC MAC等多種加密解密算法。TI官方提供

2017-11-08 14:15:20 33

33 一種AES算法實現是采用輪展開的流水線結構,吞吐量很大可達到10 Gb/s量級,但消耗大量的邏輯面積。考慮在資源少的FPGA上實現AES算法,能滿足低端應用的加、解密速度一般不超過100Mb

2017-11-23 11:38:20 2643

2643 1 引 言 AES加密算法的一種優化的FPGA實現方法 隨著密碼分析水平,芯片處理能力和計算技術的不斷進步,des的安全強度已經難以適應新的安全需要,其實現速度、代碼大小和跨平臺性均難以繼續滿足

2017-11-30 01:31:26 1789

1789 由于對廣泛使用的AES算法的性能要求越來越高,基于軟件的密碼算法已經越來越難以滿足高吞吐量密碼破解的需求,因此越來越多的算法利用現場可編程邏輯門陣列( FPGA)平臺進行加速。針對AES算法

2017-12-03 09:49:02 7

7 的DES,已經被多方分析且廣為全世界所使用。本壓縮文件中對于AES的各個步驟分別打包為FUNCTION,便于查找。實現語言為matlab。

2018-05-25 15:18:19 11

11 FPGA 進行物理加密具有很好的防攻擊性,實時性好, 可實現高速數據處理,資源占用非常小,是空間數據加密的重要發展方向。

2018-12-30 09:31:00 5156

5156

AES算法作為DES算法的替代者應用非常廣泛,其硬件實現方法已有不少討論,主要是通過提高算法頻率來提高吞吐量。但是在實際運行中,為了保證整個加密系統的穩定性,通常全局時鐘頻率較低,不可能達到算法的仿真頻率,如PCI接口電路時鐘頻率只有33MHz,因此實際數據吞吐量仍然較低。

2019-04-18 08:15:00 3057

3057

idkt是一個高性能的安全存儲設備系列,提供2k字節的用戶內存,具有先進的內置aes 256安全引擎和加密功能。存儲器被分為8個用戶區,每個用戶區分別設置不同的安全訪問權限,或者一起使用為一個或多個數據文件提供空間。配置區域包含用于定義idkt全局安全ic的安全邏輯所使用的aes256密鑰的寄存器。

2019-10-22 16:53:13 12

12 是用一個單元數據替換另一個。AES使用了如下幾種不同的技術來實現置換和替換。字節替代(SubBytes):通過非線性的替換函數,用查找表的方式把分組的字節矩陣中的每個字節用同一個S-BOX替換成另外一個字節

2019-12-06 21:57:54 6425

6425 AES算法的主要數學基礎是抽象代數,其中算法中的許多運算是按單字節(8bits)和4字節(32bits)定義的,單字節可看成有限域GF(2)中的一個元素,而4字節則可以看成系數在GF(2)中并且次數

2020-01-17 14:19:00 16

16 Rijndael算法為高級加密標準AES。AES密碼算法的加密速度快,安全級別高,已經成為加密各種形式的電子數據的實際標準。目前,針對AES密碼算法的加密技術已成為研究熱點。論文提出了一種低成本的AES密碼算法的硬件實現方法,并且使用FPGA器件實現了具體的設

2020-03-19 17:16:22 6

6 美國國家標準技術局(NIST)于2001年發布高級加密標準(AES),用來取代DES,從而成為廣泛使用的對稱分組加密標準。針對AES的硬件實現人們做了許多有意義的研究工作,有的著力于采用流水線結構

2020-04-20 17:59:03 10

10 實現,經過仿真并在Xilinx Spartan 3系列FPGA上進行綜合驗證,可以將結構簡化,使AES電路面積得到優化,明顯節約硬件資源。

2021-01-25 14:27:14 19

19 通過將AES算法模塊化、運算一般化,給出了類AES算法的統一框架。在此框架下不僅可以同時實現AES的加密、解密,而且可以通過外部參數動態設定分組算法,使得密碼算法的使用更加靈活、安全。給出了算法的FPGA實現。結果表明設計方案可行,速度較高。

2021-03-26 15:58:04 16

16 基于FPGA的AES算法中S-box和列混合單元優化

2021-06-08 10:52:39 7

7 密鑰的未知字節長度。結合注入故障后輸出的錯誤密文,可通過窮舉猜測的方式恢復初始密鑰未知字節。攻擊測試結果表明,通過該方法執行一次有效故障注入攻擊能得到4字節長度初始密鑰,即對于128位AES算法,攻擊者僅需猜測4×23次就

2021-06-08 14:16:35 4

4 /UltraLite家族、iCE40UltraPlus家族全型號器件詳情鏈接:FPGA.EQ6GL9小型低功耗百萬門級FPGA替換XILINX/賽靈思:XC6SLX4、XC6S

2022-03-02 09:26:57 5428

5428

本文檔介紹了AES 硬件 IP 功能。高級加密標準 (AES) 是 OpenTitan 協議中使用的主要對稱加密和解密機制。 AES 單元是一個加密加速器,它接受來自處理器的請求以加密或解密 16 字節的數據塊。它作為外設模塊連接到芯片互連總線,符合外設功能的要求指南。

2023-08-03 10:46:50 442

442

電子發燒友網站提供《在Virtex-6 FPGA中使用全數字VCXO替換技術實現三倍速率SDI直通.pdf》資料免費下載

2023-09-14 14:52:17 3

3

電子發燒友App

電子發燒友App

評論