在過去兩年里,用于消除IC、電路板和系統(tǒng)之間數(shù)據(jù)傳輸瓶頸的接口標(biāo)準(zhǔn)層出不窮,本文將考評通信應(yīng)用標(biāo)準(zhǔn)部件的某些最流行的標(biāo)準(zhǔn),并研究眾多新標(biāo)準(zhǔn)出現(xiàn)的原因,此外還探討設(shè)計者可如何解決互用性的難題。

新興接口標(biāo)準(zhǔn)綜述

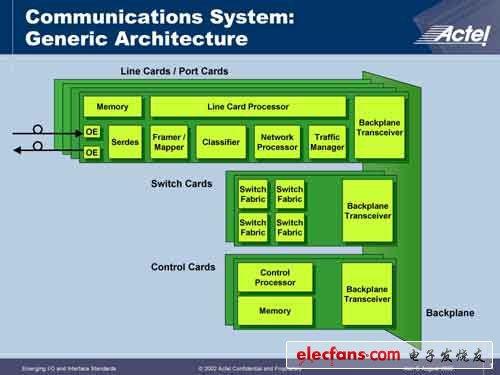

如果查看一下典型通信系統(tǒng)的結(jié)構(gòu)(見圖),可以看出很多元件都需要相互進行通信。為滿足數(shù)據(jù)通道中各種元件的不同需求,因而出現(xiàn)了各種不同的接口標(biāo)準(zhǔn)。要了解各種接口的優(yōu)缺點,就需要查看元件本身及每個元件所發(fā)生的通信類型。這里將從光電接口開始,然后逐一介紹內(nèi)部元件,直至交換架構(gòu)(switch fabric)。

圖1 型通信系統(tǒng)的結(jié)構(gòu)

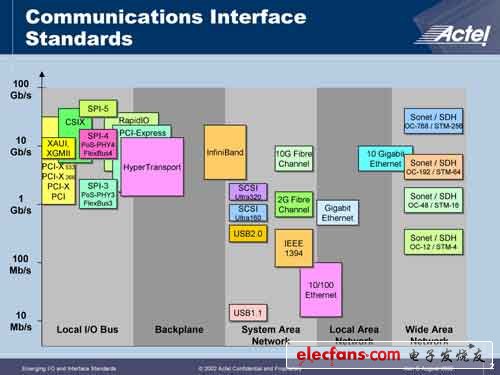

在高速光纖通信系統(tǒng)中,傳輸?shù)臄?shù)據(jù)流需要進行格式轉(zhuǎn)換,即在光纖傳輸時的串行格式及在電子處理時的并行格式之間轉(zhuǎn)換。串化器-解串器 (一般被稱作串并行轉(zhuǎn)換器) 就是用來實現(xiàn)這種轉(zhuǎn)換的。串并行轉(zhuǎn)換器與光電傳感器間的接口通常為高速串行數(shù)據(jù)流,利用一種編碼方案實現(xiàn)不同信令,這樣可從數(shù)據(jù)恢復(fù)嵌入的時鐘。視乎所支持的通信標(biāo)準(zhǔn),該串行流可在1.25Gb/s (千兆以太網(wǎng))、2.488Gb/s (OC-48 / STM-16)、9.953Gb/s (OC-192 / STM-64) 或10.3Gb/s (10千兆以太網(wǎng))條件下傳輸。

b.串并行轉(zhuǎn)換器至成幀器接口

在Sonet / SDH的世界中,光纖中的數(shù)據(jù)傳輸往往采用幀的形式。每幀包括附加信息(用于同步、誤差監(jiān)視、保護切換等)和有效載荷數(shù)據(jù)。傳輸設(shè)備必須在輸出數(shù)據(jù)中加入幀的附加信息,接收設(shè)備則必須從幀中提取有效載荷數(shù)據(jù),并用幀的附加信息進行系統(tǒng)管理。這些操作都會在成幀器中完成。

由于成幀器需要實現(xiàn)某些復(fù)雜的數(shù)字邏輯,因而決定了串并行轉(zhuǎn)換器與成幀器間所用的接口技術(shù),采用標(biāo)準(zhǔn)CMOS工藝制造的高集成度IC。目前的CMOS工藝不能支持10Gb/s串行數(shù)據(jù)流(盡管很多人認(rèn)為未來的CMOS工藝可以實現(xiàn)此項功能),因此串并行轉(zhuǎn)換器與成幀器間需要并行接口。目前最流行的選擇是由光網(wǎng)絡(luò)互聯(lián)論壇 (Optical Internetworking Forum) 開發(fā)的SFI-4,該接口使用兩個速度達622Mb/s的16位并行數(shù)據(jù)流(每個方向一個)。SFI-4與目前很多新興接口一樣,使用源同步時鐘,即時鐘信號與數(shù)據(jù)信號共同由傳輸器件傳輸。源同步時鐘可顯著降低時鐘信號與數(shù)據(jù)信號間的偏移,但它不能完全消除不匹配PCB線路長度引起的偏移效應(yīng)。16個數(shù)據(jù)信號和時鐘信號均使用IEEE-1593.6標(biāo)準(zhǔn)LVDS信令。該接口僅需在串并行轉(zhuǎn)換器與成幀器間來回傳輸數(shù)據(jù),距離較短,因此無需具備復(fù)雜的流控制或誤差檢測功能。

以太網(wǎng)中也存在類似接口。在10千兆以太網(wǎng)PHY的物理編碼子層(PCS)與物理介質(zhì)連接(PMA)層之間,IEEE-802.3ae規(guī)范提供了一種被稱作XSBI的接口。這種"10千兆16位接口"在每個方向都具有16位并行數(shù)據(jù)流及源同步時鐘。數(shù)據(jù)和時鐘均使用IEEE-1593.6標(biāo)準(zhǔn)LVDS信令。數(shù)據(jù)通道使用64b/66b編碼方案,其時鐘頻率為644MHz。

該10千兆以太網(wǎng)規(guī)范使用串行接口連接MAC(介質(zhì)訪問控制)層和PHY(物理)層。這個被稱作XAUI的接口,也被稱為"10千兆連接單元接口",這是一種使用四通道的串行接口,每個通道傳輸2.5Gb/s有效載荷數(shù)據(jù),8b/10b編碼使每個通道

的比特率高達 3.125Gb/s。該接口一般用于連接MAC和包含PHY及光器件的獨立模塊。根據(jù)幾家制造商的多源協(xié)議開發(fā)的Xenpak光模塊使用XAUI接口。后文還將提到XAUI也用于系統(tǒng)背板。

c.成幀器與網(wǎng)絡(luò)處理器及其它元件間的接口

成幀器與網(wǎng)絡(luò)處理間傳輸?shù)臄?shù)據(jù)可代表很多不同的數(shù)據(jù)流。Sonet/SDH幀中包含的附加數(shù)據(jù)表明數(shù)據(jù)有效載荷中每個數(shù)據(jù)流的位置,該信息需要在成幀器與網(wǎng)絡(luò)處理器及相關(guān)器件間傳輸,如分類引擎和流量管理器。此外,網(wǎng)絡(luò)處理器和相關(guān)器件還實現(xiàn)各種復(fù)雜的任務(wù),如數(shù)據(jù)包傳向交換芯片的時序安排,管理數(shù)據(jù)包內(nèi)容以確保沒有非法數(shù)據(jù)進入網(wǎng)絡(luò),以及測量帶寬以便特定應(yīng)用或用戶享有優(yōu)先權(quán)。由于這些任務(wù)很復(fù)雜,因此需要在成幀器與網(wǎng)絡(luò)處理器間實施流控制方案。

成幀器、網(wǎng)絡(luò)處理器與相關(guān)器件間通常使用的接口包括Utopia接口、POS-PHY接口、SPI接口和Flexbus接口。每個接口的后綴為 "level X",其級別表明標(biāo)稱數(shù)據(jù)速率。Level 2即指每個方向的數(shù)據(jù)速率為622Mb/s,Level 3為2.488Gb/s,level 4為9.953Gb/s,Level 5為39.8Gb/s。因此POS-PHY Level 4的標(biāo)稱帶寬為9.953Gb/s。Utopia接口是為包含固定長度ATM單元的數(shù)據(jù)流而設(shè)計的。Utopia的規(guī)范由ATM論壇頒布。

POS-PHY接口 (Sonet物理層上的包) 由PMC-Sierra和Saturn開發(fā),很多特性與Utopia接口相同,有一項改進功能值得注意,即POS-PHY能滿足不同長度數(shù)據(jù)包的需要,而 Utopia只適用于固定單元長度。這表明POS-PHY接口是為無需ATM層,即可在Sonet/SDH傳輸層上直接傳輸長度變化的IP包的應(yīng)用而設(shè)計的,因此被稱作"Sonet上的數(shù)據(jù)包"。

Flexbus接口由AMCC開發(fā),可處理Sonet傳輸層上的變長度IP包。AMCC的Flexbus Level 4已獲光網(wǎng)絡(luò)互聯(lián)論壇采納,作為SPI Level 4 Phase 1(一般縮寫為"SPI-4.1"),并已經(jīng)作為業(yè)界標(biāo)準(zhǔn)規(guī)范發(fā)布。該規(guī)范在每個方向上提供64位并行點至點數(shù)據(jù)通道,它使用HSTL class 1 I/O,源同步時鐘頻率為200MHz,還提供四分之一速率接口和16位并行數(shù)據(jù)通道。

POS-PHY Level 4也已經(jīng)被光網(wǎng)絡(luò)互聯(lián)論壇采納,命名為SPI Level 4 Phase 2 (通常縮寫為"SPI-4.2")。該接口具有采用IEEE-1593.6標(biāo)準(zhǔn)LVDS的16位并行數(shù)據(jù)通道,源同步雙數(shù)據(jù)速率時鐘頻率最小為 311MHz。SPI-4.2的許多應(yīng)用則使用頻率更高的時鐘,因為該接口除了傳輸數(shù)據(jù)有效載荷外,還傳送包標(biāo)簽和路由信息。因此,設(shè)計者常常采用 SPI-4.2,每個信號對的數(shù)據(jù)速率高達840Mb/s,每個方向的累計帶寬可達13.4Gb/s。

盡管SPI-4.2是為Sonet上數(shù)據(jù)包而開發(fā),它已被通信業(yè)的其它應(yīng)用所采納。作為能支持多數(shù)據(jù)流而且每個數(shù)據(jù)流中都具有流控制的靈活接口,它可用作 10G以太網(wǎng)的有效接口,還可用于存儲區(qū)域網(wǎng)絡(luò)(SAN)。目前市場上有各種采用SPI-4.2接口的新產(chǎn)品,還有一些產(chǎn)品正在開發(fā)之中,除了Sonet / SDH成幀器和網(wǎng)絡(luò)處理器,還包括TCP 卸載引擎(TOE)和10G以太網(wǎng)MAC。

d.網(wǎng)絡(luò)處理器與交換架構(gòu)間的接口

網(wǎng)絡(luò)處理器與相關(guān)器件及交換架構(gòu)間的接口有兩種類型:一類為不需要在背板傳輸數(shù)據(jù)的接口,另一類為需要在背板傳輸數(shù)據(jù)的接口。

對于第一種接口,位于同一塊電路板的網(wǎng)絡(luò)處理器芯片組和交換架構(gòu)間的接口可用CSIX Level 1接口實現(xiàn)。該接口采用CSIX Level 1包格式,包括為交換架構(gòu)提供路由指令的報頭,以及用于誤差檢測及糾正的報尾,還包括數(shù)據(jù)載荷本身。控制CSIX規(guī)范的網(wǎng)絡(luò)處理器論壇將進一步完善該規(guī)范,增加從一個NPU芯片組通過交換芯片傳至另個NPU芯片的額外指令。這將成為CSIX Level 2規(guī)范的最主要推進力。該規(guī)范還定義了每個方向中使用至多128個HSTL一類I/O的電氣互連,其源同步時鐘頻率高達250MHz。CSIX Level 1協(xié)議與CSIX Level 1電氣規(guī)范無關(guān),無論NPU芯片組和交換架構(gòu)間的經(jīng)由背板的通信采用何種電氣標(biāo)準(zhǔn),仍可使用CSIX Level 1協(xié)議。

對于第二種接口,即NPU芯片組與交換架構(gòu)間需要在通過背板通信,仍然可以使用CSIX Level 1協(xié)議,但這種電氣接口并不合適。信號將穿過連接器,從端口卡到達系統(tǒng)背板,經(jīng)過數(shù)英寸到達另一個連接器,然后進入交換卡。有諸多原因使得越來越多的設(shè)計者選擇具有嵌入式時鐘的串行接口來實現(xiàn)這些連接。首先,串行接口可最大限度地減少電路板與背板連接器的引腳數(shù),從而可減小插拔力及對操作系統(tǒng)中電路板的可能損害。其二,在信號中嵌入時鐘和數(shù)據(jù)的串行接口可完全避免時鐘偏移問題。時鐘偏移是PCB中數(shù)英寸長的并口所面臨的主要問題。其三,串行信號的背板設(shè)計者還可提高傳輸速率,因為不存在時鐘偏移,也就沒有對未來性能的限制。

被成功用作串行背板標(biāo)準(zhǔn)的接口是XAUI,它是為10千兆以太網(wǎng)開發(fā)的。該規(guī)范適用于通道排列電路,無論四通道軌線長度是否匹配,符合XAUI的器件均能接收無誤差數(shù)據(jù)。該接口使用差分電流模式邏輯信令,它還采用交流耦合模式,允許電路板間的參考電壓不同。

e.控制板接口

目前本文所提到的接口都用于"數(shù)據(jù)通道",即數(shù)據(jù)從光纖傳輸介質(zhì)到達交換架構(gòu),然后返回光纖通道。但由于通信系統(tǒng)具有復(fù)雜的"控制板",負責(zé)統(tǒng)計數(shù)據(jù)收集、流量監(jiān)視、系統(tǒng)管理及維護等功能,因此需要強大的處理能力運行軟件以實現(xiàn)這些功能。這些構(gòu)建控制板處理器的接口正如設(shè)想的那樣,與數(shù)據(jù)通道的接口明顯不同。數(shù)據(jù)通道接口主要用于在兩個器件間傳輸數(shù)據(jù)(即點對點鏈接),控制板接口則是與具有不同元件的一個或多個微處理器相連接: 背板收發(fā)器、DSP、數(shù)據(jù)板器件的控制端口等。實現(xiàn)這些靈活的互連需要完全不同類型的接口。

這類系統(tǒng)過去都是圍繞多點復(fù)接的中心總線構(gòu)建的。實現(xiàn)PCI總線架構(gòu)的32位/ 33MHz及最近采用的64位/ 66MHz標(biāo)準(zhǔn)已經(jīng)用于通信系統(tǒng)中。最近64位/ 133MHz PCI-X更用于高端服務(wù)器。但是,由于數(shù)據(jù)板處理的帶寬已經(jīng)增加,控制板的帶寬也要提高。很多設(shè)計者發(fā)現(xiàn)共享總線帶寬不足以滿足多個器件的需求。因此, 出現(xiàn)一類新型接口。

這類新接口采用點至點連接,用源同步時鐘減少時鐘偏移。差分信令可提高數(shù)據(jù)傳輸率,減少交換噪聲和功耗。但真正的創(chuàng)新在于使用交換架構(gòu)或通道器件,實現(xiàn)控制應(yīng)用中所需的多點互連。 已獲得Motorola及RapidIO貿(mào)易聯(lián)合會支持的RapidIO是使用交換架構(gòu)實現(xiàn)點至點鏈接的接口。該接口的傳輸層規(guī)定數(shù)據(jù)如何封裝在包中,每個包都具有數(shù)據(jù)源和目標(biāo)信息,交換架構(gòu)將數(shù)據(jù)包送往合適的目的地。RapidIO在每個方向上提供8個或16個位,采用250MHz至1.0GHz雙數(shù)據(jù)速率。此外,串行RapidIO可使用具有8b/10b編碼的1通道或4通道數(shù)據(jù),嵌入時鐘達3.125Gb/s,它還具有CML差分信令。 Motorola已經(jīng)推出幾種使用并行RapidIO的通信處理器。

AMD及HyperTransport聯(lián)盟開發(fā)的HyperTransport使用通道器件實現(xiàn)點至點鏈接。數(shù)據(jù)以包的形式傳輸,每個包均包括數(shù)據(jù)源和目標(biāo)信息。接收數(shù)據(jù)的通道器件按照數(shù)據(jù)包報頭確定是將數(shù)據(jù)傳至鏈中的下一個器件,還是直接處理數(shù)據(jù)。目前的HyperTransport規(guī)范需要寬度為2至 16位的并行數(shù)據(jù)。未來規(guī)范可支持更高速率。PMC-Sierra和Broadcom已經(jīng)為HyperTransport通信產(chǎn)品推出基于MIPS的處理器。PCI-SIG已經(jīng)推出高速率PCI-X。它們使用與最初PCI-X相同的64位總線帶寬,可支持雙數(shù)據(jù)速率和四倍數(shù)據(jù)速率。PCI-X 533是速率最快的版本,最大總計帶寬達34.1Gb/s。

解決接口沖突

設(shè)計工程師如何面對這些紛繁蕪雜的接口標(biāo)準(zhǔn)。實際上,對于給定的設(shè)計情況,設(shè)計者選擇接口的余地并不大。他們一般根據(jù)系統(tǒng)所需的成本及功能,選擇合適的標(biāo)準(zhǔn)產(chǎn)品。設(shè)計者必須選擇最合適的器件。但這可能導(dǎo)致接口標(biāo)準(zhǔn)沖突,因為最好的標(biāo)準(zhǔn)器件由于接口標(biāo)準(zhǔn)不兼容,會引起互用性問題。在這種情況下,設(shè)計者可如此選擇:重新選擇與接口兼容的標(biāo)準(zhǔn)器件,但可能會造成不能滿足功能需要或系統(tǒng)的成本要求,或者使用橋接器件避開不兼容的接口。現(xiàn)在已經(jīng)推出很多具有高性能接口IP及高速物理I/O的FPGA,可滿足10Gb/s以上數(shù)據(jù)通道的通信系統(tǒng)的要求。

Actel正在開發(fā)各種可編程邏輯器件,結(jié)合高級接口技術(shù)和最新推出的Axcelerator系列高速FPGA架構(gòu)。首款產(chǎn)品將具有速率高達 3.125Gb/s的集成串并行轉(zhuǎn)換器通道和硬連線物理編碼子層,它們能自動處理XAUI和串行RapidIO所需的8b/10b編碼和通道排列。這些器件還具有實現(xiàn)LVDS信令的高速通用I/O,可交互使用SPI-4.2、HyperTransport和并行RapidIO等接口標(biāo)準(zhǔn)。這些器件還將集成各種知識產(chǎn)權(quán)內(nèi)核,以便應(yīng)用于要求苛刻的橋接產(chǎn)品。??

電子發(fā)燒友App

電子發(fā)燒友App

評論