在制程進(jìn)入深次微米世代之后,晶片(IC)設(shè)計(jì)的高復(fù)雜度及系統(tǒng)單晶片(SOC)設(shè)計(jì)方式興起。此一趨勢(shì)使得如何確保IC品質(zhì)成為今日所有設(shè)計(jì)從業(yè)人員不得不面臨之重大課題。靜態(tài)時(shí)序分析(Static Timing Analysis簡(jiǎn)稱STA)經(jīng)由完整的分析方式判斷IC是否能夠在使用者的時(shí)序環(huán)境下正常工作,對(duì)確保IC品質(zhì)之課題,提供一個(gè)不錯(cuò)的解決方案。然而,對(duì)于許多IC設(shè)計(jì)者而言,STA是個(gè)既熟悉卻又陌生的名詞。本文將力求以簡(jiǎn)單敘述及圖例說(shuō)明的方式,對(duì)STA的基礎(chǔ)概念及其在IC設(shè)計(jì)流程中的應(yīng)用做詳盡的介紹。

什么是STA?

STA的簡(jiǎn)單定義如下:套用特定的時(shí)序模型(Timing Model),針對(duì)特定電路分析其是否違反設(shè)計(jì)者給定的時(shí)序限制(Timing Constraint)。以分析的方式區(qū)分,可分為Path-Based及Block-Based兩種。

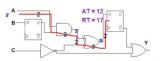

先來(lái)看看Path-Based這種分析方式。如圖一所示,訊號(hào)從A點(diǎn)及B點(diǎn)輸入,經(jīng)由4個(gè)邏輯閘組成的電路到達(dá)輸出Y 點(diǎn)。套用的Timing Model標(biāo)示在各邏輯閘上,對(duì)于所有輸入端到輸出端都可以找到相對(duì)應(yīng)的延遲時(shí)間。而使用者給定的Timing Constraint為:

訊號(hào)A到達(dá)電路輸入端的時(shí)間點(diǎn)為2(AT=2,AT為Arrival Time)。

訊號(hào)B到達(dá)電路輸入端的時(shí)間點(diǎn)為5(AT=5)。

訊號(hào)必須在時(shí)間點(diǎn)10之前到達(dá)輸出端Y(RT=10,RT為Required Time)。

現(xiàn)在我們針對(duì)P1及P2兩條路徑(Path)來(lái)做分析。P1的起始點(diǎn)為A,訊號(hào)到達(dá)時(shí)間點(diǎn)為2。經(jīng)過(guò)第1個(gè)邏輯閘之后,由于此閘有2單位的延遲時(shí)間,所以訊號(hào)到達(dá)此閘輸出的時(shí)間點(diǎn)為4(2+2)。依此類推,訊號(hào)經(jīng)由P1到達(dá)輸出Y的時(shí)間點(diǎn)為7(2+2+3)。在和上述第三項(xiàng)Timing Constraint比對(duì)之后,我們可以得知對(duì)P1這個(gè)路徑而言,時(shí)序(Timing)是滿足使用者要求的。

按照同樣的方式可以得到訊號(hào)經(jīng)由路徑B到達(dá)輸出Y的時(shí)間點(diǎn)為11(5+1+3+2),照樣和上述第三項(xiàng)Timing Constraint比對(duì),我們可以得知對(duì)P2這個(gè)路徑而言,Timing是不滿足使用者要求的。

對(duì)圖一的設(shè)計(jì)而言,總共有6個(gè)訊號(hào)路徑。對(duì)于采用Path-Based分析方式的STA軟體來(lái)說(shuō),它會(huì)對(duì)這6個(gè)訊號(hào)路徑作逐一的分析,然后記錄下結(jié)果。IC設(shè)計(jì)者藉由檢視其分析報(bào)告的方式來(lái)判斷所設(shè)計(jì)的電路是否符合給定的Timing Constraint。由于最常用來(lái)做靜態(tài)時(shí)序分析驗(yàn)證核可(STA Signoff)的EDA軟體PrimeTime?采用Path-Based的分析方式,所以本文將以Path-Based的分析方式介紹為主。

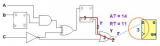

再來(lái)看看Block-Based的分析方式。此時(shí)時(shí)序資訊(Timing Information)的儲(chǔ)存不再是以路徑為單位,而是以電路節(jié)點(diǎn)(Node)為單位。由Timing Constraint我們僅能得知A節(jié)點(diǎn)的AT為2,B節(jié)點(diǎn)的AT為5以及Y節(jié)點(diǎn)的RT為10。Block-Based的分析方式會(huì)找出每個(gè)節(jié)點(diǎn)的AT和 RT,然后比對(duì)這兩個(gè)數(shù)值。當(dāng)RT的值大于AT時(shí)表示訊號(hào)比Timing Constrain中要求的時(shí)間還早到達(dá),如此則Timing是滿足的,反之則不滿足。

STA資料準(zhǔn)備

在做STA之前,我們必須對(duì)其準(zhǔn)備工作有充分的了解。STA所需的資料如圖三所示,以下我們分項(xiàng)說(shuō)明。其中Design Data部分,由于Block Model和STA軟體相關(guān)性太高,我們不在此加以說(shuō)明,請(qǐng)直接參閱您STA軟體的使用手冊(cè)。

Library Data:

STA所需要的Timing Model就存放在標(biāo)準(zhǔn)元件庫(kù)(Cell Library)中。這些必要的時(shí)序資訊是以Timing Arc的方式呈現(xiàn)在標(biāo)準(zhǔn)元件庫(kù)中。Timing Arc定義邏輯閘任兩個(gè)端點(diǎn)之間的時(shí)序關(guān)系,其種類有Combinational Timing Arc、Setup Timing Arc、Hold Timing Arc、Edge Timing Arc、Preset and Clear Timing Arc、Recovery Timing Arc、Removal Timing Arc、Three State Enable & Disable Timing Arc、Width Timing Arc。其中第1、4、5、8項(xiàng)定義時(shí)序延遲,其他各項(xiàng)則是定義時(shí)序檢查。

?

Combinational Timing Arc是最基本的Timing Arc。Timing Arc如果不特別宣告的話,就是屬于此類。如圖四所示,他定義了從特定輸入到特定輸出(A到Z)的延遲時(shí)間。Combinational Timing Arc的Sense有三種,分別是inverting(或 negative unate),non-inverting(或 positive unate)以及non-unate。當(dāng)Timing Arc相關(guān)之特定輸出(圖四Z)訊號(hào)變化方向和特定輸入(圖四A)訊號(hào)變化方向相反(如輸入由0變1,輸出由1變0),則此Timing Arc為inverting sense。反之,輸出輸入訊號(hào)變化方向一致的話,則此Timing Arc為non-inverting sense。當(dāng)特定輸出無(wú)法由特定輸入單獨(dú)決定時(shí),此Timing Arc為non-unate。

圖七

圖八

圖九

圖十

圖十一

圖十二

其他的Timing Arc說(shuō)明如下。

Setup Timing Arc:定義序向元件(Sequential Cell,如Flip-Flop、Latch等)所需的Setup Time,依據(jù)Clock上升或下降分為2類(圖五)。

Hold Timing Arc:定義序向元件所需的Hold Time,依據(jù)Clock上升或下降分為2類(圖六)。

Edge Timing Arc:定義序向元件Clock Active Edge到資料輸出的延遲時(shí)間,依據(jù)Clock上升或下降分為2類(圖七)。

Preset and Clear Timing Arc:定義序向元件清除訊號(hào)(Preset或Clear)發(fā)生后,資料被清除的速度,依據(jù)清除訊號(hào)上升或下降及是Preset或Clear分為4類(圖八)。這個(gè)Timing Arc通常會(huì)被取消掉,因?yàn)樗鼤?huì)造成訊號(hào)路徑產(chǎn)生回路,這對(duì)STA而言是不允許的。

Recovery Timing Arc:定義序向元件Clock Active Edge之前,清除訊號(hào)不準(zhǔn)啟動(dòng)的時(shí)間,依據(jù)Clock上升或下降分為2類(圖九)。

Removal Timing Arc:定義序向元件Clock Active Edge之后,清除訊號(hào)不準(zhǔn)啟動(dòng)的時(shí)間,依據(jù)Clock上升或下降分為2類(圖十)。

Three State Enable & Disable Timing Arc:定義Tri-State元件致能訊號(hào)(Enable)到輸出的延遲時(shí)間,依據(jù)Enable或Disable分為2類。(圖十一)

Width Timing Arc:定義訊號(hào)需維持穩(wěn)定的最短時(shí)間,依據(jù)訊號(hào)維持在0或1的位準(zhǔn)分為2類。(圖十二)

上文列出了標(biāo)準(zhǔn)元件庫(kù)內(nèi)時(shí)序模型的項(xiàng)目,但對(duì)其量化的數(shù)據(jù)卻沒(méi)有加以說(shuō)明。接下來(lái),我們就來(lái)看看到底這些時(shí)序資訊的確實(shí)數(shù)值是如何定義在標(biāo)準(zhǔn)元件庫(kù)中的。

以Combinational Timing Arc為例,訊號(hào)從輸入到輸出的延遲時(shí)間可以描述成以輸入的轉(zhuǎn)換時(shí)間(Transition Time)和輸出的負(fù)載為變數(shù)的函數(shù)。描述的方式可以是線性的方式,如圖十三所示。也可以將這2個(gè)變數(shù)當(dāng)成指標(biāo),建立時(shí)序表格(Timing Table),讓STA軟體可以查詢出正確的延遲時(shí)間。這種以表格描述的方式會(huì)比上述線性描述的方式準(zhǔn)確許多,因此現(xiàn)今市面上大部分的標(biāo)準(zhǔn)元件庫(kù)皆采用產(chǎn)生時(shí)序表格的方式來(lái)建立Timing Model。

我們舉個(gè)簡(jiǎn)單的例子來(lái)說(shuō)明STA軟體如何從時(shí)序表格計(jì)算出元件延遲時(shí)間。(圖十四)

元件延遲時(shí)間(Ddelay):輸入達(dá)邏輯1位準(zhǔn)50%到輸出達(dá)邏輯1位準(zhǔn)50%的時(shí)間。

元件轉(zhuǎn)換時(shí)間(Dtransition):輸出達(dá)邏輯1位準(zhǔn)20%(80%)到80%(20%)的時(shí)間。

當(dāng)輸入的轉(zhuǎn)換時(shí)間為0.5,輸出負(fù)載為0.2時(shí),可由圖十四的時(shí)序表格查得元件I2的延遲時(shí)間為0.432。而由于表格的大小有限,對(duì)于無(wú)法直接由表格查詢到的延遲時(shí)間(如輸入轉(zhuǎn)換時(shí)間0.25,輸出負(fù)載0.15),STA軟體會(huì)利用線性內(nèi)插或外插的方式計(jì)算延遲時(shí)間。

對(duì)于其他的Timing Arc,不管是時(shí)序延遲或時(shí)序檢查,其相對(duì)應(yīng)的時(shí)序數(shù)值計(jì)算和上例的計(jì)算方式是一樣的。

接下來(lái)我們說(shuō)明操作環(huán)境(Operating Condition)對(duì)時(shí)序的影響。操作環(huán)境指的是制程(Process)、電壓(Voltage)、溫度(Temperature)三項(xiàng)因子。這三項(xiàng)因子通常會(huì)被簡(jiǎn)稱為PVT,其對(duì)時(shí)序的影響可用下方線性方程式來(lái)描述。其中nom_process、nom_voltage及 nom_temperature會(huì)定義在標(biāo)準(zhǔn)元件庫(kù)中,代表建立時(shí)序表格時(shí)的操作環(huán)境。

Interconnect Data:

在「什么是STA」段落的例子中,為了方便說(shuō)明,我們并沒(méi)有把邏輯閘和邏輯閘間的連線延遲(Interconnect Delay)考慮在內(nèi)。事實(shí)上,許多DSM IC設(shè)計(jì)之時(shí)序表現(xiàn)是由連線延遲主導(dǎo)的,其重要性不容我們忽視。

連線延遲依照布局與繞線(P&R)前后有不同的考量。在布局與繞線前,元件在晶片中擺放的位置尚未確定,所以連線延遲是一個(gè)預(yù)估值。而在布局與繞線之后,連線延遲則是根據(jù)實(shí)際繞線計(jì)算出來(lái)的。對(duì)布局與繞線之前的連線延遲,通常是用Wireload Model來(lái)預(yù)估。Wireload Model根據(jù)晶片面積的預(yù)估大小及連線驅(qū)動(dòng)元件數(shù)目(Fan-out)的多寡來(lái)決定連線的電阻和電容值,STA軟體則利用這些電阻電容值計(jì)算出連線延遲。在布局與繞線之后,可以利用電阻電容萃取(RC Extraction)軟體將繞線圖形轉(zhuǎn)換成實(shí)際的電阻電容電路,然后貼回(Back-annotate)STA軟體計(jì)算連線延遲。

Timing Constraints:

Timing Constraint為使用者所給定,用來(lái)檢驗(yàn)設(shè)計(jì)電路時(shí)序的準(zhǔn)則。其中最重要的一項(xiàng)就是時(shí)脈(Clock)的描述。對(duì)于一個(gè)同步電路而言,暫存器和暫存器之間的路徑延遲時(shí)間必須小于一個(gè)Clock周期(Period),也就是說(shuō),當(dāng)我們確認(rèn)了Clock規(guī)格,所有暫存器間的路徑的Timing Constraint就會(huì)自動(dòng)給定了。

Clock規(guī)格包含波形、Latency及Uncertainty的定義。波形定義一個(gè)Clock的周期及訊號(hào)上升緣及下降緣的時(shí)間點(diǎn)。 Latency定義從Clock來(lái)源到序向元件Clock輸入端的延遲時(shí)間。Uncertainty則定義Clock訊號(hào)到序向元件Clock輸入端可能早到或晚到的時(shí)間。

如果上面的文字讓你有不知所云的感覺(jué),那底下看圖說(shuō)故事的解說(shuō)也許會(huì)讓你有比較清晰的概念。在圖十五的電路中,左邊的正反器(Flip-Flop)在第一個(gè)Clock上升緣時(shí)會(huì)丟出資料,此資料會(huì)在第二個(gè)Clock上升緣讓右邊的Flip-Flop擷取。要分析右邊的Flip-Flop能否正確擷取資料就必須知道第一個(gè)Clock上升緣到達(dá)節(jié)點(diǎn)C1的時(shí)間點(diǎn)和第二個(gè)上升緣到達(dá)節(jié)點(diǎn)C2的時(shí)間點(diǎn)。假設(shè)在時(shí)間點(diǎn)為0的時(shí)候,Clock訊號(hào)由S點(diǎn)出發(fā),經(jīng)過(guò)一段時(shí)間(source latency,1個(gè)時(shí)間單位,模擬晶片外的Clock延遲時(shí)間,例如板子上的繞線產(chǎn)生的訊號(hào)延遲時(shí)間)到達(dá)電路的Clock輸入端點(diǎn)P,接下來(lái)再經(jīng)過(guò)一段時(shí)間(晶片內(nèi)Clock繞線造成的訊號(hào)延遲時(shí)間),Clock訊號(hào)分別到達(dá)C1和C2節(jié)點(diǎn)。如果電路已經(jīng)進(jìn)行布局與繞線,輸入端點(diǎn)P到C1和C2的訊號(hào)延遲時(shí)間可由連線上的寄生電阻電容計(jì)算得來(lái)。比方說(shuō),經(jīng)過(guò)計(jì)算發(fā)現(xiàn)訊號(hào)由P傳遞到C1需要1個(gè)時(shí)間單位,由P傳遞到C2需2個(gè)時(shí)間單位,則Clock訊號(hào)第一個(gè)上升緣到達(dá)C1和第二個(gè)上升緣到達(dá)C2的時(shí)間點(diǎn)就會(huì)如圖十六下方兩列所示,分別為時(shí)間點(diǎn)2和13(因?yàn)榧由狭?個(gè)時(shí)間單位的source latency)。

在布局與繞線之前,我們無(wú)法準(zhǔn)確得知P到C1和C2的訊號(hào)延遲時(shí)間,僅能先做個(gè)預(yù)估。圖十五的network latency及上文提到的Uncertainty就是用來(lái)做此種預(yù)估的。先假設(shè)我們擁有某種完美的布局與繞線軟體可以讓Clock輸入端點(diǎn)P到所有 Flip-Flop的Clock輸入端的訊號(hào)延遲時(shí)間一模一樣,那么我們只要知道這個(gè)訊號(hào)延遲時(shí)間就可以得到Clock訊號(hào)到達(dá)C1和C2的時(shí)間點(diǎn)了。這個(gè)訊號(hào)延遲時(shí)間可以藉由電路特性(如預(yù)估面積大小,F(xiàn)lip-Flop數(shù)目等)來(lái)做預(yù)估,而這個(gè)預(yù)估值就是所謂的network latency。如果這種完美的軟體存在的話,那Clock的上升緣到達(dá)C1和C2的時(shí)間點(diǎn)就可以由Latency(source latency + network latency)計(jì)算出來(lái)。

很不幸的,世界上沒(méi)有這么完美的軟體,在布局與繞線后Clock輸入端點(diǎn)P到所有Flip-Flop的Clock輸入端的訊號(hào)延遲時(shí)間不會(huì)完全一樣。也就是說(shuō)Clock的某個(gè)上升緣不會(huì)同時(shí)到達(dá)C1和C2。因此我們要對(duì)上述的預(yù)估值做些修正,加入U(xiǎn)ncertainty的描述來(lái)定義Clock上升緣左右移動(dòng)的可能范圍。在圖十六中,Uncertainty為1個(gè)時(shí)間單位,所以Clock第一個(gè)上升緣會(huì)在時(shí)間點(diǎn)3(因?yàn)?Latency為3)左右1時(shí)間單位范圍內(nèi)(也就是時(shí)間點(diǎn)2到時(shí)間點(diǎn)4)到達(dá)C1,。第二個(gè)上升緣則會(huì)在時(shí)間點(diǎn)12到14的范圍內(nèi)到達(dá)C2。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論