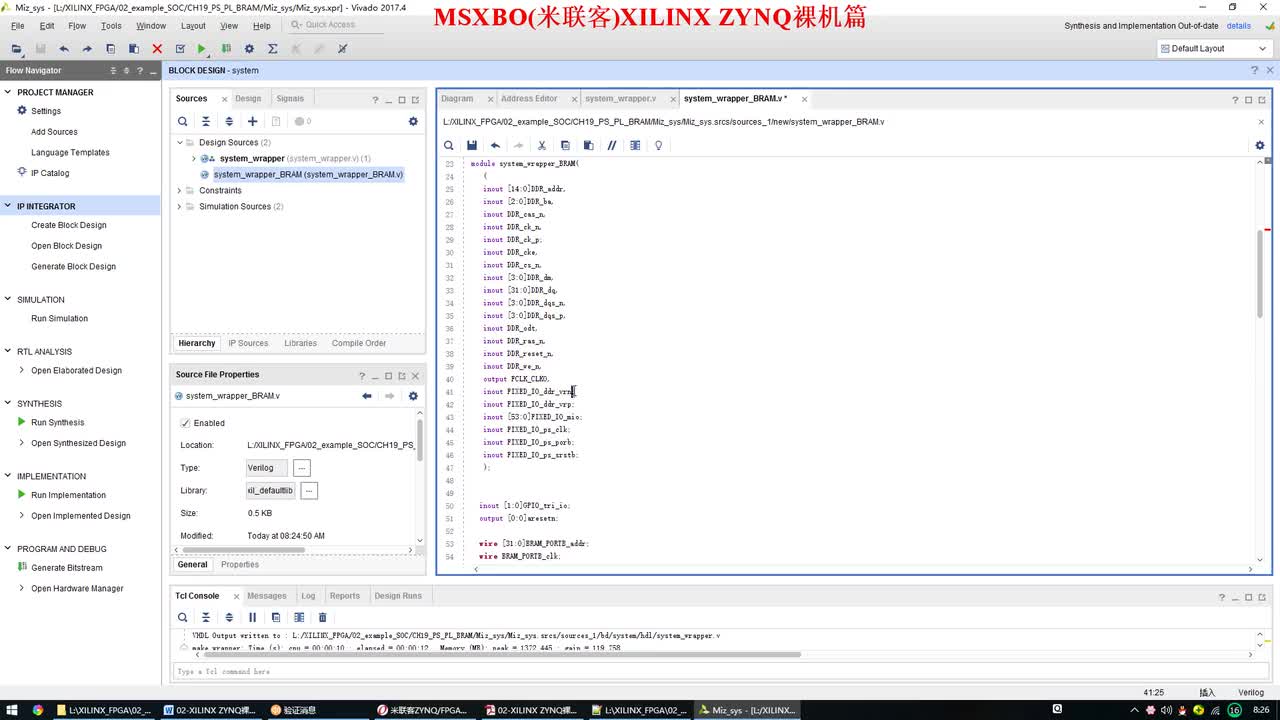

本文介紹一個FPGA常用模塊:SRIO(Serial RapidIO)。SRIO協議是一種高速串行通信協議,在我參與的項目中主要是用于FPGA和DSP之間的高速通信。有關SRIO協議的詳細介紹網上有很多,本文主要簡單介紹一下SRIO IP核的使用和本工程的源代碼結構。

2023-12-12 09:19:08 856

856

Keystone_SRIO_Init(&srio_cfg);之后,接收即終止了,之后也沒辦法繼續接收FPGA傳輸的數據。而此時DSP可以正常向FPGA傳輸數據。

??????? 不知道是不是因為沒有添加

2018-06-21 13:16:48

數據,這個時候觀測交換芯片對應的端口的寄存器,發現端口狀態出錯,其值為0x84120306。

請問

1.是否可以這么理解,交換芯片和FPGA重新load程序之后,DSP的SRIO仍然處于已初始化的狀態

2018-06-21 13:50:07

? ? ? ? 我已經研究過K1_STK中的SRIO例程,對SRIO的工作方式也很熟悉。現在將DSP板與FPGA板兩板通過SRIO 4x進行背板連接,因為FPGA有專門的工具可以通過發送PRBS

2018-06-21 06:25:29

6678通過SRIO與FPGA通信,FPGA發起,向DSP的內存寫數據,DSP再將數據寫回FPGA。問題1:DSP如何得知何時發送完畢?是否必須通過中斷(門鈴中斷或者GPIO中斷)問題2:DSP

2019-01-09 10:58:04

各位專家好!請問:我現在想通過6678的SRIO接收來自FPGA的數據,DSP作為從屬。用的是論壇給的KI_STK_V1.1的SRIO例程,在test between 2 DSPs的程序段里修改

2019-01-11 07:33:39

MicroBlaze掛載的外設。可以選擇通過軟件寄存器來控制用戶IP。點擊Next可以選擇寄存器位寬和個數。其中IPIC是user_logic 與PLC總線之間數據交互的一系列信號。點擊NEXT完成配置。(2)設計編寫

2018-01-09 14:53:42

\device_srio.cport mode(port模式)SRIO通道有自回環(loopback)模式和普通模式(Normal),要使用SRIO實現FPGA和DSP的通信,必須將各port調至Normal模式,即

2020-09-23 11:08:36

\device_srio.cport mode(port模式)SRIO通道有自回環(loopback)模式和普通模式(Normal),要使用SRIO實現FPGA和DSP的通信,必須將各port調至Normal模式,即

2020-09-08 10:36:41

FPGA與6678調試SRIO通信過程中,如DSP修改后重新編譯LOAD后,FPGA方無反應,需要斷電再上電才能通信正常,請問可能是什么原因,根據論壇例程改編的DSP程序。。。

2018-08-07 07:28:46

CCS5.5DSP 6657FPGA XC7Z030FPGA 與 FPGA 之間SRIO傳輸成功;DSP 與 DSP 之間SRIO傳輸成功;問題 : FPGA 與 DSP 之間 ,PORT OK 可以通過,可是就是無法正確傳輸成功。 這會是什么問題呢?會是什么原因導致的呢?需要注意什么地方呢?

2019-01-10 11:17:28

IP CORE SRIO 2.1 ENDPOINT ECP3

2023-03-30 12:02:57

SITE LICENSE SRIO 2.1 ECP3

2023-03-30 12:03:00

各位好!

? ? ? ?參考Ti給的例程,發現SRIO中斷是直接配置寄存器,然后再SRIO_vector.asm文件中完成中斷服務函數入口的映射,而主機PC和DSP的交互是通過利用CSL庫函數來完成中斷配置,我想問一下:兩種中斷配置方式能同時寫在同一個函數里面嗎?

謝謝!

2018-06-21 08:43:37

本人使用virtex 5 與dsp c6678 srio通信,fpga是從模式,一直使用的1x。現在調試4x的時候遇到問題,4x會自動變成1x通信,或者:dsp成4x,fpga也訓練成4x,但是此時

2018-06-21 00:10:20

我用fpga nwrite方式向6678寫數然后看ddr3內存 點內存界面的持續刷新時 內存數據不變 點刷新時內存數據變化 有的時候只有srio初始化的時候內存數據變一下 請問問題可能出在哪

2018-08-03 06:51:53

嗨, 我想通過srio協議將數據從我的模塊(fpga)發送到其他模塊(tc6678texas處理器)。我想知道是否有任何中斷來啟動轉移?感謝致敬M LOKESWARA REDDYBEL

2020-04-30 09:31:47

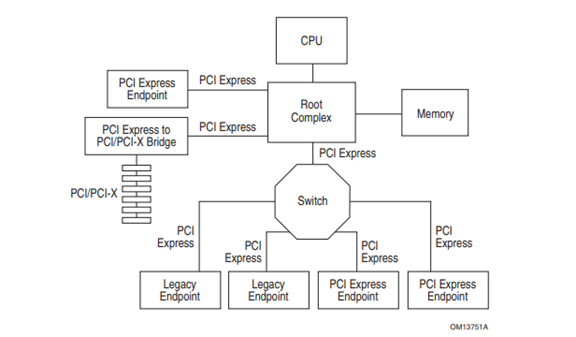

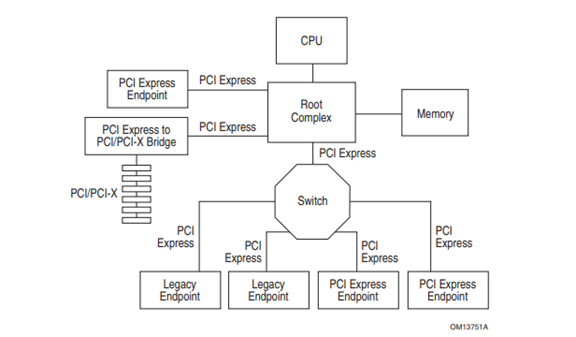

數據、萬兆以太網數據、SRIO協議等數據的采集。采-存-傳系統——存儲高帶寬大容量的存儲能力是本系統的靈魂我們的系統采用高性能NVME SSD為存儲介質,NVME SSD硬盤通過PCIe Gen3x4

2021-12-16 11:33:22

? ? ?各位好,我正準備投板FPGA+DSP(c6657+kintex7)的一塊板子,兩者是通過SRIO口做數據的交互。目前,整個板子剩下SRIO口的電路還不是很確定,雖然在論壇也看過一些帖子,但

2018-06-19 01:47:15

請教SRIO通信問題,6672和FPGA的SRIO通信,2個lane連接,現象如下:

?(1)兩端都配置成2x,3.125G,FPGA顯示port initial成功,link initial失敗。

(2)把6672配置成2個1x,FPGA顯示初始化成功,但無法進行數據通信。

請教是什么問題,謝謝。

2018-06-21 13:52:27

我在做EVMC6678L_EVM與FPGA用SRIO通信,首先我要做SRIO外部回環測試驗證我的DSP能夠向FPGA發包,硬件上,我做了一個互聯底板,安裝AMC插座和SMA插件,用連接線實現SRIO

2018-12-26 14:14:40

寫數據進行比對,以檢測SRIO傳輸是否有數據錯誤。1.1.3例程使用特別提示:例程使用,請參考下面章節順序執行。確保ZYNQ PL程序要先運行,然后才能運行DSP程序。1.1.3.1 加載運行ZYNQ程序

2023-02-21 14:51:50

進行比對,以檢測SRIO傳輸是否有數據錯誤。1.1.3 例程使用特別提示:例程使用,請參考下面章節順序執行。確保ZYNQ PL程序要先運行,然后才能運行DSP程序。1.1.3.1 加載運行ZYNQ程序

2023-02-02 21:43:20

目前已調試完成兩片DSP之間的SRIO通信,在進行DSP與FPGA之間的SRIO。現在遇到了如下幾個問題。希望TI的工程師們有時間的時候給點幫助,不勝感激。1.DSP之間傳輸時一切正常,但是

2018-12-27 11:16:03

目前在調試多片6678與fpga通過cps1848交換芯片通信,使用的是論壇中keystone_srio例程調試過程中有幾個問題。1.dap向dpga發數時而成功時而失敗,失敗時查看error

2019-06-04 11:03:34

你好!我現在嘗試實現FPGA通過SRIO接口向DSP TMS320C6670發送數據,代碼基于CCS5.0下的SRIO_Loopbacktestproject,但發現在sriodevice_init

2018-08-06 06:38:43

6678、FPGA,程序基于STK例程修改。流程:FPGA通過srio傳輸數據后,將傳輸完成標志置1。該傳輸完成標志位于DSP的SL2中。DSP查詢該標志的狀態。如果為1,則去讀取數據。讀取數據后

2018-08-03 09:20:22

進行修改,實現了c6678與FPGA之間的數據通信(數據通信功能已測試完成)。現在的問題是,原代碼中可以正常接收到doorbell中斷(即FPGA向C6778發送doorbell,在c6678一側會成

2018-08-03 06:19:00

你好,

? ? ? 我想將FPGA上的數據 , 位寬 32bit, 速率500MHz 左右 實時傳到 DSP上去,應該如何設計接口,不使用RAPID IO/SRIO 等接口。

2018-06-21 07:51:58

本帖最后由 一只耳朵怪 于 2018-6-25 14:20 編輯

大家好,我現在利用SRIO接口從FPGA向6678的共享內存發送數據,數據分段存儲。例如將共享內存(共4M)分8段,輪詢向這8

2018-06-25 01:31:27

基于ZigBee網與以太網間數據傳輸系統該怎樣去設計?

2021-05-19 06:20:59

在現代各類儀器的開發中,人機交互功能正起著無可替代的作用。人機交互界面友好的儀器將更容易操作和使用,從而提高工作效率。液晶顯示器(LCD)具有功耗低、價格低、壽命長、接口控制方便等特點,在科研

2019-10-21 07:48:41

如題,怎么將保存的的txt文件中的時間數據讀出啊,用表格顯示的話,時間數據總是顯示0啊,怎么回事啊

2013-07-23 11:05:40

在現代各類儀器的開發中,人機交互功能正起著無可替代的作用。人機交互界面友好的儀器將更容易操作和使用,從而提高工作效率。液晶顯示器(LCD)具有功耗低、價格低、壽命長、接口控制方便等特點,在科研

2019-08-22 07:50:27

我用quartus跑了cortexm3,但是不知道怎么和fpga進行數據交互,有償求個大佬解答,解答就行,不需要代做,有的麻煩加一下我qq1661044013

2019-05-12 21:32:01

大家好,我想請教一個問題,我需要把一段離散的時間數據轉換成連續的時間數據,如圖左邊,第1秒到第10秒的數據都是100,第10秒到第20秒的數據都是200,第20秒到第30秒的數據都是300,想轉換成

2020-04-09 09:16:49

大家好,5396的手冊網上只要簡版的2頁說明,想問下把5396的數據接口直接連到FPGA的GTX,能進行5396與FPGA的數據交互嗎,還是需要相關的配置來完成5396余FPGA的交互呢?還有把數據

2018-01-07 23:02:05

本文介紹一種基于FPGA高精度時間數字轉換電路的設計方法,利用片內鎖相環(PLL)和環形移位寄存器,采用不高的系統時鐘便可得到很高的時間分辨率,且占用較少邏輯資源。可作為功能電路獨立使用,也可作為 IP核方便地移植到其他片上系統(SOC)中。

2021-05-07 06:10:43

我有一塊TMS320C6670 的開發板,現在想和FPGA通信,想通過SRIO接口通信,求一個例程熟悉下?謝謝

2018-06-21 18:50:51

程序如圖,但是運行后顯示兩列時間數據 ,如何才能只顯示一列時間數據

2019-03-27 13:19:32

我在做fpga與dsp的SRIO通信,我用的是論壇上提供的SRIO test程序,目前dsp端能夠實現端口0的外部回環測試。fpga端的協議還沒做通,我想用dsp直接給fpga發包,fpga根據收到

2018-06-21 10:45:13

通過全局地址搬移,如從0x10800000搬移到0x13800000,那么請問如果是多核交互的話,是否其他核就是從MSMC,共享DDR,或者0x13800000對應的本地內存空間去取數據就可以了,還是

2019-01-02 15:23:29

現在用6678的SRIO從FPGA接收數據,FPGA做主!現在遇到一個問題,就是怎么判斷FPGA發送過來的數據已經到達DSP指定的空間,比如我想把數據發送到6678的SL2,待數據完全到達我才能對數據

2019-01-03 11:36:07

本帖最后由 一只耳朵怪 于 2018-6-19 15:39 編輯

因為項目需求,一片C6670需要連接到兩片FPGA,但是又覺得沒必要使用SRIO SWITCH。所以我的問題是:C6670

2018-06-19 00:53:24

本帖最后由 一只耳朵怪 于 2018-6-19 14:49 編輯

本人使用的是6678芯片,現在需要編寫6678核間數據交互部分的程序。看了資料,qmss,CPPI都可以用來進行核間數據

2018-06-19 02:42:49

你好我對DSP和SRIO之間的通信感興趣。有人知道virtex-6 FPGA是否有srio引腳,以及如何配置?

2020-06-14 14:22:51

收不到數據,serdes loopback收到數據正確。采用的是6678平臺,目前external loopback 硬件連接是:通過外部用線連RX,TX。SRIO external loopback

2018-06-19 06:26:42

怎樣去設計數據采集與交互系統的軟件部分?怎樣去設計數據采集與交互系統的硬件部分?

2021-05-24 06:55:36

在論壇下載到SRIO的官方例程,移植到開發板后,使DSP與FPGA通訊,DSP向FPGA發送1K數據成功,更改傳輸數據的大小為1024*1024后編譯成功,但是還是傳輸的1K數據,查看地址以及配置

2018-07-23 10:49:17

Hi,Ti guys,我在使用自己板上的c6678,利用論壇上keystone_srio程序調試dsp和fpga端的通信。同事從fpga(v6,srio核)看來收發地址都是34衛的,但我調DSP互聯

2018-12-28 11:08:14

收發接口來說,驅動初始化完畢之后,是不是FPGA可以通過一個接口向DSP發送數據,而DSP也可以通過另一個反向接口發送數據,就是說對于一對SRIO接口來說,兩邊是不是都能通過這個接口主動發起數據讀寫操作啊?謝謝!

2018-06-19 03:02:21

本帖最后由 一只耳朵怪 于 2018-5-25 15:56 編輯

我們設計的系統是6678和Altera的FPGA利用SRIO進行通訊,FPGA利用SRIO 1X接口,對6678進行SRIO

2018-05-25 10:16:06

摘要:闡述了基于,’-- 的海量空間數據在線分發系統原理和關鍵技術,給出了海量影像空間數據在線瀏覽發布的實例。關鍵詞:海量空間數據;影像數據發布;無縫影像數據庫

2009-01-09 11:58:48 22

22 分析空間數據的特點和用常規方法進行空間數據聚類分析的難點與不足,提出一種基于改進的演化算法空間數據聚類方法——SDCEA。解決用傳統方法進行空間數據聚類分析時存在的問

2009-04-10 09:29:24 28

28 利用數據庫技術來管理海量的空間數據,有兩種方法:一種是在數據庫和用戶應用系統間建立中間層,稱為空間數據引擎SDE,利用SDE作為中間接口使數據庫操作系統能存儲和管理空

2009-08-07 09:56:31 9

9 本文在介紹空間數據挖掘、Agent 技術的概念和特點的基礎上,提出一個基于Agent的分布式空間數據挖掘系統,描述了其實現過程。由于在實現過程中只傳送執行挖掘功能的移動Agent

2009-12-25 13:38:56 14

14 什么是空間數據轉換格式

空間數據轉換格式是實施空間數據轉換的標準中介格式。為實現轉換,需要制訂并遵循統一 的空間數據轉換標準,包括現實世

2009-06-17 07:35:45 1549

1549 什么是空間數據庫無縫連接

空間數據庫的無縫連接是一個建立在用戶與空間數據庫接口基礎上的概念,它是空間數據庫 中空間數據集

2009-06-17 07:36:28 1145

1145 什么是空間數據交換中心

空間數據交換中心是指對不同范圍、領域的空間信息及其元數據進行有效管理、給信息需求 者提供空間數據

2009-06-17 07:40:05 875

875 :根據現行文獻中反復提到的空間數據處理內涵的理解,將空間數據處理分為空間數據處理技術和空間數據處理理論,簡要論述了各自的主要內容,討論了空間數據挖掘的現狀和今后研究的重

2011-06-24 11:12:43 0

0 本文介紹了這種基于SRIO互聯技術的高速實時數據處理硬件平臺,并在該平臺上研究了多DSP之間、DSP與FPGA之間的SRIO通信技術。

2012-01-10 15:07:55 3562

3562

基于FPGA的高精度時間數字轉換 方法研究

2015-10-30 10:59:13 4

4 一種基于FPGA的時鐘相移時間數字轉換器_王巍

2017-01-07 22:23:13 2

2 基于Linux及Qt_Embedded的壓鑄車間數據采集系統設計_魯遙遙

2017-02-07 18:11:35 0

0 空間數據系統咨詢委員會(CCSDS)-直致力于空間任務安全性方面的工作,并成立了一個工作小組,旨在數據鏈路層為遙控遙測通信制定安全協議,即空間數據鏈路安全(SDLS)協議。該協議為已存在的空間數據

2017-11-07 15:29:37 19

19 難度大,實現復雜算法也比較困難。因此,結合多核DSP和FPGA的優勢,構建基于異構處理器的信號處理系統成為當前一種發展趨勢。異構處理器間的高速通信成為高速信號處理系統[1]的關鍵問題之一,本文基于SRIO協議設計和實現了DSP與FPGA之間的高速數據通信。

2017-11-17 03:11:01 28802

28802

為了滿足2ynq-7000系列芯片的SRIO數據傳輸要求,提出了一種基于FPGA控制DMA傳輸進行SRIO通信的設計方案,并完成了ARM與FPGA核間高吞吐率的數據交互操作。系統的FPGA部分主要

2017-12-21 11:37:03 30

30 隨著信息技術的飛速發展和企業界新需求的不斷提出,以面向事務處理為主的空間數據庫系 統已不能滿足需要,信息系統開始從管理轉向決策處理,空間數據倉庫就是為滿足這種新的 需求而提出的空間信息集成方案,它有四個特點:

2018-09-05 16:58:11 21

21 SRIO是面向嵌入式系統開發提出的高可靠、高性能、基于包交換的新一代高速互聯技術,已于2004年被國際標準化組織(ISO)和國際電工協會(IEC)批準為ISO/IECDIS 18372標準。SRIO則是面向串行背板、DSP和相關串行數據平面連接應用的串行RapidIO接口。

2020-06-17 11:48:12 2555

2555 本文為您分享基于C66x+FPGA的SRIO開發視頻教程,適用于創龍TMS320C6678、TMS320C665x、Kintex-7、Artix-7平臺。

2020-07-01 10:47:39 1760

1760 近年來,隨著面向對象數據庫技術成熟,使用大型的RDBMS管理海量空間數據成為可能,企業化GIS數據組織和處理就顯得非常必要。空間數據共享是當前地理信息系統建設的重要課題,而空間數據轉換是實現信息共享

2020-09-17 16:07:00 13

13 基于Oracle-Spatial空間數據共享系統設計(肇慶理士電源技術有限公司圖片)-該文檔為基于Oracle-Spatial空間數據共享系統設計總結文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-09-16 13:59:08 1

1 隨著PCIe接口、以太網接口的飛速發展,以及SOC芯片的層出不窮,芯片間的數據交互帶寬大大提升并且正在向片內交互轉變;SRIO接口的應用市場在縮小,但是由于DSP和PowerPC中集成了SRIO接口,因此在使用DSP/Power PC + FPGA的使用場景中仍然占有一席之地。

2022-08-02 10:00:26 3112

3112

目前具備SRIO接口的硬件不多,推薦廣州星嵌電子科技有限公司開發的DSP+FPGA+RAM開發板XQ6657Z35-EVM。

2022-11-08 17:22:21 743

743

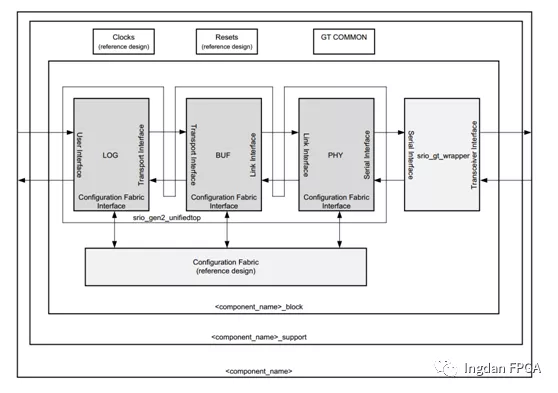

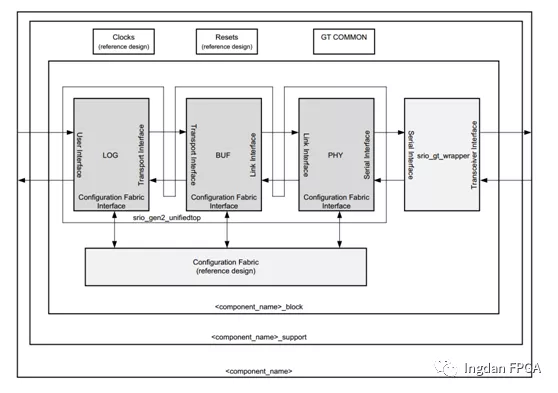

數據從遠程設備(假設為DSP的SRIO端)傳輸過來,FPGA端(假設我們這端為FPGA的SRIO端口)通過RX接收到串行數據,先到達物理層進行時鐘恢復,串并轉換,之后進行8b/10b解碼操作、CRC校驗,這一系列的操作都在物理層完成,之后進入傳輸層

2023-03-03 10:19:53 725

725 摘要: 現代 信號 處理系統通常需要在不同處理器之間實現高速數據 通信 ,SRIO協議由于高效率、低延時的特性被廣泛使用。本文研究了在 FPGA 和 DSP 兩種處理器之間實現SRIO協議的方法

2023-03-20 15:00:01 1324

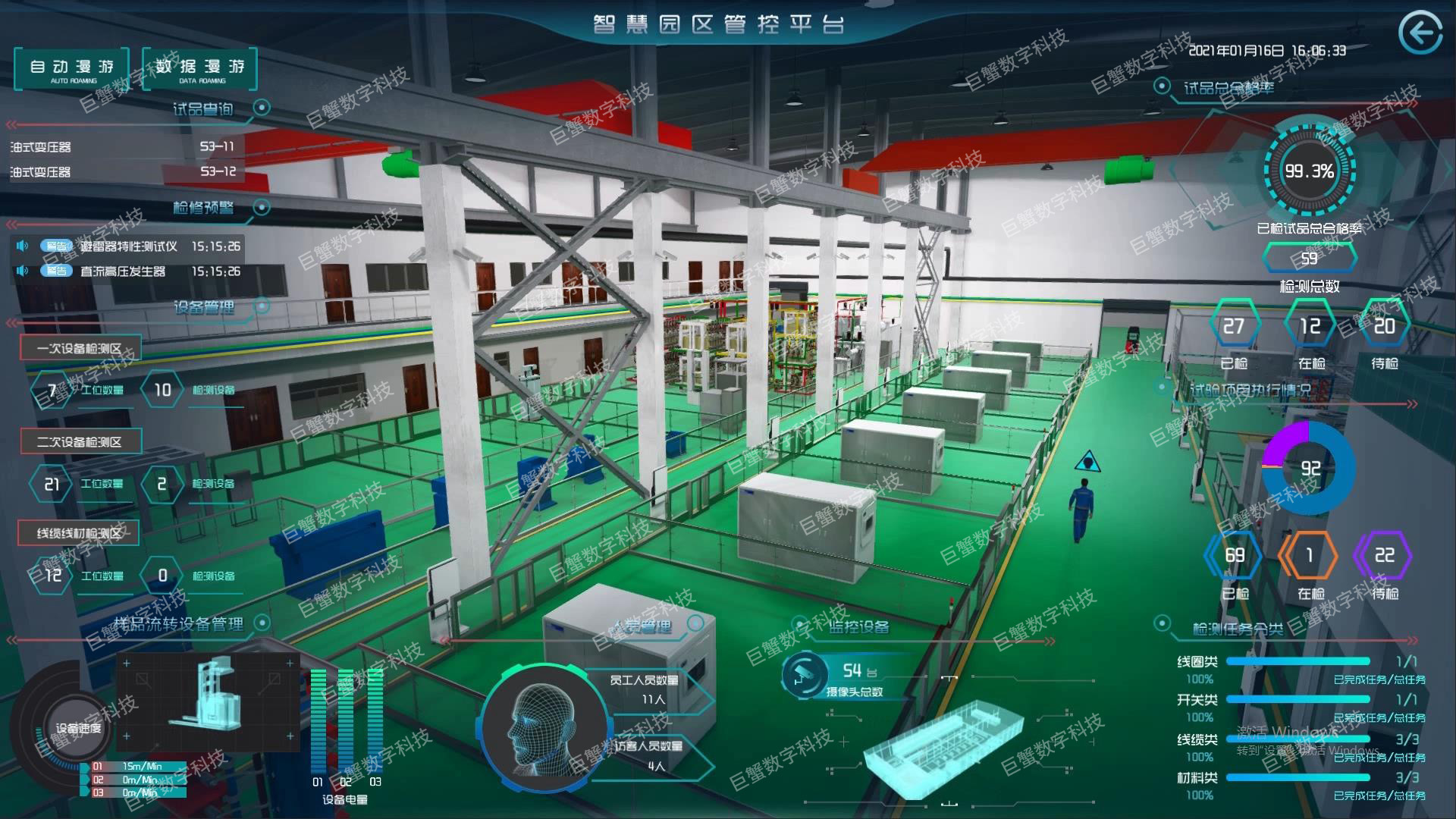

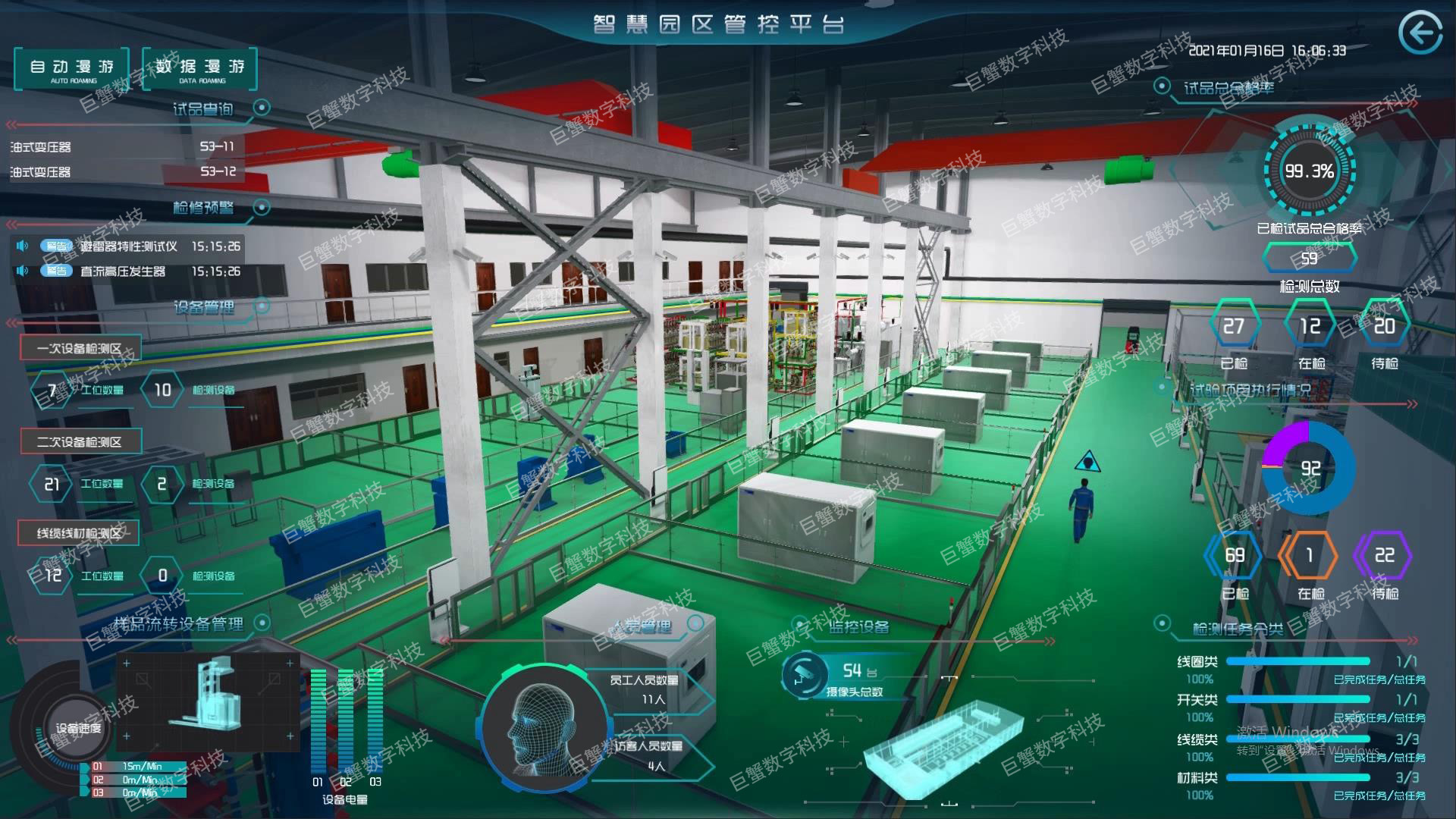

1324 河南鄭州洛陽數字孿生智慧工廠,工廠車間數字化三維仿真交互,3d可視化數據大屏展示系統。在推動制造業邁向智能化的諸多技術之中,數字孿生備受關注,也被寄予厚望。巨蟹數字科技通過虛實融合,不僅可以實現可視化展示,還可以實現精準預警以及運營優化,成為傳統工廠數智化建設轉型的熱門技術。

2023-03-31 14:18:42 478

478

SRIO這種高速串口復雜就復雜在它的協議上,三層協議:邏輯層,傳輸層以及物理層。

數據手冊會說這三層協議是干什么的呢?也就是分工(【FPGA】SRIO IP核系統總覽以及端口介紹(一)(User Interfaces 之 I/O Port))

2023-04-25 11:20:55 1176

1176

目的:實現上位機與FPGAuart交互

開發環境:quatus prime 18.1,芯片 altera :EP4CE15F23C8。

實驗現象: 1.使用uart:bps=9600(參數可調整

2023-05-08 10:28:33 2

2 本文介紹一個FPGA常用模塊:SRIO(Serial RapidIO)。SRIO協議是一種高速串行通信協議,在我參與的項目中主要是用于FPGA和DSP之間的高速通信。有關SRIO協議的詳細介紹網上有很多,本文主要簡單介紹一下SRIO IP核的使用和本工程的源代碼結構。

2023-09-04 18:19:18 683

683

等領域,以實現設備之間的高速、低延遲數據交互。SRIO交換芯片的出現,極大地提升了數據傳輸效率和系統性能。

2024-03-16 16:40:42 1567

1567

電子發燒友App

電子發燒友App

評論