摘要:基于時分長期演進(timedivision- longtermevolution,TD-LTE)射頻一致性測試系統中數據交互的分析研究,為了很好地滿足現場可編程門陣列(fieldprogrammablegatearray,FPGA)間的大容量數據交互,設計了一種高速的嵌入式技術串行高速輸入輸出口(serialrapidIO, SRIO),實現2塊FPGA芯片間的互連,保證在TD-LTE系統中上行和下行數據處理的獨立性和交互的便捷。基于Xilinx公司的Virtex-6系列XC6VLX475T芯片,給出了SRIO接口的整體性設計方案,經過ModelSim軟件仿真,確定適合項目需要的數據交互的格式類型和事務類型,對接口代碼進行綜合、板級驗證、聯機調試等,在ChipScope軟件上對比分析數據傳輸的正確性,通過測試模塊統計比較發送和接收信號的誤比特率, 確定了SRIO接口在高速數據傳輸的穩定性和可靠性,成功驗證了SRIO接口在FPGA之間數據的互連互通,并將該方案作為一種新的總線技術應用于TD-LTE射頻一致性測試儀系統開發中。

0 引言

隨著移動通信技術研究的不斷深入, 3GPPLTE逐漸成為支撐世界電信業務的重要移動通信系統。在時分長期演進(timedivision-longtermevolution,TD-LTE)系統的研究中,頻分多址技術、多輸入多輸出(multipleinputmultipleoutput, MIMO)技術[1]等各種創新技術的應用,使得系統的處理能力要求越來越高,高速數字信號處理(digitalsignalprocessor,DSP)以及大規模現場可編程門陣列(fieldprogram-mablegatearray,FPGA)被廣泛應用[2],僅僅依靠提高單處理器的性能來提高處理能力越來越艱難,必須采用實時并行處理技術。多處理芯片并行處理是滿足系統處理能力要求的有效解決途徑,因此,芯片之間的互連顯得尤為重要。傳統的分級共享總線帶寬和速率都很低,其性能已經達到極限,不能滿足TD-LTE的高速處理需求。

傳統并行總線互連所需要引腳數較多,給器件封裝、測試和焊接都帶來了一些問題,也會增加在系統中應用的復雜度。而串行高速輸入輸出口(se-rialrapidIO,SRIO)接口具有速度快、管腳數少、系統成本低、可以實現點對點或點對多點通信等優點。SRIO接口已經成功應用在多DSP處理芯片間 的數據互連[3] 。在多FPGA處理芯片系統架構的TD-LTE系統中,基帶處理信息交互急需一種新的 高速互連接口。本文在對SRIO協議[4] 及相關技術 進行深入研究后,設計了一種基于可靠的開放式互連協議標準,實現2塊FPGA芯片之間的數據交互方案,提高了數據交互能力,并對傳輸時延進行分析,滿足TD- LTE射頻一致性測試系統的性能要求。

1 SRIO技術

1.1 SRIO的簡介

SRIO屬于系統內部互連技術,適用于高性能的 嵌入式設備的系統內部互連, 還提供了嵌入式系統開發者所需的可擴展性、魯棒性和效率。RapidIO采用包交換技術,在網絡處理器(networkprocessingunit,NPU)、中央處理器(centralprocessingunit,CPU)和DSP之間的通信具有高速、低延遲、穩定可靠的互連性,可行的應用包括多處理器、存儲器、網絡設備中的存儲器映射I/O器件、存儲子系統和通用計算平臺的數據交互,具有廣闊的應用前景。

2011年5月發布的RapidIOv2.1規范提供了2種接口模式(1x和4x)[5] , 1x使用較少的邏輯資源,數據帶寬也比較低;4x需要更多的邏輯資源,但是提供了更高的帶寬和更好的可靠性。時鐘采用內部的差分時鐘,支持的波特率[6] 分別有1.25, 2.5,3.125和5Gboud,滿足不同的應用需求,還支持多 種事物類型,包括讀/寫非共享寄存器、流寫、維護、門鈴和信箱服務等。

1.2 SRIO規范

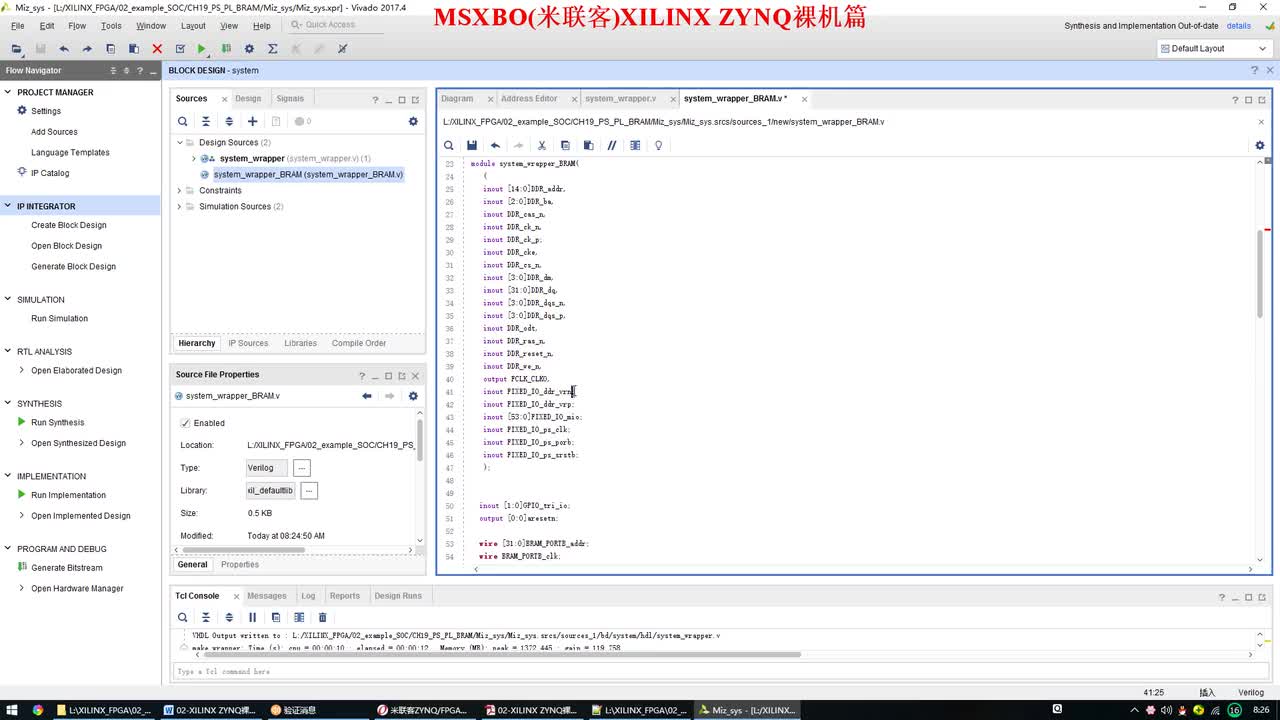

SRIO采用3層分級體系結構[4],如圖1所示。

?

①邏輯層。定義了多種規范,包括I/O邏輯操作、消息傳遞、共享存儲、流量控制和數據流,以及接口的全部協議和包的格式。它們為端點器件發起和完成事物提供必要的信息。

②傳輸層。定義了RapidIO的地址空間,并提供報文在端點設備間傳輸所需的路由信息。

③物理層。處于整個分級結構的底部,定義了設備級接口的細節,明確說明了包傳輸機制、流量控制、電氣特性和低級錯誤管理[7] 。

1.3 SRIO接口寫時序

根據實際應用時FPGA用戶端通過SRIO接口 發送數據所生成的時序圖[6] ,可知其接口的基本時序圖如圖2所示。

?

圖2中,sys_clk是系統時鐘,是由輸入的差分 時鐘經過時鐘模塊得到的,比普通單端時鐘更穩定;ireq_sof_n是開始信號,標志著一個數據幀的開始;ireq_eof_n是結束信號,一個數據幀的結束標志;ireq_vld_n為有效信號,該信號為低時所傳送的數據有效;ireq_rdy_n是開始標志位;ireq_byte_en_n是數據的位使能信號,圖2中數據D6對應的ireq_byte_en_n低8位為高,意味著D6的低8位未被使能,還有其他許多的格式控制信號就不在這一一列舉。

2 SRIO的邏輯設計與實現

SRIO接口作為FPGA間的數據交互通道,數據 通過接口由主機傳送到從機以及由從機傳回至主機的過程,在FPGA中由6個主要的模塊完成:接口控制、時鐘、復位控制、邏輯核、物理核、緩存控制。下面將介紹系統內部實現方案以及各個模塊的功 能及Veriolg語言[8]實現方法[9]。

為了仿真和實現圖的顯示直觀方便,這里采用回環的方式來論證,即發送和接收為同一主機,目標地址與源地址相同。

接口控制模塊是整個系統的起始端和結束端,用戶可以通過該模塊來控制所需交互數據大小、類型和格式。隨機存儲器(randomaccessmemory,RAM)是FPGA用來傳輸數據的中轉站,通過控制RAM中的數據來實現SRIO在2塊FPGA芯片之間數據交互功能。

SRIO使用的是專用的差分時鐘,頻率為156.25MHz或125MHz,不同的時鐘對應的傳輸速率不一樣,差分時鐘的用戶約束為NET“sys_clkn”LOC=“G9”;NET“sys_clkp”LOC=“G10”。這里差分時鐘先是經過差分時鐘緩存(IBUFDS_GTXE1)和時鐘 分頻管理單元(MMCM_ADV)后, 得到2個時鐘UCLK和UCLK_DV4,用來驅動其他模塊工作。

2.1 FPGA設計方案的硬件環境

FPGA是選用2塊Xilinx公司的Virtex-6系列 XC6VLX475T芯片。基于采用第三代Xilinx ASMBLTM架構的40nm制造工藝, Virtex-6FPGA系列還擁有新一代開發工具和早已針對Virtex-5FP-GA而開發的廣泛IP庫支持。Virtex-6FPGA把先 進的硬件芯片技術、創新的電路設計技術以及架構上的增強完美結合在一起,與前代Virtex器件以及競爭FPGA產品相比,功耗大大降低,性能更高并且成本更低。

2.2 FPGA內部實現方案框圖

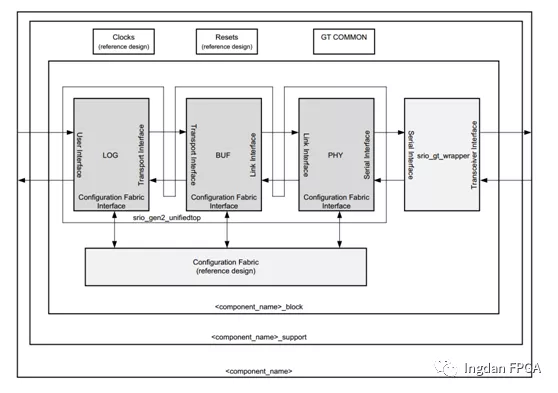

根據SRIO接口構成系統的原理可以設計出SRIO接口硬件實現原理方案框圖,如圖3所示。SRIO完成2塊FPGA芯片間的數據交互,原理圖兩部分是對稱的。

復位模塊為整個工程產生復位信號,這里采用 的是異步復位同步釋放,當一個系統復位信號出現時這個模塊會發出一個鏈路復位信號。

邏輯層接口由3個部分組成:用戶接口、鏈路接口和維護接口。用戶接口又由4個信號端口構成,分別為初始請求ireq、初始響應iresp、目標請求treq和目標響應tresp。用戶可以通過接口控制模塊來配置這4個信號端口,來實現數據向遠端的或寫操作。鏈路接口是用來與物理層通信和緩存器的數據交互。維護操作可以用來發送某些信息,例如,不含端點的器件的錯誤指示符或狀態信息。數據載荷通常放在目標端點的隊列中并向本地處理器產生一個中斷。

緩存器可以平衡系統性能與資源使用之間的平衡,發送和接收的緩存區間大小是可以配置的。緩存核可以處理所有從物理層返回的數據包,包括包的重發和錯誤恢復。它能夠保證數據包正確到達接收端和物理層的驗證。

物理層核( phy sicallayer,PHY )負責處理鏈路調整、初始化和協議,包括插入循環冗余校驗碼(cyclical redundancy check,CRC

)和確認標識符到輸出的信息包中。PHY使用專用的8B/10B碼(即K碼)來管理鏈路,管理內容包括流量控制、包定界和錯誤報告。

最后在接口控制模塊中加入數據收集模塊,收集有效的發送數據ireq_data和接收數據treq_data,再用matlab軟件對比分析誤碼率。

3 數據交互仿真與實現

本文使用Xilinx ISE13.4軟件,聯合ModelSim仿真軟件仿真了不同事物格式和類型下多數據包傳輸。圖4主要顯示了事物格式字段值為5、事物類型字段值為4的情況下數據交互的控制信號和數據信號的整體波形,由于篇幅的原因,圖4只給出了部分發送端和接收端的信號,包括數據信號treq_data_i、開始控制信號treq_sof_n_i、結束控制信號treq_eof_n_i、準備控制信號treq_rdy_n_o、有效控制信號treq_vld_n_i、事務格式treq_ftype_i和事物類型treq_ttype_i等。經過仿真對比分析,驗證了發送和接收數據是相同的,且相應的控制信號滿足協議要求,仿真實現了2塊FPGA芯片間的數據交互功能。

對上述設計的程序進行綜合、布局布線,將代碼下載到硬件平臺后能夠正常運行,通過ChipScope軟件,可以進一步從實際情況測試接口的正確性和穩定性。通過數據采集,可以得到SRIO在硬件平臺上數據交互的測試波形圖,如圖5所示。FPGA以NWRITE(Ftype=5,Ttype=4)事務類型發送數據,而接收端從物理接口接收數據并以逆向解析出用戶數據。

用matlab軟件對比發送和接收數據,計算統計得到的誤碼率低于10-10,滿足高速低誤碼率傳輸系統的要求,而且各個控制信號都符合協議要求。由圖5可知,數據傳輸時延為122個時鐘周期,接口在硬件平臺上運行的實際情況與設計方案是相符的,滿足接口通信的要求,實現了數據的正確接收并且具有較好的穩定性。從而能夠更好地用在實際的開發平臺中。

4 總 結

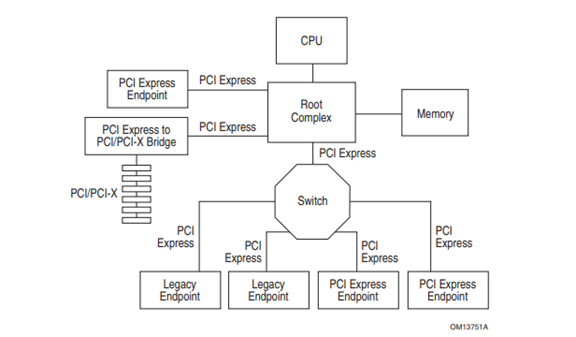

SRIO針對高性能嵌入式系統芯片間和板間互連設計,是未來嵌入式系統互連的最佳選擇之一。本文詳細介紹了SRIO基本規范、系統組成基本原理、硬件環境和關鍵模塊設計。經過軟件仿真和硬件平臺,驗證了2塊FPGA芯片之間數據交互的可行性。并將此模塊應用于TD-LTE射頻一致性測試儀表系統開發中,如圖6所示(TD-LTE射頻一致性測試儀基帶發送板)。通過實驗證明,其工作可靠,達到了設計要求,為下一步數據的正確處理提供了可靠保證。

電子發燒友App

電子發燒友App

評論