編碼器元件是一種可替代炭膜電位器的新型數字式電子元件,編碼器按產品結構分為編碼器元件和編碼器組件.

2012-04-05 10:09:35 6252

6252

增量式光電編碼器原理及其結構

增量式光電編碼器的特點是每產生一個輸出脈沖信號就對應于

2010-06-02 22:50:46 18420

18420 本帖最后由 mr.pengyongche 于 2013-4-30 02:57 編輯

FPGA+DSP 在空中背景下運動目標實時跟蹤系統中的應用 摘要:針對電視跟蹤系統對飛行目標的檢測與跟蹤受到速度瓶頸

2012-12-28 11:19:07

本人剛入門FPGA,不知道如何實現FPGA+DSP,FPGA+ARM接口設計,網上查詢有的說FPGA+DSP可以通過EMIF,IP核實現,FPGA+ARM可以通過SPI,有沒有具體硬件參考的?

2016-08-27 11:30:26

.FPGA+DSP的導引頭信號處理結構成為當前以及未來一段時間的主流。FPGA和DSP處理器具有截然不同的架構,在一種器件上非常有效的算法.在另一種器件上可能效率會非常低。如果目標要求大量的并行處理或者最大

2019-08-30 06:31:29

剛剛學習fpga方面的知識,fpga如何測量一個增量式編碼器,消除抖動的話是否也是在上升沿和下降沿都進行計數處理,這樣的話怎樣設定可以保障計數器可以同時在兩個always 下進行計數,可以給一下大概的例程最好

2016-01-11 18:27:47

如圖是海德漢編碼器輸出信號調理電路,Z+,Z-為差分信號,電路的作用是將三角波信號經過比較器調理成方波信號,但我不是太懂原理,希望大家能指教一下。

2018-12-03 09:37:16

有人用過海德漢IK220卡讀取SSI編碼器角度么。運行海德漢自己給的讀SSI的VI,總是提示找不到卡。這是什么原因呢。

2017-04-14 15:52:22

我用labview對海德漢絕對式編碼器進行編程,設定一個幾毫秒的采樣周期,將讀取到的位置值經過計算轉化成速度值,并有過零判斷,但是讀出的轉速值波動較大,海德漢25位精度的,本身精度特別高,但是測試幾百轉的轉速波動能達到幾十轉,請問大家遇到過這種情況嗎?有什么可能的原因嗎?萬分感激。

2017-05-05 22:40:54

編碼器的原理是什么?編碼器可分為哪幾類?編碼器是如何進行接線的?編碼器軟件四倍頻技術是什么?

2021-08-04 06:08:39

編碼器是什么?編碼器工作原理是什么?

2021-10-19 09:59:08

編碼器是什么?編碼器主要分為哪幾種?編碼器測速的大致原理是什么?

2021-06-30 07:48:39

伺服電機的種類有哪些?伺服電機主要的作用是什么?編碼器的結構域工作原理是什么?編碼器的分類和特點有哪些?伺服電機與編碼器的工作是什么?

2021-06-28 08:11:44

編碼器的工作原理是什么?如何通過波形得出正反轉的判據呢?編碼器的程序結構如何實現?

2021-10-14 06:36:49

為什么在使用同步機做自整定的時候,整定的角度有時候偏差會比較大,會出現飛車現象。而更改編碼器后可以正常整定。請問編碼器什么情況下會導致這樣的問題。另外,斷電測試時候,編碼器會損壞的原因有哪些?(電源穩定)

2018-09-07 14:40:40

AVS編碼與DSP實現的視頻編碼器,不看肯定后悔

2021-06-08 06:01:15

為什么要用編碼器?STM32編碼器的原理是什么?

2021-11-24 07:32:10

UEC 111海德漢伺服驅動器銷售可維修,汕頭市羅克自動化科技有限公司全心全意為您服務!聯系人郭經理:*** UEC 111海德漢伺服驅動器 汕頭羅克自動化科技有限公司是專業的自動化設備

2020-03-13 16:54:33

UEC 112海德漢驅動器現貨大賣,汕頭市羅克自動化科技有限公司全心全意為您服務!聯系人郭經理:*** UEC 112海德漢驅動器 汕頭羅克自動化科技有限公司是專業的自動化設備維修中心

2020-03-13 16:57:05

cpld高手幫忙解答一下。感興趣的也可以提出點建議哈。網上一般是fpga與海德漢的編碼器接口通訊,但是fpga感覺有點浪費了,想直接用cpld來實現。

2011-05-30 22:45:23

為什么要用電機驅動?TB6612電機驅動怎么實現?為什么要用電機編碼器?電機編碼器怎么使用?

2021-10-20 07:36:53

什么是脈沖當量?伺服電機和編碼器有什么關系?伺服電機自帶編碼器為什么還要外加編碼器?

2021-11-01 06:20:22

海德漢伺服驅動器電源維修UVR150D北京HEIDENHAIN海德漢伺服驅動器維修常見故障有:上電無顯示、電源燈不亮、過電流、過電壓、欠電壓、過熱、過載、過速、缺相、抖動、編碼器異常、模塊損壞、接地

2021-11-16 07:27:27

編碼器的原理是什么?電機編碼器是如何進行接線的?編碼器接口的配置方式有哪些?使用編碼器時有哪些注意事項?

2021-08-02 10:21:23

增量式編碼器工作原理是什么?增量式編碼器的結構是由哪些部分組成的?光電旋轉編碼器使用方法是什么?單片機讀取光柵編碼器角度的方法是什么?

2021-06-30 07:29:18

電機系統編碼器電路板 配件日本發那科 配件編碼器驅動器 電機 電路板 機器人配件 回收拆機回收發那科編碼器傳感器海德漢控制器電路板西門子施耐德伺服回收發那科電機,回收發那科

2020-09-11 17:01:44

微信=電話 188-0743-0667回收發那科編碼器傳感器海德漢控制器電路板西門子施耐德伺服回收發那科電機,回收發那科A61L-0001-0093等驅動器、編碼器回收發那科FANUC編碼器,回收

2021-05-23 20:08:37

回收發那科編碼器傳感器海德漢控制器電路板西門子施耐德伺服***王姍姍回收發那科電機,回收發那科A61L-0001-0093等驅動器、編碼器回收發那科FANUC編碼器,回收A860-2020-T361

2020-11-05 21:42:34

公司的產品種類繁多,具有很好的品質保證,被廣泛應用于機床、自動化領域,尤其在半導體和電子制造業等領域。海德漢光電編碼器占有很大市場份額,而與之相配套的解碼設備不適合嵌入式系統應用。本文針對實驗用轉臺

2019-06-18 07:46:27

圖像數據處理的工作原理是什么?基于FPGA+DSP的圖像處理系統待如何去設計?

2021-06-02 06:54:28

基于FPGA+DSP的高速數據采集系統設計

2012-06-27 17:23:53

編碼器實現指標分析LDPC碼編碼器實現編碼器方案驗證與優缺點分析

2021-04-30 06:08:10

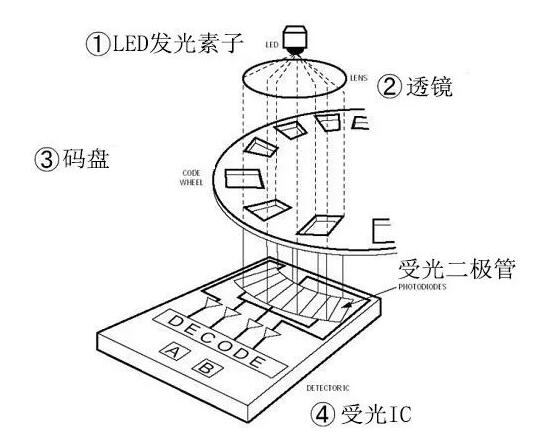

增量式光電編碼器結構和原理增量式光電編碼器結構如圖1所示。在它的編碼盤邊緣等間隔地制出n個透光槽。發光二極管(LED)發出的光透過槽孔被光敏二極管所接收。當碼盤轉過1/n圈時,光敏二極管即發出一個

2016-09-12 13:43:01

。目前想要選擇單一FPGA進行設計,但是又擔心片太貴預算超標,大家是否有合適的片子推薦?或者還是繼續采用FPGA+DSP的結構,大家有啥看法呢?

2018-05-11 11:54:50

如何利用DSP去設計一款MPEG-4編碼器?

2021-04-09 07:04:47

,生命周期縮短。實現功能強、性能指標高、抗干擾能力強、工作穩定可靠、體積小、功耗低、結構緊湊合理符合彈載要求的導引頭信號處理器已經勢在必行。過去單一采用DSP處理器搭建信號處理器已經不能滿足要求.FPGA+DSP的導引頭信號處理結構成為當前以及未來一段時間的主流。

2019-11-06 08:34:27

本文充分利用FPGA高速實時特點,采用并行處理及流水線設計,通過優化CAVLC編碼結構和level編碼子模塊,提高CAVLC編碼器的性能。

2021-04-28 06:34:13

,生命周期縮短。實現功能強、性能指標高、抗干擾能力強、工作穩定可靠、體積小、功耗低、結構緊湊合理符合彈載要求的導引頭信號處理器已經勢在必行。過去單一采用DSP處理器搭建信號處理器已經不能滿足要求.FPGA+DSP的導引頭信號處理結構成為當前以及未來一段時間的主流。

2019-08-19 06:38:12

編碼器的關鍵參數有哪些呢?怎樣使用STM32的編碼器功能去讀取編碼器反饋的脈沖數呢?

2022-01-26 07:54:42

雖說FPGA+DSP的數字硬件系統正好結合了兩者的優點,但有什么方法去證明FPGA+DSP系統中FPGA的關鍵技術是存在的呢?

2021-04-08 06:54:33

我想用FPGA+DSP做個聲相儀,有感興趣的小伙伴嗎?一起開發,在上海最好啦。先做原型機出來,然后再考慮產品化。私聊:QQ 4010087

2017-04-25 14:53:48

電機的旋轉編碼器輸出是5V的脈沖信號,DSP是3.3V供電的,這個接口怎么設計?

2013-04-08 14:11:56

信號。因為它們不同的感應原理,光編比磁編更容易失效。因為光編靠旋轉碼盤和光收發器配合工作。它們的距離非常近,但又不能接觸。但是在振動下和結構的間隙變大的情況下,碼盤會和光收發器碰撞。當光編碼器的運動部件...

2021-06-28 11:35:40

本文詳細介紹了一個測量各類海德漢編碼器的數據的通用且實用的模塊。該模塊基于Xilinx FPGA平臺和TI DSP平臺,使用和調試方便,使用者可快速掌握;通過了實驗和精度的檢測,實現了設計目的,工作可靠;模塊小巧,可以與上位機通信,可以很好的被結合到嵌入式系統中。

2021-04-30 07:01:32

日本發那科 配件編碼器驅動器 電機 電路板 機器人配件 回收拆機回收發那科編碼器傳感器海德漢控制器電路板西門子施耐德伺服***微信同步

2021-04-27 17:12:03

系列PLC模塊,回收三菱Q系列PLC模塊,回收發那科編碼器傳感器海德漢控制器電路板西門子施耐德伺服,回收發那科電機,回收發那科A61L-0001-0093等驅動器、編碼器,回收發那科fanuc編碼器

2021-09-11 09:27:33

請問下有人用LabVIEW對海德漢ik220計數卡過編程嗎?

2014-11-27 16:49:14

、DSP、ARM等器件直接進行并行通訊。實驗結果驗證了設計的正確性。可以看出,利用FPGA設計光電編碼器信號處理模塊,無論是設計過程,還是電路結構、都變得更加簡潔。另外,在應用中注意FPGA的時鐘周期應

2019-06-10 05:00:08

***同步長期回收發那科編碼器傳感器海德漢控制器電路板西門子施耐德伺服重慶回收發那科電機,回收發那科A61L-0001-0093等驅動器、編碼器沈陽回收發那科FANUC編碼器,回收

2021-10-16 09:59:02

介紹了一種基于FPGA+DSP 的數據采集與處理平臺,給出了系統實現的總體方案,并闡述了各部分硬件電路的設計。重點對FPGA 內部各主要功能模塊做了詳細闡述,對各個模塊的設計方法

2009-12-19 15:59:16 34

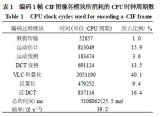

34 本文重點研究了AVS-P2熵編碼器的算法、結構以及利用FPGA實現的若干關鍵問題,給出了詳細的塊變換系數熵編碼器硬件結構,并通過了仿真驗證。實現中提出了一種新的2D-VLC碼表存儲

2010-08-06 16:37:38 24

24 增量型編碼器與絕對型編碼器的區別

編碼器如以信號原理來分,有增量型編碼器,絕對型編碼器。 增 量 型 編 碼 器 (旋轉

2009-09-26 17:36:29 2348

2348

編碼器,編碼器是什么意思

編碼器

編碼器(encoder)是將信號

2010-03-08 15:04:26 2868

2868 光電編碼器,光電編碼器是什么意思

光電編碼器光電編碼器,是一種通過光電轉換將輸出軸上的機械幾何位移量轉換成脈沖或

2010-03-08 15:20:40 1431

1431 光電編碼器原理結構圖

增量式光電旋轉編碼器??? 所謂編碼器即是將某種物理量轉換為數字格式的裝置。運動控制系統中的編碼器的

2010-03-08 15:24:23 15909

15909 摘要:在FPGA+DSP構建的便件平臺上,以鏈路口(LINKPORT)通信協議為根據,實現紅外圖像數據采集與顯示。重點描述紅外圖像數據采集與經過LINKPORT傳入DSP,圖像壓縮與經過LINKPORT傳出DSP以及圖像數據緩存與顯示,最后介紹了程序高度過程中的方法。樣機在實

2011-03-01 00:11:12 87

87 本文設計了一種基于FPGA的編碼器接口,用以進行編碼器和伺服驅動器DSP處理器之間的通訊,并且具有CRC校驗等糾錯功能。本文給出了硬件連接和FPGA程序設計流程

2011-04-06 11:49:48 4733

4733

介紹了Virtex2Ⅱ系列FPGA (現場可編程門陣列)的時鐘管理模塊DCM (數字時鐘管理器)的結構和功能,詳細分析了RS(Reed2Solomon)碼編碼器的工作過程,提出了一種連續RS編碼器設計方案,給出了硬件

2011-09-02 16:25:13 83

83 分析了光電編碼器4倍頻原理,提出了一種基于可編程邏輯器件FPGA對光電增量式編碼器輸出信號4倍頻、鑒相、計數的具體方法,它對提高編碼器分辨率與實現高精度、高穩定性的信號檢測

2011-11-03 15:13:16 75

75 接口 - 海德漢編碼器,全部產品接口介紹,各種接口技術。

2016-03-14 15:44:11 9

9 800Mbps準循環LDPC碼編碼器的FPGA實現

2016-05-09 10:59:26 37

37 基于FPGA的經濟型MPEG2運動圖像編碼器IP核設計

2016-08-30 15:10:14 9

9 基于FPGA+DSP實時圖像采集處理系統設計

2017-01-03 11:41:35 9

9 本文介紹了基于DSP和FPGA的編碼器信號測量及處理的通用模塊,對海德漢編碼器進行了概述等。

2017-10-13 18:17:29 19

19 所處理的數據量少,算法結構復雜,適于運算速度快,尋址靈活的DSP數字信號處理器進行處理。這里提出了一種FPGA+DSP相結合的實時圖像處理系統,并應用于傳像光線束傳遞圖像。CMOS實際采集的是光線束的出端圖像,FPGA將CMOS采集的Bayer格式的

2017-10-26 15:44:56 2

2 所處理的數據量少,算法結構復雜,適于運算速度快,尋址靈活的DSP數字信號處理器進行處理。這里提出了一種FPGA+DSP相結合的實時圖像處理系統,并應用于傳像光線束傳遞圖像。CMOS實際采集的是光線束的出端圖像,FPGA將CMOS采集的Bayer格式的

2017-10-31 17:00:34 12

12 電子編碼器是電氣火災監控探測器的設定工具。通過電子編碼器,可以讀寫探測器的地址編碼、讀寫探測器剩余電流的報警值。

2017-11-10 17:30:47 8612

8612 采用DSP 和FPGA 協同技術設計實現了一個高性能的MPEG24 視頻編碼器。FPGA 模塊完成視頻采集、YUV 分離、數據I/ O 等功能,而使用DSP 專一進行視頻壓縮編碼。針對DSP

2018-07-18 07:45:00 643

643

本文主要介紹了一種基于FPGA+DSP的視頻控制的智能交通燈設計。該交通燈由視頻采集、圖像處理和控制模塊組成,使用FPGA核心搭建專用高速視頻采集模塊,使用DSP處理器進行實時圖像運算,通過圖像算法提取車流量信息,最終結合模糊算法實現智能控制。

2018-01-09 14:15:41 1853

1853

FPGA+DSP的數字硬件系統正好結合了兩者的優點,兼顧了速度和靈活性。本文以導引頭信號處理系統為例說明FPGA+DSP系統中FPGA的關鍵技術。

2019-01-08 08:36:00 2449

2449

目前的視頻監控行業,基于DSP的H.264編碼器解決方案占有絕對優勢的市場份額,這是由DSP方案開發周期相對較短的特性決定的。在ASIC或FPGA方案仍處于研發階段時,DSP方案已捷足先登,并較好地解決了視頻監控行業中H.264編碼器方案從無到有的過程,為H.264在監控應用中走向成熟立下了汗馬功勞。

2018-10-29 08:21:00 12470

12470 高速中頻采樣信號處理平臺在實際應用中有很大的前景,提出采用FPGA+DSP的處理結構,結合高性能A/D和D/A處理芯片,設計了一個通用處理平臺,并對其主要性能進行了測試。

2018-10-18 16:36:48 4637

4637

大,運算簡單,但是要求運算速率高,可以用FPGA硬件來處理,上層所處理的數據量少,算法結構復雜,適于運算速度快,尋址靈活的DSP數字信號處理器進行處理。這里提出了一種FPGA+DSP相結合的實時圖像處理系統,并應用于傳像光線束傳遞圖像。CMOS實際采集的是光線束

2018-10-22 22:00:01 392

392 在信號處理領域中,基于FPGA+DSP的結構設計已經是系統發展的一個重要方向。隨著該系統設計的廣泛應用,功能變得更加豐富,成本日趨低廉。而在某些小型化應用的場合中,對系統體積的要求越來越高,因此

2019-02-22 14:37:58 7625

7625

透光型編碼器主要由四部分結構構成——①LED發光素子;②透鏡;③碼盤;④受光IC。

2019-10-09 15:35:30 3348

3348

現場可編程邏輯陣列(FPGA)資源豐富,結構靈活,近年來發展迅猛。針對其特點,本文設計了基于FPGA的增量式光電編碼器的接口電路,實現了對增量式編碼器脈沖信號的倍頻、鑒相及計數等功能。

2021-04-27 13:57:50 3886

3886

基于FPGA+DSP的高精度數字電源數據采集系統設計(開關電源技術發展綜述)-該文檔為基于FPGA+DSP的高精度數字電源數據采集系統設計講解文檔,是一份不錯的參考資料,感興趣的可以下載看看,,,,,,,,,,,,,,,,,

2021-09-24 11:32:01 34

34 基于FPGA+DSP彈載SAR信號處理系統設計

2021-12-27 18:58:51 21

21 增量型編碼器與絕對值型編碼器怎么選擇?在進行編碼器選擇時,增量型編碼器和絕對值型編碼器是兩種常見的選擇。增量型編碼器是一種基于脈沖計數的編碼器,通常由光電編碼器和霍爾編碼器組成。這種編碼器的主要優點

2023-05-08 11:28:33 1341

1341

編碼器是什么?編碼器有哪些分類及應用;編碼器是什么?在數字信號處理和通信系統中,編碼器是一種重要的設備,用于將原始數據轉換為字符序列或二進制碼序列。編碼器是一種可以同時測量物體位置和方向的蒿精度

2023-05-18 11:08:47 3137

3137

電子發燒友網站提供《基于FPGA+DSP模式的智能相機設計.pdf》資料免費下載

2023-10-08 10:37:16 0

0 磁性編碼器結構及原理,磁性編碼器的結構:磁性編碼器由兩個主要組合而成,讀頭和標尺。標尺是一個含有磁性條紋的輪子或桿,而讀頭則固定在機械裝置上,可以測量標尺相對于讀頭的位置。標尺上的磁條可以是南極

2024-01-22 11:24:40 274

274

編碼器(Encoder)是將輸入數據轉化為特定編碼表示的一種技術。對于不同類型的編碼器,評判其好壞可以從多個方面進行考量,包括編碼質量、速度、模型結構等。 編碼器的原理主要基于自動編碼器

2024-01-23 10:58:07 415

415

正在加载...

電子發燒友App

電子發燒友App

評論