在現(xiàn)代工業(yè)控制系統(tǒng)中,對電機(jī)的控制是其重要組成部分。編碼器作為電機(jī)角位移的檢測裝置,為系統(tǒng)提供重要反饋信號。本文介紹了一個(gè)適合嵌入式系統(tǒng)的基于DSP和FPGA的海德漢光電編碼器信號處理通用模塊,能夠測量和處理海德漢公司的高精度增量式編碼器信號和采用EnDat2.2雙向數(shù)字接口的絕對式編碼器信號。經(jīng)使用者的簡單操作,模塊適用于不同位數(shù)、不同類型的海德漢編碼器。該模塊通過實(shí)驗(yàn)、調(diào)試與測試,能有效快速工作,目前已應(yīng)用于實(shí)驗(yàn)用轉(zhuǎn)臺中。

引 言

隨著科學(xué)技術(shù)的飛速發(fā)展,自動控制系統(tǒng)在各領(lǐng)域中的應(yīng)用越來越多,特別是計(jì)算機(jī)自動控制系統(tǒng)已成為現(xiàn)代科學(xué)技術(shù)、軍事工程和現(xiàn)代工業(yè)等領(lǐng)域不可缺少的部分。因而,自動控制元件如作為動力裝置的各種電動機(jī)、發(fā)電機(jī)和作為信號變換的各種控制電機(jī)在各種控制系統(tǒng)中得到廣泛的應(yīng)用。要對被控對象進(jìn)行控制,不僅需要控制器和執(zhí)行機(jī)構(gòu),還需要反饋裝置。因此,編碼器作為電機(jī)的角度、速度、方向的檢測裝置,也得到了廣泛的應(yīng)用。編碼器又有旋轉(zhuǎn)變壓器、霍爾傳感器和光電編碼器。其中,光電編碼器精度高,抗干擾能力強(qiáng),接口簡單,使用方便,因而獲得了最廣泛的應(yīng)用[1]。

光電編碼器按編碼方式又主要有增量式編碼器和絕對式編碼器兩大類,前者具有分辨率高、價(jià)格較低、接口簡單等優(yōu)點(diǎn),然而在當(dāng)今工業(yè)中,無掉電記憶功能又對其應(yīng)用構(gòu)成了很大局限;后者結(jié)構(gòu)緊湊、體積小、接口數(shù)字化、抗干擾能力強(qiáng)、具有掉電記憶功能,在應(yīng)用中也越來越受重視[2]。

當(dāng)前市場上,德國海德漢公司的產(chǎn)品種類繁多,具有很好的品質(zhì)保證,被廣泛應(yīng)用于機(jī)床、自動化領(lǐng)域,尤其在半導(dǎo)體和電子制造業(yè)等領(lǐng)域。海德漢光電編碼器占有很大市場份額,而與之相配套的解碼設(shè)備不適合嵌入式系統(tǒng)應(yīng)用。本文針對實(shí)驗(yàn)用轉(zhuǎn)臺使用的海德漢編碼器設(shè)計(jì)出了增量式和絕對式的通用數(shù)據(jù)處理模塊。該模塊具有信號處理速度快、精度高、數(shù)據(jù)準(zhǔn)確、應(yīng)用靈活廣泛、使用和調(diào)試方便、成本低廉等優(yōu)點(diǎn),能很好滿足使用需求。

1 海德漢編碼器概述

1.1 高精度增量式編碼器

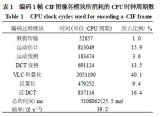

增量式編碼器是經(jīng)過光柵將位移轉(zhuǎn)換成周期性的電信號,再把這個(gè)電信號轉(zhuǎn)變成計(jì)數(shù)脈沖,用脈沖的個(gè)數(shù)表示位移的大小。其光柵由周期性刻線組成,通過計(jì)算自某點(diǎn)開始的增量數(shù)(測量步距數(shù))獲得位置信息。本模塊要測量的高精度海德漢增量式編碼器的光柵上還有刻有距離編碼參考點(diǎn)的軌道,加快參考點(diǎn)回零[3]。下圖1為某帶距離編碼的圓光柵。

圖1帶距離編碼參考點(diǎn)的圓光柵(ERA4480)

這些參考點(diǎn)彼此相距數(shù)學(xué)算法確定的距離。已過三個(gè)參考點(diǎn)的兩個(gè)脈沖后,后續(xù)電子設(shè)備就能找到絕對參考點(diǎn)。

1.2 高精度絕對式編碼器

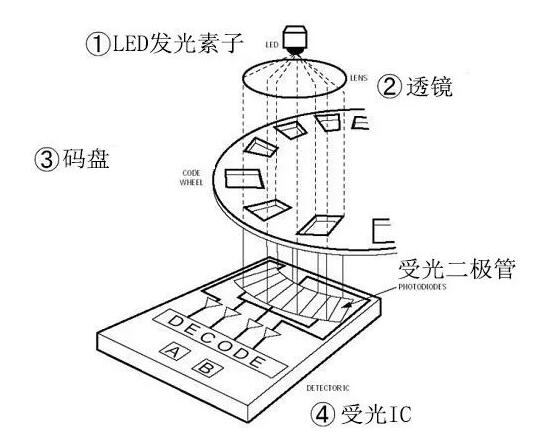

絕對式編碼器利用自然二進(jìn)制、循環(huán)二進(jìn)制( 格雷碼) 或PRC碼對碼盤上的物理刻線進(jìn)行光電轉(zhuǎn)換,將連接軸的轉(zhuǎn)動角度量轉(zhuǎn)換成相應(yīng)的電脈沖序列并以數(shù)字量輸出,其每一個(gè)位置對應(yīng)一個(gè)確定的唯一的數(shù)字編碼,因而具有掉電記憶功能[4]。

有時(shí),通過位置編碼器獲得位置值的數(shù)字驅(qū)動系統(tǒng)和反饋環(huán)還需要編碼器提供一些附加值。為使系統(tǒng)具有更高可靠性,編碼器還需具有錯(cuò)誤檢測和診斷功能。海德漢公司的Endat2.2數(shù)據(jù)接口是一種適用于編碼器的雙向數(shù)據(jù)接口,可傳輸絕對式或增量式編碼器的位置值,也能傳輸或更新保存在編碼器中的信息或保存新信息。由于采用串行數(shù)據(jù)傳輸方式它只需要4條線。數(shù)據(jù)傳輸保持與后續(xù)電子設(shè)備時(shí)鐘信號同步。傳輸?shù)臄?shù)據(jù)類型(位置值、參數(shù)或診斷信息等)通過后續(xù)電子設(shè)備發(fā)至編碼器的模式指令選擇[5]。

2 硬件設(shè)計(jì)

本模塊采用了DSP和FPGA結(jié)合的工作方式。DSP主要用于數(shù)字信號處理領(lǐng)域,非常適合高密度、重復(fù)運(yùn)算及大數(shù)據(jù)容量的信號處理。FPGA/CPLD器件一方面可實(shí)現(xiàn)硬件上的并行工作,非常適用于實(shí)時(shí)測控和高速應(yīng)用領(lǐng)域,另一方面物理機(jī)制和純硬件電路一樣,十分可靠,尤其是抗強(qiáng)電磁干擾。兩者結(jié)合,可實(shí)現(xiàn)寬帶信號處理,速度快且可靠性好[6]。

根據(jù)方案功能需求,設(shè)計(jì)模塊結(jié)構(gòu)圖如圖2所示:

?

?

圖2硬件結(jié)構(gòu)圖

圖中,模塊連接器為標(biāo)準(zhǔn)的DB15連接器,通過管腳配置,能相應(yīng)地與增量式編碼器和采用EnDat2.2接口的絕對式編碼器進(jìn)行信號交流。模塊的收發(fā)單元支持的是RS-485形式,差分信號和單端信號通過接口芯片進(jìn)行轉(zhuǎn)換。為了提高對高精度增量式編碼器數(shù)據(jù)測量精度,需在同一個(gè)增量編碼器上安裝4個(gè)讀數(shù)頭,各自測量增量式編碼器數(shù)據(jù),再合成得到位置值。這樣,板卡上讀取編碼器信號的接口設(shè)置有4個(gè)。

FPGA芯片選用賽靈思公司Spartan-3AN系列的XC3S700An,logic cells為10476。

實(shí)現(xiàn):①對增量信號的計(jì)數(shù)和參考信號的采集,在進(jìn)行計(jì)數(shù)達(dá)到參考碼道的數(shù)據(jù)后,進(jìn)行增量信號的清零;②對Endat2.2絕對式編碼器位置信號的采集;③在外同步時(shí)鐘上升沿到來前,保存計(jì)數(shù)處理,把數(shù)據(jù)存儲在雙口RAM中,等待DSP讀取。

本模塊選用的DSP芯片為TI公司的TMS320F28335,主頻可達(dá)150MHz。TMS320F28335增加了浮點(diǎn)運(yùn)算單元,在保持了原有DSP芯片優(yōu)點(diǎn)如強(qiáng)大控制和信號處理能力、C語言編程效率等優(yōu)點(diǎn)的同時(shí),節(jié)省了代碼執(zhí)行時(shí)間和存儲空間[7]。F28335通過GPIO端口與XC3S700An連接有4路地址線和16根數(shù)據(jù)線,可以接受16種編碼器信號。模塊中DSP部分開辟參數(shù)存儲區(qū),在中斷信號到來的時(shí)候讀取FPGA中數(shù)據(jù),完成數(shù)據(jù)合成,通過SCI串口把數(shù)據(jù)發(fā)送給主控機(jī)箱,電器形式為RS422。

3軟件設(shè)計(jì)及實(shí)現(xiàn)

根據(jù)硬件架構(gòu),分別對DSP和FPGA進(jìn)行軟件功能分析和具體編程實(shí)現(xiàn)。

FPGA部分使用Xilinx公司的ISE10.1開發(fā)軟件,采用Verilog語言,接受從接口管腳輸入的編碼器信號,相應(yīng)地實(shí)現(xiàn)對海德漢高精度增量式編碼器輸出并經(jīng)細(xì)分盒細(xì)分后的TTL脈沖計(jì)數(shù)和參考信號生成,或者是與絕對式編碼器的Endat2.2通信。DSP部分開發(fā)軟件采用TI公司的CCS5.2,使用C語言進(jìn)行編程。DSP完成對信號最終的位置合成處理,在這里,首先要定義編碼器的相關(guān)參數(shù),如:編碼器總刻度數(shù)、分辨率、帶參考碼道的增量式編碼器的參考點(diǎn)數(shù),還要考慮增量信號進(jìn)入FPGA前的細(xì)分?jǐn)?shù)(取決于IBV600),以及FPGA對TTL計(jì)數(shù)是否進(jìn)行四倍頻等。使用時(shí),根據(jù)具體編碼器類型進(jìn)行參數(shù)修改。

軟件實(shí)現(xiàn)了對高精度海德漢增量式編碼器和絕對式編碼器的位置值的讀取。下面將分別進(jìn)行介紹。

3.1測量增量式編碼器位置值

3.1.1 相關(guān)部分的FPGA設(shè)計(jì)

增量式編碼器是一旋轉(zhuǎn)式光電編碼器,根據(jù)軸所轉(zhuǎn)過的角度,輸出一系列脈沖。一般來說編碼器輸出有三相信號:A、B、Z。A、B兩相信號是相位相差90°的正交方波脈沖串,每個(gè)脈沖代表被測對象旋轉(zhuǎn)了一定的角度,A、B之間的相位關(guān)系則反映了被測對象的旋轉(zhuǎn)方向,即當(dāng)A相超前B相,轉(zhuǎn)動方向?yàn)檎D(zhuǎn);當(dāng)B相超前A相,轉(zhuǎn)動方向?yàn)榉崔D(zhuǎn)。Z信號是一個(gè)代表參考碼道的脈沖信號,可用于調(diào)零、對位。對象每旋轉(zhuǎn)一定角度時(shí),A、B兩者的脈沖發(fā)生變化,根據(jù)AB相位變化方向和脈沖個(gè)數(shù)來計(jì)算角位移[8]。當(dāng)AB相位變化為00 10 11 01 00時(shí),為輸出正轉(zhuǎn)計(jì)數(shù)脈沖,脈沖計(jì)數(shù)P加1;當(dāng)AB相位變化為00 01 11 10 00時(shí),為輸出反轉(zhuǎn)計(jì)數(shù)脈沖,脈沖計(jì)數(shù)P減1。相位變化幾次計(jì)數(shù)操作幾次。需要指出的是,相位的狀態(tài)變化只有嚴(yán)格按照上面8中方式改變時(shí),F(xiàn)PGA才進(jìn)行計(jì)數(shù)操作。在Verilog編程時(shí),可以把前一個(gè)AB相電平狀態(tài)和后一個(gè)AB相電平狀態(tài)組成一個(gè)散轉(zhuǎn)地址向量,然后把這個(gè)向量作為條件語句,進(jìn)行計(jì)數(shù)操作。比如,當(dāng)AB從00變?yōu)?0時(shí),向量就為0010,P=P+1。相反,若AB從10變?yōu)?0,這個(gè)向量就為1000,P=P-1。下面為FPGA讀取TTL數(shù)據(jù)并組成散轉(zhuǎn)地址向量的Verilog代碼:

always @(posedgeinClk)

begin

regUa1a2State <= {inIncUa1,inIncUa2};//讀取AB向量

if(regUa1a2State!=regAllState[1:0]) //狀態(tài)變化

begin

regAllState<= {regAllState[1:0],regUa1a2State};//組成新的散轉(zhuǎn)地址向量

regPulseStateChanged<= 1;

end

elsebegin

regPulseStateChanged<= 0;

end

end

另外,增量式編碼器不具有斷電記憶功能,每次啟動時(shí)都需確定零位。以前,只有一個(gè)零位參考點(diǎn)時(shí),有時(shí)需轉(zhuǎn)360°Z相位出現(xiàn)脈沖才能確定零位。高精度海德漢編碼器參考點(diǎn)碼道有若干個(gè)距離編碼參考點(diǎn),任一參考點(diǎn)經(jīng)過讀數(shù)頭時(shí),Z相位輸出脈沖。此時(shí),需要把之前的脈沖計(jì)數(shù)P保存下來(記為Q),P清零。這樣,每次Z相位輸出脈沖時(shí),P的數(shù)值就為上次經(jīng)過參考點(diǎn)后的脈沖數(shù),這是DSP確定零位和當(dāng)前參考點(diǎn)的重要依據(jù)。

FPGA測得4個(gè)讀數(shù)頭的4組信息,寫入雙口,等待DSP讀取。每組寫入雙口的數(shù)據(jù)有兩個(gè):①上一次過參考碼道時(shí)的計(jì)數(shù)增量計(jì)數(shù)RefPulseCnt(Q值),②增量計(jì)數(shù)PulseCnt(P值)。

3.1.2 相關(guān)部分的DSP設(shè)計(jì)

DSP程序中先生成增量式編碼器參考碼道的參考角度,也就是每個(gè)距離編碼參考點(diǎn)所對應(yīng)的脈沖數(shù)以及角度。又因?yàn)槊績蓚€(gè)參考點(diǎn)間脈沖數(shù)(即Q值)是不同且唯一的,可以根據(jù)讀取的FPGA雙口中的Q值確定最近經(jīng)過的參考點(diǎn),然后“查表”可以得到該參考點(diǎn)的角度。同時(shí),DSP讀取P值再乘以分辨率得到已當(dāng)前參考點(diǎn)后的角度,合成后兩者相加可以確定相應(yīng)讀數(shù)頭測得的位置值。分辨率為360°/刻度值總刻度數(shù)*進(jìn)入FPGA前細(xì)分?jǐn)?shù)*4(本模塊FPGA對TTL計(jì)數(shù)的處理實(shí)質(zhì)就是對AB路信號進(jìn)行了4倍頻)所有讀數(shù)頭過完零以后,輸入到DSP的4路讀數(shù)頭信號相對參考碼道的零點(diǎn)而言,都有一個(gè)絕對位置。一般來說,安裝讀數(shù)頭時(shí),要參考測量的單個(gè)讀數(shù)頭的位置值對4個(gè)讀數(shù)頭的位置要進(jìn)行調(diào)整,通常,相鄰兩個(gè)讀數(shù)頭之間相差90度最好。以任何一個(gè)讀數(shù)頭為基準(zhǔn),其他3個(gè)讀數(shù)頭的絕對位置相對基準(zhǔn)讀數(shù)頭而言的位置差為90°,180°,270°。為了簡化,以電路板輸入端口的1作為基準(zhǔn)量。合成位置量為A=(A1+A2+A3+A4-90-180-270)/4=(A1+A2+A3+A4-540°)/4,由于有安裝系統(tǒng)誤差,且要求合成位置值要大于0,計(jì)算時(shí)可以用520°替代540°。其范圍為(e,e+359.999999),e為誤差,這個(gè)時(shí)候要對360做求模處理,最后得到的合成值的工作范圍就為(0,359.9999999)。

3.2 測量絕對式編碼器的位置值

模塊參考海德漢公司提供的endat2.2相關(guān)技術(shù)手冊[5] [9],設(shè)置好參數(shù):根據(jù)編碼器位數(shù)和模式命令設(shè)置傳輸?shù)臄?shù)據(jù)位數(shù)ct_tx_oem_value、ct_rx_oem_value;需要傳送的附加信息個(gè)數(shù)ai_count;傳輸時(shí)鐘頻率參數(shù)freq_oem_value;恢復(fù)時(shí)間III ( tST)的設(shè)置參數(shù)freq_tst_value等。測量EnDat2.2的子文件根據(jù)參數(shù)轉(zhuǎn)換狀態(tài)機(jī),進(jìn)行相應(yīng)操作。另外,程序帶有電纜傳輸延遲測量模塊pdm。然后,按照下圖4的格式根據(jù)自己對信息的需求設(shè)置向編碼器傳輸?shù)男盘杁_in。在系統(tǒng)時(shí)鐘上升沿到來后立即通過start_trans信號控制開始與編碼器通信。接收編碼器數(shù)據(jù),讀出相應(yīng)d_out信號數(shù)據(jù),得到代表位置值的數(shù)據(jù)寫入雙口。

圖4endat2.2輸入數(shù)據(jù)“d_in”

上圖中,Mode bits為6位模式指令,最基本的編碼器發(fā)送位置值模式為000111。模式指令和其他參數(shù)的含義都可以在技術(shù)手冊中查到。

DSP從FPGA雙口RAM中讀取絕對式信號數(shù)據(jù),取有效位數(shù)后再乘以該絕對式編碼器的分辨率即得到位置信息。分辨率為360°/2^N,N是對應(yīng)的絕對式編碼器位數(shù)。

3.3 數(shù)據(jù)輸出

模塊通過RS422異步串行接口與上位機(jī)進(jìn)行通信,串行接口通過DSP的SCI口實(shí)現(xiàn),設(shè)計(jì)的模塊同時(shí)需要上位機(jī)發(fā)送的同步采樣頻率信號,將其與DSP相連,作為中斷信號啟動ISR功能。同時(shí),該信號管腳通過跳針把該外同步時(shí)鐘分給FPGA。這樣,保證兩者的時(shí)鐘源是統(tǒng)一的,然后DSP訪問FPGA的雙口就能實(shí)現(xiàn)正確讀取所需數(shù)據(jù)。過程時(shí)序示意圖如圖5所示:

?

圖5整體過程時(shí)序示意圖

如上圖所示,在t_1時(shí),F(xiàn)PGA即啟動與編碼器的通信,在t_2時(shí),F(xiàn)PGA把增量式編碼器脈沖計(jì)數(shù)或者絕對式編碼器信息存入雙口,在t_3時(shí),外同步時(shí)鐘上升沿啟動DSP中斷程序,讀取已經(jīng)存儲在FPGA雙口中的數(shù)據(jù)并合成位置值,合成量綱后通過RS422接口把絕對位置值傳遞給主控機(jī)箱。這樣,主控得到的數(shù)據(jù)是上一幀的數(shù)據(jù),即有一幀的延遲,時(shí)鐘頻率越大,延遲越小。因此,對采樣頻率有一定要求,不能太低。

4實(shí)驗(yàn)及數(shù)據(jù)分析

模塊設(shè)計(jì)好以后,需搭建平臺檢測是否實(shí)現(xiàn)功能。實(shí)驗(yàn)平臺如圖6所示:

圖6實(shí)驗(yàn)平臺

如圖6所示:打開電源控制開關(guān),然后從PC機(jī)把DSP和FPGA程序分別通過仿真器加載到F28335和XC3S700AN芯片中,打開主控機(jī)箱。最后,點(diǎn)擊CCS上的運(yùn)行鍵,撥動編碼器,可在CCS軟件界面右上方的變量觀察窗口觀察編碼器位置值。界面如下圖7所示:

?

圖7實(shí)驗(yàn)時(shí),觀察位置值的CCS界面

本實(shí)驗(yàn)中,所使用的編碼器為23位海德漢絕對式編碼器ECN1023,外同步時(shí)鐘源為500HZ。FPGA內(nèi)部頻率為10MHz,向Endat2.2輸入的頻率為64MHz的32分頻。觀察到該界面中位置值為359.8117303848267度。在實(shí)驗(yàn)中通過real-time與自動刷新功能還觀察到,界面上數(shù)據(jù)的變化與編碼器的轉(zhuǎn)動幾乎同步,編碼器停止轉(zhuǎn)動后,數(shù)據(jù)小數(shù)點(diǎn)后前3位之前的數(shù)據(jù)非常穩(wěn)定,第3、4、5位數(shù)據(jù)比較穩(wěn)定。由此可見,本模塊滿足了一定的測量速度和測量精度,能夠很好工作。

通過實(shí)驗(yàn)對本模塊的性能有了一定了解后,還需對精度進(jìn)行檢測。通過模塊與標(biāo)準(zhǔn)檢測儀同時(shí)測量一臺海德漢絕對式編碼器,360度測量正反相各測24組值。結(jié)果,正測RMS值為0.67角秒,極差為1.9角秒;反測RMS值為0.76角秒,極差為2.2角秒。兩組誤差曲線圖如下圖8所示:

?

圖8正反轉(zhuǎn)檢測兩組誤差數(shù)據(jù)曲線

從圖中觀察到,從0到23的24組數(shù)據(jù)皆是從0度到36度變化時(shí)測量得到的。如圖所示,兩組誤差曲線基本重合,可在最大誤差點(diǎn)加個(gè)修正值減小誤差。

結(jié)語

編碼器應(yīng)用廣泛。本文詳細(xì)介紹了一個(gè)測量各類海德漢編碼器的數(shù)據(jù)的通用且實(shí)用的模塊。該模塊基于Xilinx FPGA平臺和TI DSP平臺,使用和調(diào)試方便,使用者可快速掌握;通過了實(shí)驗(yàn)和精度的檢測,實(shí)現(xiàn)了設(shè)計(jì)目的,工作可靠;模塊小巧,可以與上位機(jī)通信,可以很好的被結(jié)合到嵌入式系統(tǒng)中。目前,本模塊已用于實(shí)驗(yàn)轉(zhuǎn)臺用的增量式和絕對式編碼器數(shù)據(jù)的處理,擬結(jié)合到實(shí)驗(yàn)室驅(qū)動控制機(jī)箱中,正進(jìn)一步開發(fā)它對海德漢絕對式編碼器Endat2.2附加信息的測量和處理。

電子發(fā)燒友App

電子發(fā)燒友App

評論