我們知道XDC與UCF的根本區別之一就是對跨時鐘域路徑(CDC)的缺省認識不同,那么碰到FPGA設計中常見的CDC路徑,到底應該怎么約束,在設計上又要注意些什么才能保證時序報告的準確性?

CDC的定義與分類

CDC是Clock Domain Crossing的簡稱,CDC時序路徑指的是起點和終點由不同時鐘驅動的路徑。在電路設計中對這些跨時鐘域路徑往往需要進行特別的處理來避免亞穩態的產生,例如使用簡單同步器、握手電路或是FIFO來隔離。

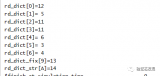

安全的CDC路徑

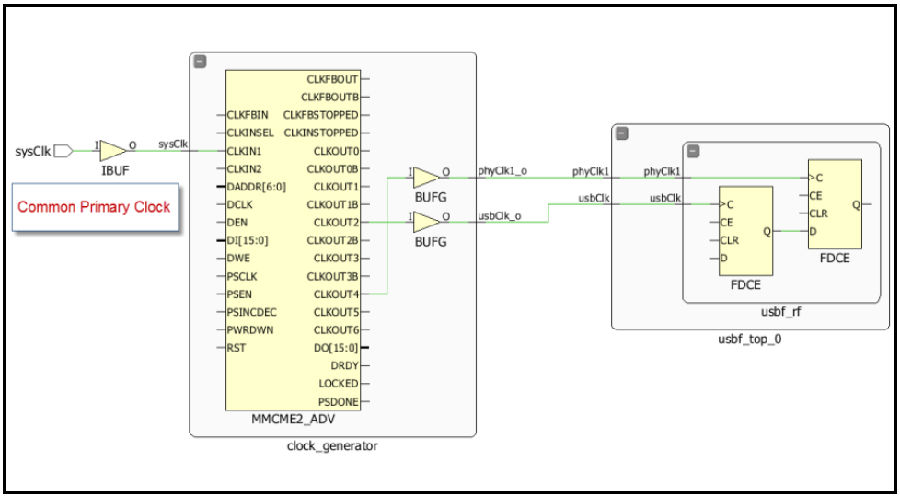

所謂安全的CDC路徑是指那些源時鐘和目標時鐘擁有相同的來源,在FPGA內部共享部分時鐘網絡的時序路徑。這里的安全指的是時鐘之間的關系對Vivado來說是全透明可分析的。

?

不安全的CDC路徑

不安全的CDC路徑則表示源時鐘和目標時鐘不同,且由不同的端口進入FPGA,在芯片內部不共享時鐘網絡。這種情況下,Vivado的報告也只是基于端口處創建的主時鐘在約束文件中所描述的相位和頻率關系來分析,并不能代表時鐘之間真實的關系。

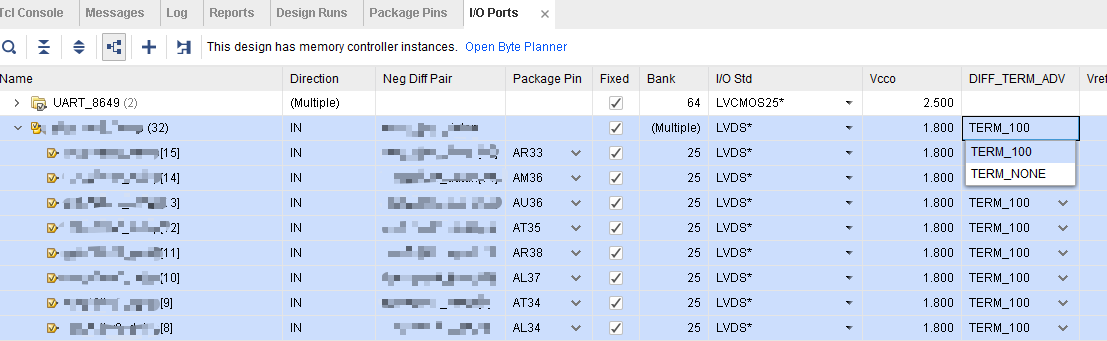

在Vivado中分析CDC

在ISE中想要快速定位那些需要關注的CDC路徑并不容易,特別是要找到不安全的CDC時,因為ISE缺省認為所有來源不同的時鐘都不相關且不做分析,要報告出這類路徑,需要使用ISE Timing Analyzer (TRCE) ,并加上 “-u” (表示unconstrained)這個選項。

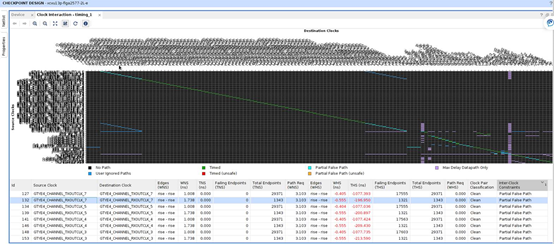

在Vivado中則容易許多,我們可以使用report_clock_interaction命令(GUI支持)來鑒別和報告設計中所有的時鐘關系。執行命令后會生成一個矩陣圖,其中對角線上的路徑表示源時鐘與目標時鐘相同的時鐘內部路徑,其余都是CDC路徑。

Vivado還會根據網表和已讀入的約束分析出CDC路徑的約束情況,并分顏色表示。例如綠色代表有時序約束,紅色代表不安全的CDC路徑但是沒有約束時序例外,橙色表示有部分路徑已約束為false path的不安全CDC路徑。

矩陣下方是時鐘關系表格,可以就各種條件進行篩選和排序,方便定位CDC路徑。建議的做法是:首先,對“Common Primary Clock”排序(顯示為Yes 或No),這么做可以快速鑒別出那些安全和不安全的CDC路徑,接著觀察對應的“Inter-Clock Constraints”欄內的內容,判斷已讀入的XDC中是否對這類路徑進行了合理的約束。

第二步,可以對“Path Req (WNS)”由小到大進行排序,找到那些數值特別小(例如小于100ps)或是顯示為“Unexpanded”的CDC路徑,結合是否共享“Common Primary Clock”來鑒別此類路徑,作出合理的約束。

過小的Path Req (WNS)一般都表示此類跨時鐘域路徑缺少異步時鐘關系或其它時序例外的約束,如果兩個時鐘連“Common Primary Clock”也不共享,則100%可以確認為異步時鐘,應該加上相應的時鐘關系約束。

顯示為“Unexpanded”的時鐘關系,表示Vivado在一定長度(缺省為1000)的周期內都沒有為兩個時鐘的頻率和相位找到固定的關系,則無法推導出相應的Path Req 約束值。此類CDC需要特別留意,也要加上異步時鐘關系約束。

這個矩陣還支持交互式的時序分析,選中任意一個方框,右鍵顯示下拉菜單:選擇Report Timing,會報告出這一格代表的時鐘域(本時鐘域或是跨時鐘域)內最差的時序路徑;選擇 Set Clock Groups則可以設置時鐘關系約束并添加到XDC文件中。

CDC的設計與約束

CDC路徑在FPGA設計中普遍存在,在設置相應的約束前,必須了解設計中采取了怎樣的方法來處理跨時鐘域路徑。

簡單同步器

對于單根跨時鐘域路徑,一般采用簡單同步器(Simple Synchronizer),就是由至少兩級CE端和Reset/Clear端接死的寄存器序列來處理。

這種情況下,為了更長的平均無故障時間MTBF(Mean Time Between Failures),需要配合一個ASYNC_REG的約束,把用作簡單同步器的多個寄存器放入同一個SLICE,以降低走線延時的不一致和不確定性。

set_property ASYNC_REG TRUE [get_cells [list sync0_reg sync1_reg]]

在XDC中,對于此類設計的CDC路徑,可以采用set_clock_groups來約束。

set_clock_groups -asynchronous -group [get_clocks -include_generated_clocks clk_oxo ] \

-group [get_clocks -include_generated_clocks clk_core ]

用FIFO隔離CDC

在總線跨時鐘域的設計中,通常會使用異步FIFO來隔離。根據FIFO的實現方式不同,需要加入不同的XDC約束。

Build-in硬核FIFO

這種FIFO實際上就是用FPGA內部的BRAM來搭建,所有控制邏輯都在BRAM內部,是推薦的FIFO實現方式。其所需的XDC也相對簡單,只要像上述簡單同步器的時鐘關系約束一樣用set_clock_groups將讀寫時鐘約束為異步即可。

帶有格雷碼控制的FIFO

為了在亞穩態下做讀寫指針抽樣也能正確判斷空滿狀態,設計中也常用一種帶有格雷碼控制的FIFO來實現異步時鐘域的隔離。計數器和讀寫指針等需要用BRAM外部的邏輯搭建,這樣的結構就不能簡單約束set_clock_groups,還要考慮這些外部邏輯如何約束。

如下圖所示FIFO,在存儲器外部有一些用FPGA邏輯搭建的寫指針和讀指針控制,分屬不同的時鐘域,存在跨時鐘域的時序路徑。

此時如果僅將讀寫時鐘用set_clock_groups約束為異步時鐘,相當于設置從A到B和從B到A的路徑全部為false path。根據《XDC約束技巧之時鐘篇》所列,false path的優先級最高,很顯然這么做會導致所有跨讀寫時鐘域的路徑全部不做時序分析,讀寫指針和相關控制邏輯也就失去了存在的意義。

所以建議的做法是不設set_clock_groups約束,轉而采用set_max_delay來約束這些跨時鐘域路徑。以寫入側舉例,一個基本的原則就是約束從cell1到cell2的路徑之間的延時等于或略小于cell2的驅動時鐘一個周期的值。讀出側的約束同理。

set_max_delay $delay –from [get_cells cell1] –to [get_cells cell2] –datapath_only

如果用戶使用Vivado的IP Catalog來產生此類FIFO,這樣的XDC會隨IP的源代碼一起輸出(如下所示),使用者僅需注意確保這個FIFO的讀寫時鐘域沒有被用戶自己的XDC約束為false path或是異步clock groups 。

set_max_delay -from [get_cells …../rd_pntr_gc_reg[*]] -to [get_cells …../Q_reg_reg[*]] \

-datapath_only [get_property PERIOD $rd_clock]

set_max_delay -from [get_cells …../wr_pntr_gc_reg[*]] -to [get_cells …../Q_reg_reg[*]] \

-datapath_only [get_property PERIOD $wr_clock]

自2013.4開始,Vivado中還提供一個稱作methodology_checks的DRC檢查,其中包含有對此類異步FIFO的max delay約束與時鐘域clock groups約束的沖突檢查。

CDC約束方案的對比

CDC路徑在FPGA設計中普遍存在,不少公司和研發人員都有自己偏愛的約束方式,這些方式通常有各自適用的環境,當然也各有利弊。

全部忽略的約束

最大化全部忽略CDC路徑的約束,即采用set_clock_groups 或是set_false_path對時鐘關系進行約束,從而對跨時鐘域的路徑全部忽略。

示例:set_clock_groups -asynchronous -group clkA -group clkB

優勢:簡單、快速、執行效率高。

劣勢:會掩蓋時序報告中所有的跨時鐘域路徑,容易誤傷,不利于時序分析。

使用datapath_only約束

datapath_only是從ISE時代的UCF中繼承過來的約束,在XDC中必須作為一個選項跟set_max_delay配合使用,可以約束在時鐘之間,也可以對具體路徑進行約束。

示例:set_max_delay 10 -datapath_only -from clkA -to clkB

優勢:簡便、執行效率較高。

劣勢:1) 需要特別留意是否設置了過于嚴格的約束,因為使用者經常會使用較快的時鐘周期來約束跨時鐘域路徑 。2) 注意約束優先級的關系,是否跟設計中其它的約束有沖突。3) set_max_delay而沒有配套設置set_min_delay的情況下,同一路徑只做setup分析而不做hold分析。

逐條進行時序例外約束

對設計中的CDC路徑分組或逐條分析,采用不同的時序例外約束,如set_false_path,set_max_delay和set_multicycle_path等來約束。

示例:set_false_path -from [get_cells a/b/c/*_meta*] -to [get_cells a/b/c/*_sync*]

優勢:靈活、針對性好、便于時序分析和調試。

劣勢:1) 逐條約束會占用大量時間來調試和分析,效率低下。2) 時序例外的優先級比較復雜,多種時序例外約束共存的情況下,很容易產生意想不到的沖突,進一步增加調試時間,降低效率。3) 這么做極容易產生臃腫的XDC約束文件,而且時序例外的執行更耗內存,直接導致工具運行時間變長。

小結

CDC路徑的分析和約束不僅在FPGA設計中至關重要,也是數字電路設計領域一個非常重要的命題。IP提供商、EDA公司都有不少關于CDC的技術文檔。Vivado相比于Xilinx.上一代產品ISE,已經在CDC的鑒別和分析方面有了很大改進,XDC相比于UCF,在CDC路徑的約束上也更為高效,覆蓋率更高。

希望本篇短文可以幫助Vivado的用戶快速掌握對FPGA設計中CDC路徑的鑒別、分析和約束方法,提高設計效率。

電子發燒友App

電子發燒友App

評論