在實時操作系統中,線程調度花費的時間是一個值得關注的影響系統實時性的因素,尤其是在系統需要處理緊急的任務時,線程調度的時間更是不能忽略。本文給出了一種在GD32單片機上測量RT-Thread系統線程調度時間的方法。

2022-01-20 07:18:38

中,數字信號處理系統經常要進行高速、高精度的FFF運算。現場可編程邏輯陣列(FPGA)是一種可定制集成電路,具有面向數字信號處理算法的物理結構。用FPGA實現FFT處理器具有硬件系統簡單、功耗低的優點

2019-07-03 07:56:53

GSM系統控制信道分析王昌花一種基于優先級的獨立任務調度算法與實現蔣燕基于FPGA的FSK調制解調器設計鄭波單相正弦波逆變器設計孔維坤合成孔徑雷達成像技術研究史明松深空通信中調制技術研究宋鑫基于OFDM的通...

2021-07-06 06:13:38

【摘要】:Xen由于其很低的性能損失,而逐漸成為最受歡迎的虛擬化管理工具之一.但是,它的SEDF調度算法存在在SMP下不能支持全局負載平衡的問題.本文針對此問題提出一種名為IEDF的改進算法.該算法

2010-04-24 10:03:16

基于嵌入式圖像處理平臺的實時多目標識別算法人工智能技術與咨詢 昨天本文來自《科學技術與工程》,作者王旭輝等摘 要提出了一種適用于空間觀測任務的實時多目標識別算法,它基于DSP和FPGA組合的圖像處理

2021-12-21 07:02:06

可重構體系結構分為哪幾種?典型動態可重構系統結構有哪幾種?動態可重構系統有哪些應用實例?

2021-04-28 06:13:00

可重構體系的結構是由哪些部分組成的?可重構制造系統有哪些應用?

2021-09-30 06:18:17

可重構平臺下AES算法的流水線性能怎么優化?

2021-04-28 06:46:52

重用機床的組成模塊特征,進而將可重用機床的模塊編碼系統分為模塊主碼、模塊接口特征碼和模塊圖紙管理碼三部分組成。通過計算總相似系數得到與目標模塊最接近的模塊,給出了可重用機床模塊選擇算法的流程,并以可重用機床中的橫梁為例進行了驗證。關鍵詞:可重用機床;編碼技術;重構算法[hide][/hide]

2009-05-17 11:58:53

一、介紹調度器是常用的一種編程框架,也是操作系統的拆分多任務的核心,比如單片機的裸機程序框架,網絡協議棧的框架如can網關、485網關等等,使用場合比較多,是做穩定產品比較常用的編程技術二、原理1

2022-02-17 07:07:16

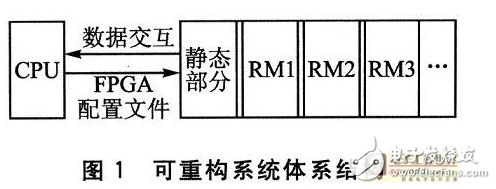

可重構設計是指利用可重用的軟、硬件資源,根據不同的應用需求,靈活地改變自身體系結構的設計方法。FPGA器件可多次重復配置邏輯的特性使可重構系統成為可能,使系統兼具靈活、便捷、硬件資源可復用等性能

2011-05-27 10:22:36

/OSII繼承了μC/OS的算法,有執行效率高、占用空間小、實時性強和可擴展性好等特點,被移植到幾乎所有類型的CPU上,成為在嵌入式領域非常有影響力的RTOS。然而,由于該實時內核是為8位CPU設計的,對于那些具有優先級算法硬件指令的CPU,僅做移植是很不夠的。

2019-11-06 06:40:56

我看官方手冊說設置時configMAX_PRIORITIES不能超過32,有沒有誰試過改成255的或者更大的,小弟改了幾下都不行!還有能問問FreeRTOS的任務調度算法和RT_Thread的不一樣,RT_Thread的算法和uCosIII的調度算法一樣呢?

2020-06-18 09:00:40

那些具有優先級算法硬件指令的CPU,僅做移植是很不夠的。 1 基于優先級的任務調度 一個基于優先級的實時多任務內核的任務調度機制需要實現下面三個核心的處理功能: ◆ 將任務置于就緒態; ◆ 將

2011-04-16 09:18:13

纏繞在一起,必須仔細處理以防不測。那么換一種思路,如果把主程序全部放入(定時)中斷中會怎么樣?這么做至少可以立即看到幾個好處: 系統可以處于低功耗的休眠狀態,將由中斷喚醒進入主程序; 如果程序跑飛,則中斷

2011-11-23 08:51:19

FPGA可重構設計的基礎是什么?基于FPGA的可重構系統結構是怎樣構成的?基于FPGA的可重構系統的應用有哪些?

2021-04-30 07:16:04

由于可重構系統的研究歷史很短,目前尚未形成標準的結構形式,在此僅根據已有的應用做初步分析。 按重構的粒度和方式,可重構系統可以粗略地分為兩種。一種是粗粒度重構單元的模塊級重構,即重構時改變

2011-05-27 10:24:20

可重構結構是一種可以根據具體運算情況重組自身資源,實現硬件結構自身優化、自我生成的計算技術。動態可重構技術可快速實現器件的邏輯重建,它的出現為處理大規模計算問題提供了一種兼具通用處理器靈活性

2019-07-10 07:56:06

自適應濾波器設計是典型的多參數組合優化問題,利用一種改進的粒子群優化算法(MPSO)來優化設計自適應LMS濾波器.將濾波器設計問題轉化為濾波器參數優化的問題,利用改進的粒子群算法MPSO搜索整個參數

2010-04-26 16:13:08

硬件+軟件看門狗監測多任務的原理是什么?如何去實現一種硬件+軟件看門狗監測多任務方案?

2021-08-05 07:55:02

操作系統執行任務調度而實現宏觀上的“并發運行” 。從宏觀上不同的任務并發運行,好像每個任務都有自己的 CPU一樣。其實在單一CPU的情況下,是不存在真正的多任務機制的,存在的只有不同的任務輪流

2022-04-14 09:14:53

FPGA芯片是由哪些部分組成的?如何去實現一種基于FPGA芯片的可重構數字電路設計?

2021-11-05 08:38:57

怎樣去分析可重構系統中軟/硬件任務間通信?什么是可重構系統中消息隊列通信機制?如何對可重構系統中任務間的通信機制進行模擬實驗?

2021-04-27 06:03:34

您好,我是新手用FPGA設計可重構硬件。我只是想了解它。誰能給我一些建議?哪些書籍文件適合我參考?網站或論壇也不錯。謝謝?

2020-06-11 10:05:15

一種基于NiosⅡ的可重構DSP系統設計

2021-03-17 06:41:55

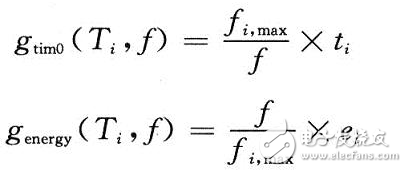

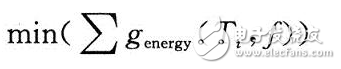

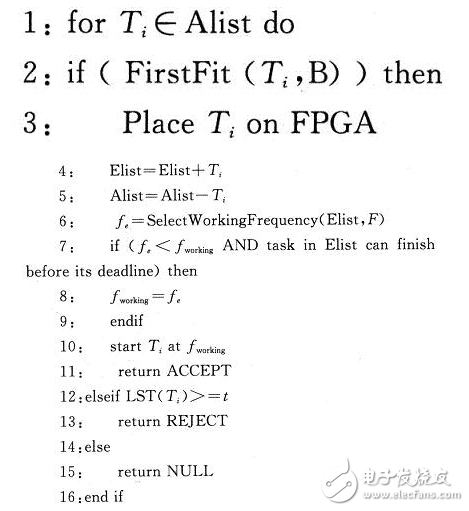

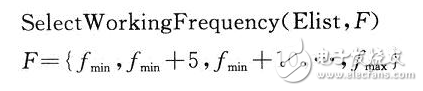

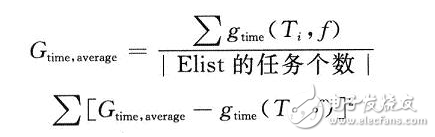

如何降低可重構系統的整體功耗?有什么方法能使可重構系統的性能和功耗需求之間達到平衡?

2021-04-08 07:09:23

慕課電子科技大學.嵌入式系統.第七章.任務管理與調度.任務管理2-就緒算法和任務切換0 目錄7 任務管理與調度7.2 任務管理2-就緒算法和任務切換7.2.1課堂重點7.2.2測試與作業8 下一章0

2021-12-21 06:19:47

的改造。主要的方法有:對內核的改造,如雙內核途徑和搶占內核途徑,細化內核的時鐘粒度。另一種改造的主要途徑是內核的調度策略。進程調度算法優劣決定系統的實時性。本文就是通過改善Linux的調度算法來提升Lin...

2021-11-05 08:15:04

.。在這種超載情況下,使任務集內各任務滿足各自的時限,嵌入式操作系統必須保證在確定的時間內對事件進行處理,因此必須要有一個良好的任務調度算法。周期任務和非周期任務是實時嵌入式系統中的常見任務類型,系統實時任...

2021-12-21 06:24:18

開發成本。UML技術是當前系統開發中常用的面向對象技術,它吸取了面向對象技術領域中其他流派的長處,同時也包括非面向對象的方法,是一種定義良好、易于表達、功能強大且普遍適用的面向對象建模技術。本文把該技術運用到嵌入式硬件系統的描述中,通過分析、設計、實現,初步得到嵌入式硬件系統的模型。

2019-08-28 07:16:00

本文提出的通過微處理器加FPGA結合串行菊花鏈實現可重構的方式,實現了動態可重構FPGA結構設計的一種應用。

2021-05-10 06:22:19

可重構結構是一種可以根據具體運算情況重組自身資源,實現硬件結構自身優化、自我生成的計算技術。動態可重構技術可快速實現器件的邏輯重建,它的出現為處理大規模計算問題提供了一種兼具通用處理器靈活性和ASIC電路高速性的解決方案。

2019-08-13 07:56:00

提出了一種可用于手持移動終真個可重構天線的設計方法。該天線安裝有兩個RF-PIN開關,可通過一個直流控制電路控制開關的狀態,以使 線的極化方式和輻射方向圖發生變化,從而實現極化可重構和方向圖可重構。該天線結構緊湊,易于與電路板集成在一起,在移動終端中有良好的應用價值。

2019-09-26 07:49:45

日前,Altium 宣布推出另一款面向桌面 NanoBoard 可重構硬件開發平臺的全新子板,進一步幫助電子設計人員輕松利用可編程硬件的優勢。這款最新插入式子板采用 780 BGA 封裝,內置

2019-07-25 06:07:43

什么是可重構技術? 它有哪些優點?可重構智能儀器的硬件怎樣去設計?可重構智能儀器的軟件設計怎樣去設計?

2021-04-29 06:23:17

本文基于現代測控系統的通用化結構特征和可重構的現場可編程門陣列FPGA技術的發展,提出一種可重構測控系統(Reconfigurable Mo—nitoring System,RMS)的設計構想,并給出其應用實例。

2021-04-30 06:40:43

本文介紹了一種基于ARM的視頻監控系統的設計方案,采用軟壓縮算法,討論了系統的硬件和軟件設計。

2021-06-08 06:27:10

求大神分享一種基于比特表的實時多任務新調度算法

2021-04-28 06:21:07

求大神分享一種高檔FPGA可重構配置方法

2021-04-29 06:16:54

,提出一種支持可重構單元陣列快速容錯的輔助布線電路,該電路結構由二維的輔助布線模塊構成,每個輔助布線模塊可以讀取并修改所在可重構單元的可編程開關配置數據.可重構單元陣列容錯時,輔助布線電路代替外部軟件執行

2010-04-24 09:01:53

粒子群算法城鎮能源優化調度問題,一、簡介1 粒子群算法的概念粒子群優化算法(PSO:Particle swarm optimization) 是一種進化計算技術(evolutionary

2021-07-07 06:04:36

可重構計算技術概述隨著20世紀80年代中期Xilinx公司推出其第一款現場可編程門陣列(FPGA)以來,另一種實現手段——可重構計算技術逐漸受到人們的重視,因為它能夠提供硬件功能的效率和軟件的可編程性,隨著可編程器件容量根據摩爾定律的不斷增大和自動設計技術的發展,可重構技術正迅速地成熟起來。

2019-07-29 06:26:03

針對多任務系統而言,調度是指根據一定的算法.將CPU 分配給符合條件的任務使用,不同的系統任務調度機制不同。本文介紹VxWorks系統的任務調度策略和算法.分析優先級倒置產

2008-12-16 14:11:26 10

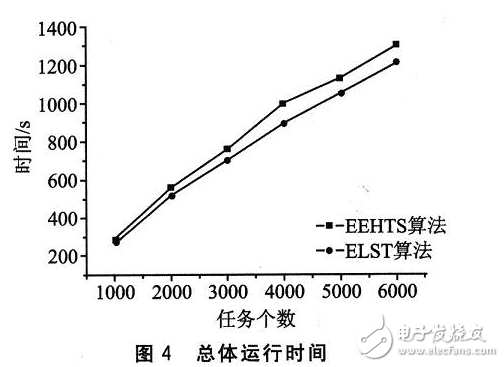

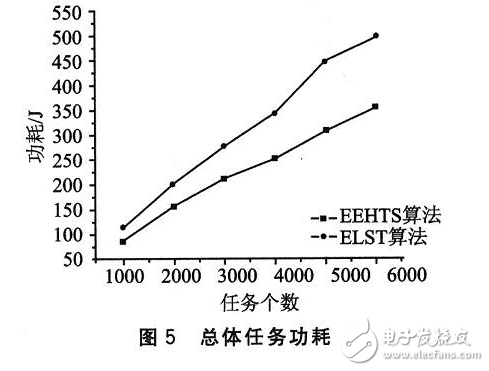

10 與實時任務的可調度分析不同,實時DVS調度在保證任務截止時間限制同時,還要關注任務執行的處理器功耗。功耗研究一段時間的累積效果,傳統基于最壞執行時間的任務調度模

2008-12-16 23:55:11 12

12 任務調度問題是一個NP難題,其算法是一個重要研究方向。該文通過對任務調度模型及已有免疫算法進行研究和比較,提出一種基于實數編碼免疫算法的任務調度算法。討論問題的編

2009-04-08 09:00:14 15

15 任務調度是網格研究的核心問題之一,在研究網格任務調度問題的基礎上,利用模糊聚類思想提出將網格任務與資源進行混合模糊聚類的網格獨立任務調度算法,該算法將最適合的

2009-04-10 09:27:07 14

14 提出一種基于樹型計算網格的自適應調度算法,實現對小粒度獨立任務和用戶大作業的自適應最優調度。通過對網格環境的實時檢測,給出了基于節點負載狀況、節點任務執行時

2009-04-17 08:58:08 21

21 針對網格任務調度的動態特性,提出一種改進的遺傳算法——動態遺傳算法(DGA),設計了新的編碼機制和適應度函數,以及相應的選擇、交叉和變異算子。根據網格系統各服務節點的

2009-04-22 08:40:49 18

18 主要討論常見的幾種多任務實時性處理算法的優缺點,提出一種更能滿足多任務實時性處理的算法——基于比特表的時間片算法。這種算法主要是把常規的比特表中的任務按照時間

2009-05-15 15:02:59 11

11 基于Multi-Agent提出了一種新的分布式測控系統動態任務調度算法。該算法采用接收者啟動的調度策略,根據各主機負載狀態,在系統運行過程中動態遷移任務,有效地提高了系統效

2009-05-16 11:35:43 15

15 本文基于已有的OPC Server 實時任務模型,設計了處理混合任務集的動態調度算法(基于截止期優先)和實現方式。該算法實現了對混合任集可調度性的判斷,可以完成有硬實時性要

2009-05-31 15:36:16 13

13 網格任務調度算法是影響網格成功與否的關鍵技術之一。本文總結了網格計算系統的體系結構和特征,分析了網格任務調度算法的基本原理和性能指標,并對各種調度策略和算法進

2009-08-14 10:27:27 10

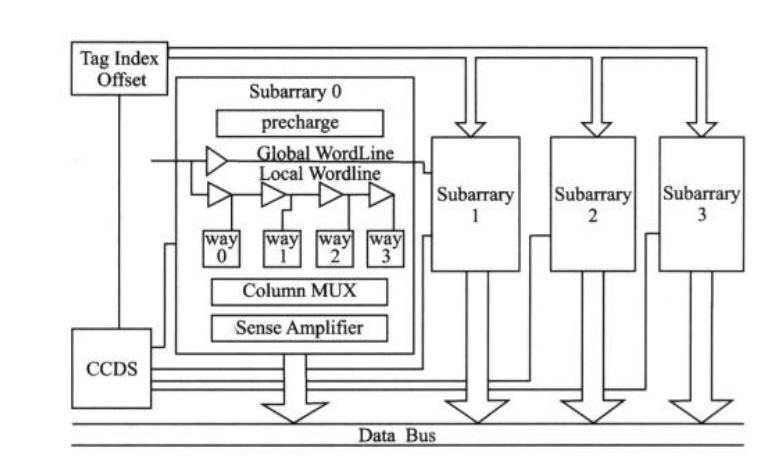

10 可重構硬件操作系統技術:為了充分發揮可重構計算的高性能和可編程能力, 需要將可重構資源和硬件任務納入到操作系統管理范疇. 因此面向可重構計算的操作系統技術—可重構硬

2009-10-06 09:41:51 23

23 該文提出了一種面向應用優化的片上總線調度策略。以系統通信事件信息為基礎,使用最小任務松弛時間與最小總線空閑時間相結合的調度策略,在優先保證滿足任務實時要求的基

2009-11-18 13:51:23 5

5 針對多任務系統而言,調度是指根據一定的算法.將CPU 分配給符合條件的任務使用,不同的系統任務調度機制不同。本文介紹VxWorks系統的任務調度策略和算法.分析優先級倒置產生

2009-11-27 16:26:41 13

13 在軍事信息網格中,某些特殊任務需要優先被調度執行,另外由于網格資源的動態性,會造成某些任務被映射而得不到調度執行。本文根據經典的Min-min算法提出了一種基于優先權

2010-01-22 13:55:51 8

8 針對現有流媒體算法在異構環境下性能惡化的問題,論文提出一種支持用戶異構性的可重構流媒體調度算法——RSMS 算法。該算法引入了追趕流的概念,能重構追趕流的速率來服務

2010-02-08 15:39:23 7

7 文中利用SystemC搭建了一種動態可重構系統的硬件任務管理模型,該模型可根據不同的管理策略和重構資源進行調整。仿真實驗結果表明,通過模型仿真獲得硬件任務,在指定管理策略和資源

2011-12-07 14:13:04 16

16 在網格環境中,如何對任務進行高效調度是當前研究的熱點問題。目前Min-Min調度算法是一個簡單、快速、有效的算法,但它很難滿足網格任務對服務質量的要求。在獨立型的任務調度模

2012-07-06 15:09:14 21

21 針對Hadoop0.20.0中任務調度算法存在的不足,提出一種基于改進遺傳算法(IGA)的任務調度算法。IGA算法對初始化種群、交叉和變異操作進行了一些改進,并引入了最優保留策略和加速進

2012-12-17 10:57:00 0

0 uCOS-III的任務調度算法研究。需要可以看下.

2016-01-13 10:34:00 4

4 面向用戶任務與云資源匹配度的調度算法研究_聶清彬

2017-01-07 18:56:13 0

0 基于改進粒子群算法的云計算任務調度算法_婁建峰

2017-01-07 19:08:43 0

0 基于改進蟻群算法的云計算任務調度研究_張海玉

2017-01-08 14:47:53 4

4 基于遺傳加差分算法的云計算任務調度

2017-01-07 21:28:58 0

0 一種面向流應用加速的可重構協處理器_曹姍

2017-01-07 22:14:03 0

0 實現準時而且無誤執行,使實時應用程序的設計和擴展變得容易,使應用程序的設計過程大為減化。 1 C/OS-II的任務調度算法分析 1.1 C/OS-II任務就緒表的解讀 C/OS操作系統采用優先級至上的任務調度原則,讓進入就緒態任務中優先級最高的那個

2017-10-30 11:18:15 2

2 云計算環境中的任務調度問題一直是云計算研究的重點,任務調度的目的尋找最優的任務調度策略,以高效地完成計算任務。針對云計算環境下資源規模龐大、異構性的特點,為了克服傳統調度算法存在的缺點,提出一種

2017-11-02 17:30:25 3

3 針對當前云任務調度算法在密碼云環境中無法實現任務實時處理的問題,提出一種基于滾動優化窗口的實時閾值調度方法。首先,將密鑰調用環節融入密碼任務流程中,提出一種密碼云服務架構;其次,為實現任務的實時調度

2017-11-24 17:08:04 5

5 合理地分配虛擬計算資源以進行有效的任務調度是云計算中的一個核心問題。為了更好地利用虛擬計算資源,高效地完成服務需求,提出了一種基于多尺度量子諧振子算法( MQHOA)的任務調度算法。首先,該算法

2017-11-30 15:17:25 0

0 任務調度是云計算中的一個關鍵問題,遺傳算法是一種能較好解決優化問題的算法。本論文針對遺傳算法在任務調度過程中隨著任務調度問題復雜度增加,算法的性能出現下降的現象,引入K-means聚類算法,提出一種

2017-12-07 15:16:10 0

0 針對云計算環境下任務調度問題,為減少任務完工時間,同時降低任務執行費用,提出一種改進的基于多目標免疫系統的任務調度算法IMISA來尋找較優的可行分配方案。與傳統分配適應度值不同,該算法將抗體群劃分

2017-12-22 14:51:37 0

0 針對現今云計算任務調度只考慮單目標和云計算應用對虛擬資源的服務的質量要求高等問題,綜合考慮了用戶最短等待時間、資源負載均衡和經濟原則,提出一種離散人工蜂群( ABC)算法的云任務調度優化策略。首先

2017-12-25 13:39:18 0

0 。將在FPGA上運行的任務視為“硬件任務”納入實時操作系統(Realtime Operating System, RTOS)的統一管理范圍,可簡化系統的設計與管理。因此,需要在傳統的RTOS中引入硬件任務管理器,實現硬件任務的管理和調度。

2018-07-11 11:20:00 1789

1789

云環境中的處理機故障已成為云計算不可忽視的問題,容錯成為設計和發展云計算系統的關鍵需求。針對一些容錯調度算法在任務調度過程中調度效率低下以及任務類型單一的問題,提出一種處理機和任務主副版本分組的容錯

2018-01-14 11:26:04 0

0 針對云計算中一些現有的基于批量調度模式和進化算法的動態云任務調度算法計算量較大,計算時間成本較高的現象,提出了一種基于改進基因表達式編程(GEP)和資源改變量的局部云任務調度算法.首先結合云任務調度

2018-01-18 13:50:44 0

0 針對物聯網異構調度環境下并行計算的靜態任務調度問題,提出了一種基于最早完成時間策略改變調度順序的表調度算法HDPTS。該算法針對現有表調度算法在調度前不能準確地確定調度順序的問題,在IHEFT算法

2018-01-29 16:50:05 0

0 任務調度響應實時性方面表現優異,但卻不適用于異構多核處理器環境。為此,提出一種高實時性任務調度算法HRSA。在Min-Min調度算法的基礎上融合LSF,EDF,HVF算法的調度策略,將任務能耗、任務完成價值和任務響應比相結合,在實現異構多核處理器任務動態

2018-02-07 11:07:43 1

1 問題,提出一種Storm環境下基于權重的任務調度算法(TSAW-Storm)。該算法首先根據各任務的CPU資源占用情況以及任務間的數據流大小,分別確定拓撲的點權和邊權;并利用最大化邊權增益的思想,逐步構建起各工作節點中承載的任務集合,在保證集群負載均

2018-04-17 10:52:18 0

0 針對高性能計算環境下的多個電子設計自動化(EDA)任務流調度問題,提出一種啟發式公平調度算法L- Fairness。在準備隊列選擇待調度任務時,L- Fairness算法結合任務滯后度、完成度

2021-03-10 15:59:30 5

5 中的重構區域劃分和任務調度決定了整個系統的性能,因此如何對DPR系統的邏輯資源劃分和調度問題進行建模,并設計高效的求解算法是保證系統性能的關鍵。在建立劃分和調度模型的基礎上,設計了基于模擬退火( SimulatedΔ nnealing,SA)的DPR系統劃分-調度聯合優化算法,用于優化重構區域的劃分方案和任務調

2021-05-13 10:39:19 5

5 針對云制造環境下的多目標任務調度問題,改進非支配排序生物地理優化算法,提出一種反映用戶偏好的任務調度算法( UPTSA)。通過基于權重均勻分配策略定義的用戶偏好度來評估制造任務調度方案的質量

2021-05-25 14:05:34 3

3 異構環境下的多DAG任務調度算法綜述

2021-06-21 15:15:16 13

13

電子發燒友App

電子發燒友App

評論