Zynq SoC架構的主要優(yōu)勢之一就是能夠通過在器件的可編程邏輯內構建外設來加快處理速度。

賽靈思 Zynq?- 7000 All Programmable SoC真正的重要優(yōu)勢之一就是能夠通過在可編程邏輯(PL)側構建外設來提高器件處理系統(tǒng)(PS)側的性能。最初您可能會認為這將是一項比較復雜的工作,但是,創(chuàng)建自己的外設其實很簡單。

如果您試圖提高PS的性能或者使用PS來控制PL側的設計行為,那么在PL內添加外設會起到很大的幫助。例如,PS可能會使用一系列存儲器映射寄存器來控制PL內的設計運行或選項。

我們選擇一種簡單模塊作為設計實例,該模塊用于打開和關閉ZedBoard上的存儲器映射LED。我們將使用賽靈思PlanAhead?、XPS和軟件開發(fā)套件(SDK)工具分三步來創(chuàng)建該模塊。

1. 在嵌入式開發(fā)套件(EDK)環(huán)境中創(chuàng)建模塊。

2. 為模塊編寫VHDL程序并構建系統(tǒng)。

3. 編寫使用最新定制模塊的軟件。

在EDK中創(chuàng)建模塊

要創(chuàng)建自己的外設,首先需要從包含Zynq SoC設計的PlanAhead項目中打開Xilinx Platform Studio (XPS) ,并選擇菜單選項中的“hardware->create or import peripheral” 。

對我們的實例模塊而言,ZedBoard上的7個LED應展示出walking display的效果,除了最重要的那個LED必須在軟件應用控制下點亮以外,其他都可以依次相繼點亮。盡管這并不是最棒的定制模塊應用,但對于流程演示而言是一種非常有用且簡單的實例。一旦掌握了這個流程,您將掌握實現(xiàn)更復雜模塊所需的全部知識。

創(chuàng)建外設時只需相繼打開10個簡單窗口并選擇所需的選項。

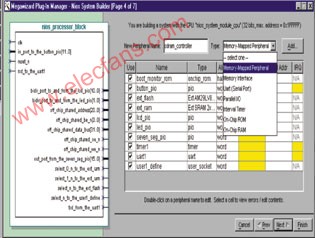

前兩個截屏(如圖1所示)詢問是否需要創(chuàng)建外設或導入現(xiàn)有的外設,如果是,需要將其關聯(lián)到哪個項目。下一步,您可在第三個截屏中對模塊進行命名并高效地定義版本和修訂版本。(注意:可利用外設流程底部的選項通過回讀*.cip文件來重新定制已創(chuàng)建的模塊。)

選定模塊名稱后,接下來要選擇所需AXI總線類型,如圖2所示。我們的實例設計需要的是一種簡單的存儲器映射控制寄存器型接口,因此我們選擇了最上面的AXI4-Lite選項。(如需了解有關不同AXI總線類型的更多信息,敬請訪問: mentation/white_papers/wp379_AXI 4_Plug_and_Play_IP.pdf )。在這個步驟中將創(chuàng)建眾多簡單寄存器。我們可利用處理系統(tǒng)通過AXI總線對寄存器進行讀/寫操作。

這些寄存器位于Zynq SoC上的可編程邏輯架構中,因此也能通過用于創(chuàng)建外設功能的用戶邏輯應用來訪問。

接下來的六個截屏為您提供相應選項,以便對AXI的主配置或從配置以及您將用于控制用戶邏輯和支持文件的寄存器的數(shù)量進行定制。本例中我們僅使用一個寄存器,并將其用作AXI-Lite的從配置。簡化系統(tǒng)開發(fā)的最重要方法是選擇外設實現(xiàn)支持標簽上的“generate template driver files”選項。這樣就能提供一系列有助于所創(chuàng)外設內部通信的源文件和頭文件。

最后一步,XPS會生成一系列有助于創(chuàng)建和使用新外設的文件:

? 以您的外設命名的頂層VHDL文件

? 可在其中創(chuàng)建用戶邏輯的VHDL文件

? 微處理器外設描述文件:用于定義連接模塊的接口,以便將模塊與XPS配合使用

? CIP文件:必要時可對外設進行重新定制

? 針對SDK的驅動程序源文件

? 針對SDK的實例源文件

? 微處理器驅動程序定義文件:詳細描述外設所需的驅動程序

這些文件將在PlanAhead源目錄(即本例中的zed_blog.srcs\ sources_1\edk\proc_subsystem)下創(chuàng)建。

源目錄的子目錄是包含XPS和PlanAhead所需文件(在與外設同名的目錄下)的Pcores目錄以及包含SDK所需文件的驅動程序目錄。

創(chuàng)建RTL

在Pcores目錄中您可以看到兩個文件,其中一個與您所創(chuàng)建的組件同名(本例中為led_if.vhd),另一個文件名為

user_logic.vhd。您可在user_logic.vhd這個文件中進行設計創(chuàng)建。同時您將會發(fā)現(xiàn)向導已經幫您生成了用于通過AXI總線在此文件中進行通信所需的寄存器和接口。此外,您可在led_if.vhd文件進行用戶邏輯模塊實例化。因此,對user_logic.vhd實體所做的任何修改都必須傳送到端口映射中。如果要求使用外部端口(例如我們的設計實例就需要外部端口來點亮LED),還必須傳送對led_if.vhd實體所做的修改。

邏輯設計創(chuàng)建完成后,您可能希望對邏輯進行仿真以確保達到預期效果。在Pcores/devl/bfmsim目錄下為您提供了總線功能模型。

在XPS中使用您的模塊

在創(chuàng)建了VHDL文件或其它文件并確保它們能正常運行后,您將期望在XPS項目中能夠應用此模塊。要正確地做到這點,需要在VHDL設計過程中確保準備添加的端口使用最新的微處理器外設描述(MPD)文件。

通過在XPS中編輯MPD文件可以順利完成這一任務。可在Project Local Pcores->USER->core name目錄下找到您所創(chuàng)建的外設。右擊文件名就可以查看MPD文件。

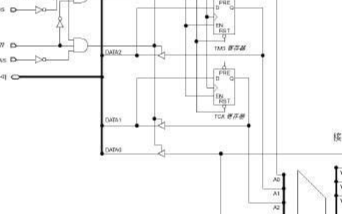

您需要添加設計中包含的非AXI接口,以便查看并在XPS中正確處理I/O。可通過以下鏈接查看MPD文件的語法: ,如圖3所示,語法非常簡單明了。圖中突出顯示的行(即中間列表底部第59行)就是用于將LED輸出端口連接到模塊的語句。

對MPD文件進行更新后必須點擊“rescan user IP repositories”,以確保將修改內容載入XPS。這時就可將器件導入系統(tǒng),就像來自IP庫中的任何其他外設一樣。一旦將其放入您希望的地址空間內(注意:最小4K)并按要求將輸出連接到外部端口,就可在必要時運行設計規(guī)則檢查程序。如果沒有任何錯誤,就可關閉XPS并返回PlanAhead。

返回PlanAhead環(huán)境后,需要重新生成頂層HDL。為此,右擊您所創(chuàng)建的處理器子系統(tǒng)并選擇“create top HDL”選項(參考《Xcell雜志》第82期,了解有關創(chuàng)建Zynq SoC PlanAhead項目方面的內容)。如果已對設計的I/O管腳進行更改,那么在實現(xiàn)之前的最后一步就是修改PlanAhead中的UCF文件。如果您對管腳滿意,就可以執(zhí)行實現(xiàn)操作,并生成隨時可在SDK中使用的比特流。

在SDK中使用外設

到這一步時,我們已經做好了在軟件環(huán)境中使用外設的準備。與創(chuàng)建和實現(xiàn)任務一樣,該流程也非常簡單直觀。第一步是使用PlanAhead中的“export hardware for SDK”選項將硬件導出至軟件開發(fā)套件。接著打開SDK,并檢查MSS文件以確定您所創(chuàng)建的外設已經存在。所列外設名稱應與旁邊的驅動程序名稱相同;

在第一個實例中,驅動程序被命名為“通用”。在SDK中使用外設時,通用驅動程序便不是問題。如果您想使用它,就需要涵蓋頭文件#include "xil_io.h."。這樣就可以調用函數(shù)Xil_in32(地址)或Xil_out32(地址),以便對外設進行讀寫操作。

采用這種方法時,需要了解外設的基地址(在xparameters.h中給出)以及寄存器間的偏移地址。在這種情況下,由于本設計實例采用32位尋址,因此寄存器的間隔為0x04。但是,如果在使用XPS創(chuàng)建外設時選擇了“驅動程序-創(chuàng)建”選項,那么將為您的外設專門構建單獨的驅動程序。且該驅動程序也將位于PlanAhead源目錄的驅動程序子目錄中。

可用這類專門構建的驅動程序來代替設計中的通用驅動程序,但首先您必須設置軟件庫指向該目錄,以便查看新生成的驅動程序。可根據“Xilinx Tools ->Repositories menu”菜單定義該軟件庫(圖4)。

一旦設定的軟件庫指向正確的目錄后,就可以對軟件庫進行重新掃描并關閉對話框。緊接著,是選擇新驅動程序以更新板支持包。右擊Project Explorer下的BSP圖標,打開板支持包設置。點擊驅動程序標簽,您將看到包含所有外設及其驅動程序的列表。從適用于該器件的驅動程序列表中選擇相應的驅動程序,就可以修改選擇的外設驅動程序(圖5)。

通過名稱為外設選擇驅動程序并點擊OK。如果您選擇了自動編譯選項,那么將會重新編譯項目。一旦代碼被重新構建,那么就要做好利用所提供的驅動程序與外設進行通信的準備。

您需要在源代碼中加入驅動程序頭文件#include "led_if.h",并采用來自xpara-meters.h的外設基地址使接口能夠明確外設在存儲空間中的位置。然后,調用“include” 文件中驅動程序所提供的命令就比較簡單了。在我們的設計中,調用示例如下

LED_IF_mWriteSlaveReg0(LED_

ADDR, LED_IF_SLV_REG0_OFF-

SET, 0x01);

寫入此命令后,就可以在硬件環(huán)境中對軟件進行測試并確認其是否按預期正常運行。

正如您所看到的,在Zynq SoC 設計中創(chuàng)建自己的外設并非您最初想象的那么復雜。外設的創(chuàng)建能為您的Zynq SoCPS乃至最終整個解決方案帶來諸多優(yōu)勢。

電子發(fā)燒友App

電子發(fā)燒友App

評論