長期以來,單片機以其性能價格比高、體積小、功能靈活、可靠性高、易于人機對話和良好的數據處理能力等方面所具有的獨特優點,被廣泛應用于各個領域。但受其內部資源的限制,在很多應用中,單片機需要在片外擴展相關資源,如程序存儲器、數據存儲器、I/O口以及中斷源等。隨著可編程邏輯器件(PLD)及EDA技術的發展,在系統設計中經常會用到FPGA/CPLD來擴展單片機的相關資源,使其有機結合,縮短開發周期,適應市場需要。FPGA/CPLD具有高速、高可靠以及開發便捷、規范等優點,在功能上與單片機有很強的互補性。以此兩類器件相結合的電路結構在許多高性能儀器儀表和電子產品中被廣泛應用。基于這種需求,筆者設計了MCS51單片機與FPGA/CPLD的總線接口邏輯電路,實現了單片機與FPGA/CPLD數據與控制信息的可靠通信,使FPGA/CPLD與單片機優勢互補,組成靈活的、軟硬件都可現場編程的控制系統。

1 單片機與FPGA/CPLD的接口方式

單片機與FPGA/CPLD的接口方式一般有兩種,即總線方式與獨立方式。

1.1 總線方式

MCS51單片機具有很強的外部總線擴展能力,利用片外三總線結構(即數據總線、地址總線、控制總線)很容易實現單片機與FPGA/CPLD的總線接口。其基本原理框圖如圖1所示。

?

圖1 總線方式原理框圖

單片機與FPGA/CPLD以總線方式通信的邏輯設計,重要的是要詳細了解單片機的總線讀寫時序,根據時序圖來設計邏輯結構,其通信的時序必須遵循單片機內固定的總線方式讀/寫時序。FPGA/CPLD的邏輯設計也相對比較復雜,在程序設計上必須與接口的單片機程序相結合,嚴格安排單片機能訪問的I/O空間。但是,單片機以總線方式與FPGA/CPLD進行數據與控制信息通信也有許多優點:

◆ 速度快。其通信工作時序是純硬件行為,對于MCS51單片機,只需一條單字節指令就能完成所需的讀/寫時序,如“MOV @DPTR,A”和“MOV A,@DPTR”。

◆ 節省PLD芯片的I/O口線。僅通過19根I/O口線,就能在FPGA/CPLD與單片機之間進行各種類型的數據與控制信息交換。

◆ 相對于非總線方式,單片機編程簡捷,控制可靠。

◆ 在CPLD/FPGA中通過邏輯切換,單片機易于與SRAM或ROM接口。這種方式有許多實用之處,如利用類似于微處理器系統的DMA的工作方式,首先由FPGA/CPLD與接口的高速器件進行高速數據采樣,并將數據暫存于SRAM中采樣結束后,通過切換,使單片機與SRAM以總線方式進行數據通信,以便發揮單片機強大的數據處理能力。

1.2 獨立方式

與總線接口方式不同,幾乎所有單片機都能以獨立接口方式與FPGA/CPLD進行通信,其通信的時序方式可由所設計的軟件自由決定,形式靈活多樣。其最大的優點是FPGA/CPLD中的接口邏輯無需遵循單片機內固定總線方式的讀/寫時序。FPGA/CPLD的邏輯設計與接口的單片機程序設計可以分先后相對獨立地完成。事實上,目前許多流行的單片機已無總線工作方式,采用獨立方式可以很好地使它們與FPGA/CPLD結合。獨立方式的接口設計方法比較簡單,其基本原理框圖如圖2所示。直接將單片機的I/O端口線與FPGA/CPLD的I/O相連即可。

圖2 獨立方式原理框圖

2 總線接口邏輯設計

由于單片機以總線方式與FPGA/CPLD進行數據與控制信息通信有許多優點,因此在設計中,單片機與FPGA/CPLD接口采用總線方式。

2.1 接口設計思想

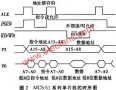

對MCS51單片機與FPGA/CPLD以總線方式通信的邏輯接口設計,應該詳細了解MCS51單片機的總線讀/寫時序,并根據時序圖來設計邏輯結構。MCS51單片機總線讀/寫的時序如圖3所示,其時序電平變化速度與單片機工作時鐘頻率有關。

?

圖3 MCS51單片機總線讀/寫時序

CLK為單片機時鐘信號,ALE為地址鎖存使能信號。在讀/寫周期開始后,CPU把低8位地址送到P0口總線上,把高8位地址送到P2口總線上,利用ALE下降沿可將低8位地址鎖存于地址鎖存器中,而高8位地址信息一直鎖存在P2口鎖存器中;同時單片機利用讀指令允許信號PSEN的低電平從ROM中將指令從P0口讀入,其指令讀入的時機是在PSEN的上升沿之前。接下來,由P2口和P0口分別輸出高8位和低8位數據地址,并由ALE的下降沿將P0口的低8位地址鎖存于地址鎖存器。然后根據讀/寫信號的狀態讀寫外部數據,把數據送到P0口總線上;數據讀/寫的時機是在讀/寫信號的上升沿之前,將數據讀入單片機或寫入被尋址的地址單元。當讀/寫信號變為無效電平后,P0口總線變為懸浮狀態,為下次總線讀/寫做好準備。

通過對MCS51單片機總線讀/寫時序的分析,可以在FPGA/CPLD中設計一個總線接口模塊,實現單片機三總線信號的編碼。由于在總線應用時,MCS51單片機的P0口是作為地址/數據總線分時復用的,因此應在總線接口模塊中設計一個三態緩沖器,實現P0口的三態接口;又因為MCS51單片機在訪問外部空間時,它的地址為16位,因此借助地址鎖存使能信號ALE在FPGA/CPLD中實現高8位與低8位地址的編碼,組合成16位地址,然后再根據MCS51單片機的讀/寫信號,實現對FPGA/CPLD的讀寫操作。

2.2 總線接口設計

通過對MCS51單片機總線讀/寫時序的分析,設計了圖4所示的接口電路。在FPGA/CPLD中,設計了兩個模塊:一個是總線接口模塊,負責單片機與FPGA/CPLD的總線接口邏輯;另一個是寄存器單元及外部接口模塊,運用總線接口模塊來操作此模塊。

?

圖4 MCS51單片機與FPGA/CPLD總線接口框圖

圖中整個總線接口邏輯模塊將MCS51單片機的三總線信號編碼成5個信號輸出:16位地址信號addr16、讀使能信號RD_EN、寫使能信號WR_EN、數據輸出信號Din及數據輸入信號Dout。

在總線接口模塊中,又分為3個小模塊:三態緩沖模塊、鎖存器模塊及編碼模塊。三態緩沖模塊實現與單片機P0口接口;鎖存器模塊利用ALE信號鎖存單片機輸出的低8位地址。利用其下降沿將低8位地址鎖存于FPGA/CPLD中的地址鎖存器(address latch)中;當ALE將低8位地址通過P0及三態緩沖器鎖存的同時,高8位地址已穩定建立于P2口;通過編碼模塊將高8位與低8位地址組合成16位地址addr16。同時根據單片機的讀/寫控制信號編碼成RD_EN與WR_EN使能信號。

若需從FPGA/CPLD中讀出數據,單片機則通過指令“MOVXA,@DPTR”使RD信號為低電平,使能RD_EN信號,由P0口將圖中地址addr16所指單元的數據讀入累加器A;但若將累加器A的數據寫進FPGA/CPLD中,單片機則需通過指令“MOVX @DPTR,A”和寫允許信號WR。這時,DPTR中的高8位和低8位數據作為高、低8位地址分別向P2和P0口輸出,然后經ALE信號下降沿鎖存,產生16位地址addr16。再由WR的低電平使能WR_EN信號,將累加器A的數據經P0口及三態緩沖器寫入圖中16位地址addr16所對應的單元中。實現單片機對FPGA/CPLD的讀/寫操作。

2.3 接口VHDL實現及仿真

在總線接口設計中,采用VHDL語言實現其接口邏輯。用VHDL編寫接口程序,往往會很方便,但在編寫時卻要注意讀完數據時,要把數據總線釋放掉以免造成總線沖突。其源程序如下:

-FPGA/CPLD內部寄存器地址定義

libraryIEEE;

useIEEE.STD_LOGIC_1164.all;

PACKAGEInterfaceIS

CONSTANT ADDR_REG1 :STD_LOGIC_VECTOR(15 DOWNTO 0):=X"FFF1";

CONSTANT ADDR_REG2 :STD_LOGIC_VECTOR(15 DOWNTO 0):=X"FFF2";

CONSTANT ADDR_REG3 :STD_LOGIC_VECTOR(15 DOWNTO 0):=X"FFF3";

CONSTANT ADDR_REG4 :STD_LOGIC_VECTOR(15 DOWNTO 0):=X"FFF4";

ENDInterface;

-FPGA/CPLD讀/寫操作

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_arith.all;

use IEEE.std_logic_unsigned.all;

use work.Interface.all;

entity MCS51_FPGA is

port (

P0 : inout STD_LOGIC_VECTOR (7 downto 0);

P2 : inSTD_LOGIC_VECTOR (7 downto 0);

ALE: inSTD_LOGIC;

WR : inSTD_LOGIC;

RD : inSTD_LOGIC;

LED: outSTD_LOGIC_VECTOR (2 downto 0)

);

end MCS51_FPGA;

ArchitectureC51_FPGA_BUS OF MCS51_FPGA IS

-16位地址

signalC51_Addr16 : STD_LOGIC_VECTOR(15 downto 0);

-內部寄存器

signal Data: STD_LOGIC_VECTOR (31 downto 0);

-WR/RD 使能

signalWR_EN:STD_LOGIC;

signalRD_EN:STD_LOGIC;

Begin

-地址鎖存

Address_p:process(ALE)

begin

if ALE′event and ALE='0' and ALE'LAST_VALUE='1' then

C51_Addr16<=P2&P0;

end if;

end process;

-WR/RD 使能

WR_EN<= (WR AND RD) OR WR;

RD_EN<= (WR AND RD) ORRD;

-讀FPGA內部寄存器

P0 <=

Data(7 downto 0)when C51_Addr16=ADDR_REG1 and RD_EN ='0'ELSE

Data(15 downto 8) when C51_Addr16=ADDR_REG2 and RD_EN ='0'ELSE

Data(23 downto 16)when C51_Addr16=ADDR_REG3 and RD_EN ='0'ELSE

Data(31 downto 24)when C51_Addr16=ADDR_REG4 and RD_EN ='0'ELSE

"ZZZZZZZZ"; 在未讀時釋放總線,實現總線的三態

-寫FPGA內部寄存器

C51_Write_FPGA:process(WR_EN)

begin

IF WR'EVENT and WR'LAST_VALUE='1' and WR_EN ='0' THEN

CASE C51_Addr16 IS

when ADDR_REG1=>Data(7 downto 0)<=P0;

when ADDR_REG2=>Data(15 downto 8)<=P0;

when ADDR_REG3=>Data(23 downto 16)<=P0;

when ADDR_REG4=>Data(31 downto 24)<=P0;

when OTHERS=>NULL;

END CASE;

END IF;

END process;

-LED控制

LED<=Data(2 downto 0);

END C51_FPGA_BUS;

總線接口讀/寫仿真如圖5所示,(a)為總線接口寫仿真,(b)為總線接口讀仿真。

?

圖5 總線接口讀/寫仿真圖

結語

本文實現單片機與FPGA/CPLD的總線接口邏輯設計,是設計的高速采樣設備的一部分。經仿真驗證以及實際應用,證明該接口原理應用完全正確、可行。在筆者設計的多個系統中,也已經成功地進行了應用。該電路由于接口簡單容易控制,因此,在涉及FPGA與單片機系統的接口電路中,可以靈活地應用。

電子發燒友App

電子發燒友App

評論