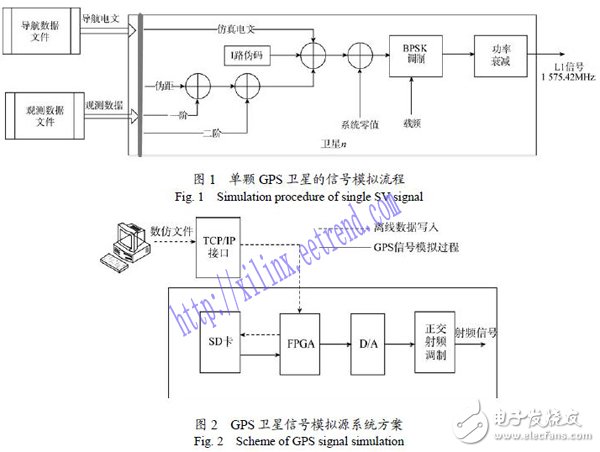

真實(shí)的多顆 GPS 衛(wèi)星信號(hào)在空間合成, 而模擬的GPS 衛(wèi)星信號(hào)在數(shù)字域?qū)崿F(xiàn)疊加合成。采用地址發(fā)生器產(chǎn)生12 顆衛(wèi)星的特征碼, 分別與對(duì)應(yīng)的導(dǎo)航電文進(jìn)行疊加, 合成的基帶信號(hào)通過(guò)正交射頻調(diào)制,調(diào)制為L(zhǎng)1 頻點(diǎn)1.575 GHz 的射頻信號(hào)。

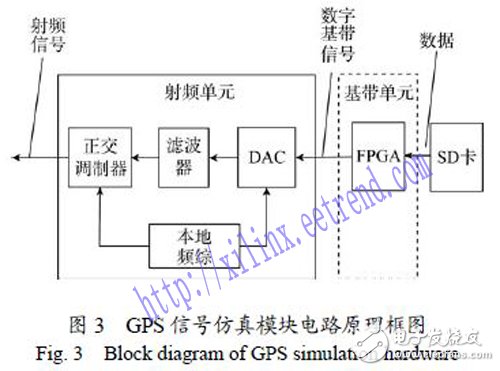

而 GPS 衛(wèi)星信號(hào)模擬源采用圖2 所示方案。采用SD 卡存儲(chǔ)導(dǎo)航電文和觀測(cè)數(shù)據(jù)文件。在系統(tǒng)工作時(shí), FPGA 讀取SD 卡的數(shù)據(jù), 按圖1 所示的流程產(chǎn)生衛(wèi)星的基帶信號(hào), 多顆星的基帶信號(hào)經(jīng)數(shù)字合成后,送至DA 變?yōu)槟M信號(hào), 再進(jìn)行正交射頻調(diào)制獲得L1 頻點(diǎn)的射頻信號(hào)。

?

?

當(dāng)系統(tǒng)需要更新數(shù)仿文件時(shí), 則通過(guò)TCP/IP 接口對(duì)SD 卡進(jìn)行讀寫(xiě)操作, 實(shí)現(xiàn)SD 卡中的文件更新。

數(shù)據(jù)文件格式

GPS 信號(hào)模擬的目的是使GPS 接收機(jī)通過(guò)接收模擬的信號(hào)正常工作, 實(shí)現(xiàn)定位解算。而GPS 信號(hào)是由多顆不斷運(yùn)行的GPS 衛(wèi)星實(shí)時(shí)發(fā)射產(chǎn)生的。為了實(shí)現(xiàn)GPS 信號(hào)模擬, 首先需要設(shè)定用戶軌跡、建立GPS 衛(wèi)星軌道模型和信號(hào)傳輸模型, 運(yùn)算量較大。因此采用離線運(yùn)算的方法, 先在高性能計(jì)算機(jī)上進(jìn)行仿真計(jì)算, 再將計(jì)算得到文件保存下來(lái)。GPS 模擬器通過(guò)讀取該文件, 實(shí)現(xiàn)GPS 信號(hào)的仿真。這種方法的好處在于為模擬器節(jié)省了大量的資源, 有利于降低成本和體積。

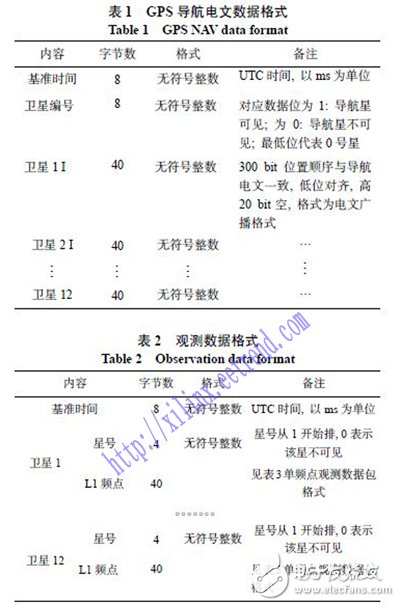

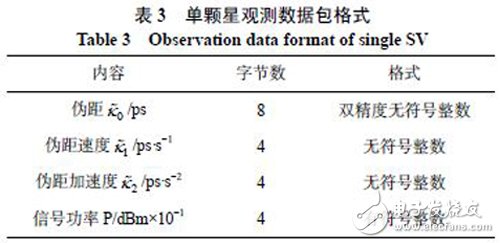

為了讓接收機(jī)實(shí)現(xiàn)定位, 必須要提供4 顆以上的GPS 衛(wèi)星信號(hào); 仿真了12 顆GPS 衛(wèi)星的數(shù)據(jù), 仿真數(shù)據(jù)主要包括導(dǎo)航電文和觀測(cè)數(shù)據(jù)。導(dǎo)航電文格式為300 bit, 占40 字節(jié), 剩余20 bit 空; 觀測(cè)數(shù)據(jù)則根據(jù)設(shè)定的位置和衛(wèi)星星歷產(chǎn)生, 模擬固定位置接收機(jī)產(chǎn)生的偽距變換, 20 ms 更新一次, 為了實(shí)現(xiàn)偽距的連續(xù)變化, 觀測(cè)數(shù)據(jù)中還包含偽距速度和加速度, 便于信號(hào)產(chǎn)生過(guò)程中的插值。

GPS 導(dǎo)航電文速率為50 bps, 300 bit 為一子幀, 一子幀為6 s。一幀包含5 子幀, 共1 500 bit, 歷時(shí)30 s。一超幀則包含25 幀, 37.5 k, 歷時(shí)12.5 min。由于GPS 電文每?jī)尚r(shí)更新一次, 則2 h 需存儲(chǔ)的導(dǎo)航電文約為 375 k; 12 顆星的導(dǎo)航電文為4.5 M。

觀測(cè)數(shù)據(jù)則為20 ms 更新一次, 單顆星的觀測(cè)數(shù)據(jù)為40 個(gè)字節(jié), 一個(gè)觀測(cè)數(shù)據(jù)包有12 顆星, 共4 288 bit; 則2 h 的數(shù)據(jù)量為4 288×50×7 200=1 543680 000 bit, 約1.5 G。因此, 采用2 G 的SD 卡可完成上述數(shù)據(jù)容量的要求。

硬件設(shè)計(jì)

GPS 信號(hào)模擬源的設(shè)計(jì)采用高速基帶數(shù)字合成技術(shù)和正交中頻、射頻調(diào)制技術(shù)。多顆衛(wèi)星信號(hào)以數(shù)字形式在高性能軟件無(wú)線電處理平臺(tái)上計(jì)算并合成, 有效提高系統(tǒng)通道間的一致性, 消除了衛(wèi)星通道間的誤差, 也消除了內(nèi)部時(shí)間誤差, 確保了高精度。該方案與射頻合成方案相比增加了軟件無(wú)線電數(shù)字部分設(shè)計(jì)的難度, 使得偽距控制精度、多普勒變化和幅度等均在數(shù)字部分計(jì)算, 簡(jiǎn)化了射頻設(shè)計(jì),避免了由射頻群時(shí)延不一致產(chǎn)生的通道間誤差和衛(wèi)星間的鐘差, 且數(shù)值計(jì)算、鐘差可控, 有效保證了系統(tǒng)的設(shè)計(jì)指標(biāo)。信號(hào)模擬源方案原理如圖4 所示。GPS信號(hào)模擬源采用基帶加射頻的單元模塊化結(jié)構(gòu)設(shè)計(jì)。

?

?

GPS 信號(hào)模擬算法對(duì)數(shù)據(jù)處理率有較高的要求,然而通過(guò)分析延時(shí)算法, 這樣龐大的計(jì)算量實(shí)際上只是簡(jiǎn)單的乘累加(MAC) 的流水操作, 其算法結(jié)構(gòu)中并無(wú)復(fù)雜的數(shù)學(xué)運(yùn)算(如正余弦、指數(shù)、對(duì)數(shù)等) ,可以說(shuō)其運(yùn)算結(jié)構(gòu)是相對(duì)比較簡(jiǎn)單的, 所以考慮采用FPGA 芯片。而目前FPGA 的功能也日益增強(qiáng), 內(nèi)嵌于FPGA 的硬核與基本邏輯構(gòu)建的軟核也不斷增強(qiáng)了FPGA 作為通用信號(hào)處理芯片的能力。通過(guò)綜合考慮, 最終選擇了用XILINX 公司的XC4VSX35作為主處理芯片。該芯片是XILINX 公司2005 推出的一款專門為數(shù)字信號(hào)處理而設(shè)計(jì)的高端FPGA, 其可編程數(shù)字信號(hào)處理模塊XtremeDSP48 在?12 的速度等級(jí)上最高性能為500 MHz。

基帶單元設(shè)計(jì)采用1 片Xilinx 高性能FPGAXC4VSX35 來(lái)完成。XC4VSX35 主要完成以下任務(wù):1) 從SD 卡讀入導(dǎo)航電文和觀測(cè)數(shù)據(jù); 2) 多星數(shù)據(jù)的分配; 3) 多星信號(hào)的精密延遲和動(dòng)態(tài)特性控制;4) 多星信號(hào)的數(shù)字合成。設(shè)計(jì)上可完成12 顆星I 路的導(dǎo)航信號(hào)產(chǎn)生。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論