數(shù)字濾波是頻譜、語音和圖像處理等應(yīng)用中的一個基本技術(shù),與模擬濾波相比,數(shù)字濾波具有很多突出的優(yōu)點。數(shù)字濾波在性能上可以滿足幅度和相位的嚴格要求,可以避免電壓漂移、溫度漂移和噪聲問題; 在實現(xiàn)上具有穩(wěn)定性好,精度高、抗干擾能力強等優(yōu)點[1]。

當今的數(shù)字信號濾波,多采用微處理器ASIC( Application Specific Integrated Circuit) 芯片實現(xiàn)[2]。近年來隨著大規(guī)模集成電路技術(shù)的飛速發(fā)展,DSP( Digital Signal Processor) 技術(shù)與微處理器技術(shù)緊密結(jié)合,可以極大地提高系統(tǒng)的運算速度與精度,使得新一代的具有DSP內(nèi)核的微處理器成為高檔智能化儀器與設(shè)備的核心元件。但是高性能的專業(yè)DSP 芯片的價格也是昂貴的,在系統(tǒng)開發(fā)時必須要考慮到系統(tǒng)的整體成本價格,選擇合適的設(shè)計方案。DSP 的ASIC 濾波芯片往往應(yīng)用于專門的領(lǐng)域,如直流電壓的高分辨率測量、溫度、壓力和質(zhì)量信號的測量等。如何采用靈活的設(shè)計方式,低成本地實現(xiàn)數(shù)字濾波成為一項挑戰(zhàn)[3]。

地震數(shù)據(jù)采集系統(tǒng)為地質(zhì)勘探服務(wù)的儀器,將地面上的震動信號轉(zhuǎn)換為數(shù)字形式記錄下來,通過對采集的數(shù)據(jù)進行反演,得到地層的結(jié)構(gòu)。本文針對地震數(shù)據(jù)采集系統(tǒng)的數(shù)字濾波設(shè)計提出并實現(xiàn)了一種FPGA( Field Programmable Gate Array) 與MCU( Micro Control Unit)相結(jié)合的設(shè)計方案,兼顧開發(fā)成本和靈活性。方案的思想不僅適用于地震數(shù)據(jù)采集系統(tǒng),也適用于電壓、壓力、音頻等各種傳感器網(wǎng)絡(luò)。

1 數(shù)字濾波系統(tǒng)結(jié)構(gòu)

在現(xiàn)代地震數(shù)據(jù)采集的設(shè)計中,為了能獲得高分辨率的振動信號,不僅數(shù)據(jù)精度要求達到24 位,系統(tǒng)測試時信噪比通常要好于110dB[4]。地震數(shù)據(jù)采集的另一個特點是有效性能量都處于低頻部分[5],通常在幾百赫茲以下,因此最終只需要1 kHz /s 的數(shù)據(jù)采樣率[6]。

Sigma - Delta 轉(zhuǎn)換器以遠遠高于奈奎斯特采樣率對模擬信號進行過采樣,非常適用于最低頻率低于數(shù)千赫茲的緩慢變化信號的高精度A/D 轉(zhuǎn)換。目前在地震數(shù)據(jù)采集中廣泛應(yīng)用的Sigma - Delta A/D 轉(zhuǎn)換器主要有Cirrus Logic公司的CS5371 /5372 高精度24 位A/D 轉(zhuǎn)換器[7]。

根據(jù)地震數(shù)據(jù)采集Sigma - Delta 高度過采樣的特點,需要在后端設(shè)計一個數(shù)字抽取濾波器,對信號進行抽取和調(diào)理。需要實現(xiàn)的功能有三個: 一是使調(diào)制器輸出的高速的信號頻率降到奈奎斯特頻率; 二是濾除調(diào)制器輸出的高頻噪聲; 三是將調(diào)制器輸出的一位數(shù)字信號轉(zhuǎn)換為高精度的多位數(shù)字輸出信號[8]。

在將數(shù)字濾波器運用于Sigma - Delta A/D轉(zhuǎn)換器中時,理論上既能采用FIR( Finite ImpulseResponse) 數(shù)字濾波器,也能采用IIR( Infinite Impulse Response) 數(shù)字濾波器來實現(xiàn)。IIR濾波器具有無限長的沖激響應(yīng),但是IIR 數(shù)字濾波器的相位特性不好控制,對相位要求較高時,需加相位校準網(wǎng)絡(luò),因此IIR 數(shù)字濾波器是不適合的。FIR 濾波器沒有反饋回路,故不存在不穩(wěn)定的問題,同時可以做到嚴格的線性相位。由于Sigma - Delta A/D 轉(zhuǎn)換器是一種高精度、高保真的A/D 轉(zhuǎn)換器,因此除了要保證信號幅度的精度外,還必須保證信號各頻率分量的相對相位不變,否則會產(chǎn)生相位失真[9]。

Sigma - Delta A/D 轉(zhuǎn)換器的高度過采樣要求數(shù)字抽取濾波器具有很高的抽取率,濾波器采用多級抽取的結(jié)構(gòu)可以獲得更高的效率。多級的抽取結(jié)構(gòu)和單級的結(jié)構(gòu)相比,計算量和存儲量要求更低,每一級的歸一化帶寬較寬,可以減少有限字長效應(yīng)[8]。此外,由于抽取方式應(yīng)用時降低了數(shù)據(jù)率,所以后續(xù)工作的FIR 濾波器需要的時鐘速率也跟著降低了,能最大限度地節(jié)約高速硬件系統(tǒng)中的功耗。

直接式FIR 濾波器的結(jié)構(gòu)需要很多乘法器和加法器,這樣的結(jié)構(gòu)需要較多的面積和成本,所以要想辦法減少乘法器和加法器的使用。CIC 濾波器( Cascaded Integrator - Comb Filter)是一種高效計算實現(xiàn)窄帶低通的濾波器,它的頻率響應(yīng)曲線跟SINC 函數(shù)sin( x) /x 相似,通常被應(yīng)用在現(xiàn)代通信系統(tǒng),實現(xiàn)硬件抽取和內(nèi)插。CIC 濾波器在硬件設(shè)計中受歡迎的一個重要的特點是它們不需要乘法,只需要加法和減法,可以降低計算復(fù)雜性,便于系統(tǒng)實現(xiàn)[10]。

在CIC 濾波器抽取/插值的應(yīng)用中,常常希望得到一個平的通帶和一個窄的過渡帶,但是這跟CIC 濾波器本身的特性是不符合的,為了解決這一問題,CIC 濾波器的前端或者后端通常有一個高性能線性相位低通FIR 濾波器,這些FIR 濾波器的任務(wù)是補償CIC 濾波器的非平坦的傳輸頻帶。

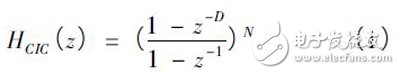

圖1( a) 所示是一個經(jīng)典的一階CIC 濾波器,由延遲單元和加減單元構(gòu)成。對于一個N階,時延為D 的CIC 濾波器,其z 域傳輸函數(shù)為:

?

CIC 濾波器有抽取濾波的形式,抽取操作意味著每隔R 個樣點只取一個樣點輸出,從而導(dǎo)致輸入采樣率是輸出采樣率的R 倍。梳狀濾波器的位置放在抽取之后可以節(jié)約計算時需要的寄存器空間。大部分的CIC 濾波器都是采用如圖1( b) 所示的結(jié)構(gòu),此時梳狀濾波器的延遲為N = D/R,而不是D。

?

CIC 濾波器的主要特點是延遲累加,所以只要用加法器、減法器和寄存器就能實現(xiàn),無需乘法器,因此用FPGA 實現(xiàn)起來比軟件算法實現(xiàn)要簡單,而且由于FPGA 是并行結(jié)構(gòu),所以處理的速度也比軟件處理快,故選用FPGA 來實現(xiàn)CIC 濾波。

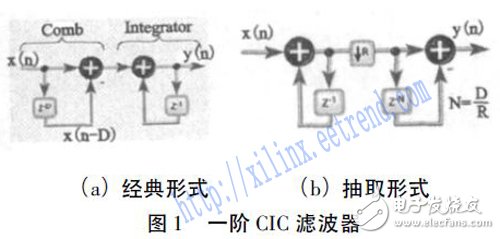

FIR 濾波器算法是對具有一組相關(guān)系數(shù)的輸入信號進行離散卷積。一個M 階FIR 濾波器的變換函數(shù)為:

?

由變換函數(shù)的表達式可看出,變換函數(shù)實際上需要用乘法器、延時元件及加法器來實現(xiàn)。FIR 也可以使用FPGA 來實現(xiàn)。用FPGA 實現(xiàn)FIR 的優(yōu)點與實現(xiàn)CIC 一樣,處理速度快,但是由于FIR 實現(xiàn)需要用到乘法器,所以實現(xiàn)起來比CIC 復(fù)雜,也需要更多的資源,這樣對成本控制是不利的。并且在地震數(shù)據(jù)濾波中,數(shù)據(jù)速率很低,并不需要高速的FIR 濾波,所以在這里,把FIR 濾波部分由MCU 來完成,在節(jié)省硬件資源的同時降低了成本。

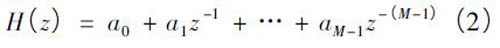

濾波系統(tǒng)的整體框圖如圖2 所示,由FPGA模塊、MCU 模塊兩部分組成。其中CIC 濾波模塊在FPGA 內(nèi)實現(xiàn),而FIR 濾波在MCU 內(nèi)實現(xiàn)。

?

濾波系統(tǒng)的輸入信號為正弦信號經(jīng)過Sigma-Delta ADC 轉(zhuǎn)換后形成的1 bit 數(shù)據(jù)流,數(shù)據(jù)率為512 kHz。經(jīng)過CIC 抽取濾波器和FIR濾波器抽取濾波之后,得到24 位1 kHz 數(shù)據(jù)率的輸出數(shù)據(jù)。

2 SINC 濾波器設(shè)計

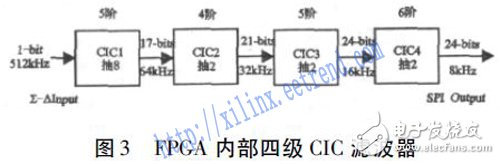

地震數(shù)據(jù)采集的采樣率除了最常用的1 k采樣率,還有2 k,4 k 采樣率等,為了支持多種采樣率,CIC 整體模塊由4 個單級的CIC 模塊級聯(lián)形成。在其他采樣率時,可以旁路其中部分濾波器。

如圖3 所示,這四個單級CIC 濾波器分別是一個5 階的8 抽樣CIC 濾波器( CIC 1) 、一個4 階的2 抽樣濾波器( CIC 2) 、一個5 階的2 抽樣濾波器( CIC 3) 和一個6 階的2 抽樣濾波器( CIC 4) 。Sigma - Delta A/D 轉(zhuǎn)換器輸入數(shù)據(jù)率和位寬分別是512k、1 bit,經(jīng)過CIC 1 后,位寬17 bit、數(shù)據(jù)率64 kHz; 經(jīng)過CIC 2 后,位寬21bit、數(shù)據(jù)率32 kHz; 經(jīng)過CIC 3 后,位寬24 bit、數(shù)據(jù)率16 kHz; 經(jīng)過CIC 4 后,位寬24 bit、數(shù)據(jù)率8 kHz。

?

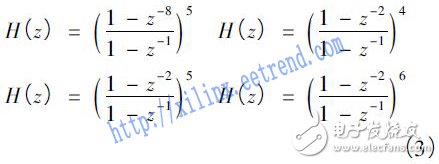

四級CIC 濾波器變換函數(shù)H( z) 分別為:

后三級CIC 濾波器的傳輸函數(shù)形式上是一樣的,分成三級設(shè)計是為了將時鐘頻率逐級降低下來,盡可能地減少工作在高速時鐘的邏輯,達到降低功耗的目的。

因為CIC 濾波器所占用的邏輯面積很小,選擇Xilinx 公司的FPGA 芯片XC3S100E 來實現(xiàn)。它是Spartan3E 系列中邏輯門數(shù)最少的芯片,已經(jīng)足夠?qū)崿F(xiàn)CIC 功能和其它很多控制邏輯[11]。Sigma - Delta A/D 轉(zhuǎn)換器輸入數(shù)據(jù)在FPGA 內(nèi)部經(jīng)過四級CIC 濾波后產(chǎn)生8 kHz、24bit 數(shù)據(jù)。FPGA 通過SPI 接口將數(shù)據(jù)發(fā)送到MCU。

3 FIR 濾波器設(shè)計

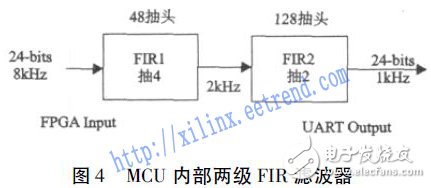

FIR 濾波器采用兩級FIR 串聯(lián)的形式達到濾波效果。由于CIC 濾波器在低頻部分有著衰減的帶寬,需要通過一個FIR 濾波器改善整個濾波系統(tǒng)低頻部分的性能。其后另接一個FIR濾波器,產(chǎn)生一個快速下降的帶寬,以對高頻部分濾除。

FIR 濾波結(jié)構(gòu)特點是沒有反饋支路,即沒有環(huán)路,其單位脈沖響應(yīng)是有限長度。FIR 的特征函數(shù)將輸入X( n) 和h( k) 做卷積運算,得到輸出Y( n) 的差分方程為:

如圖4 所示,F(xiàn)IR1 抽取濾波器為48 抽頭( 47 階) 4 抽取濾波器。FIR2 抽取濾波器為126 抽頭( 127 階) 2 抽取濾波器,Matlab 可以根據(jù)需要達到的濾波效果產(chǎn)生具體的濾波系數(shù)。

?

對于FIR 濾波器,從卷積公式可知,有K個系數(shù)的FIR 濾波對每個輸入需要做K + 1 次乘法,在抽取時,這個運算可以被簡化,不是每個輸入都要跟每個系數(shù)相乘,可以只算有效的乘積,忽視會被抽取掉的選項,可以節(jié)約MCU資源,大大提高效率[12]。

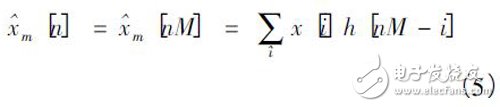

抽取為M 時,則M 個數(shù)里有一個才是有效項,即式( 5) 所示:

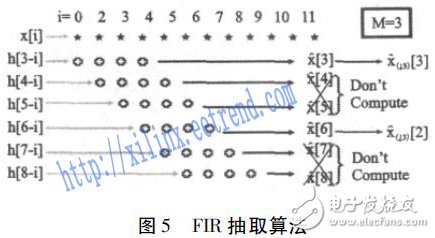

以一個階數(shù)M 為3,抽樣為3 的FIR 濾波器為例,它含有4 個系數(shù),它的有效乘積項可以用圖5 直觀表示。

對一個有K 個系數(shù),抽樣為M 的FIR 來說,一般的算法除了開頭的K - 1 個輸入,以后每個輸入都需要做K 次乘法運算; 優(yōu)化后的算法每個輸入只需要做[K /M]次乘法,其中[K /M]為系數(shù)個數(shù)除以抽樣數(shù)后向上取整。

FIR 濾波部分由三部分組成: SPI 接口,F(xiàn)IR濾波器和串口。SPI 是MCU 跟FPGA 通訊的通道,MCU 從SPI 得到數(shù)據(jù); FIR 濾波器為FIR 濾波功能實現(xiàn)模塊; 串口為MCU 跟主機通訊的通道,主機可以通過串口給MCU 發(fā)指令,MCU 可以將處理完的數(shù)據(jù)用串口發(fā)給計算機。比如NXP 公司的LPC2106 芯片是一款ARM7 核的MCU,功耗低,數(shù)十兆赫茲的處理能力已經(jīng)能夠勝任32 kHz 的數(shù)據(jù)處理[13]。

4 系統(tǒng)仿真和實際測試

Matlab 可以對系統(tǒng)的性能做出理論上的分析。CIC 濾波器的幅頻響應(yīng)如圖6 所示,可以看出CIC 在低頻部分有著良好的響應(yīng),但是在高頻部分下降得不夠快。CIC 濾波器和FIR 濾波器的整體幅頻響應(yīng)如圖7 所示,CIC 和FIR兩級濾波器在430 Hz 以下有著良好的低通性能; 而在430 Hz ~ 500 Hz 的頻率范圍內(nèi),幅度響應(yīng)下降了137 dB。

通過Matlab 仿真,可以從理論上得到CIC和FIR 構(gòu)成的數(shù)字濾波器的性能。在實際中,可以通過真實的信號進行進一步的測試。在系統(tǒng)測試時,需要提供一個正弦波經(jīng)過AD采樣后的數(shù)據(jù),這個電路可以通過CS4373和AD轉(zhuǎn)換器CS5372 組成。CS4373 的主要功能是提供一個正弦信號,而CS5372 是高精度Sigma-Delta AD 轉(zhuǎn)換器,能產(chǎn)生符合測試條件的串行bit 數(shù)據(jù)流,數(shù)據(jù)率為512 kb /s。

圖8 是測試數(shù)據(jù)的頻域波形,通過計算可以得到信噪好于110 dB,能夠滿足地震數(shù)據(jù)采集的需求。

?

5 結(jié)論

本文針對地震數(shù)據(jù)采集系統(tǒng)中Sigma-Delta A/D 轉(zhuǎn)換器后端的多級抽取濾波器進行了設(shè)計和實現(xiàn)。濾波器由四級CIC 濾波器和兩級FIR濾波器構(gòu)成,分別在FPGA 和MCU內(nèi)實現(xiàn)。相對于專用的濾波芯片設(shè)計,極大地降低了成本。濾波器有著良好的低通性能,并能有效壓制噪聲,實測信噪比好于110 dB,能夠很好地滿足地震數(shù)據(jù)采集的需求。

這種FPGA 和MCU 相結(jié)合的方式所實現(xiàn)的地震信號濾波器,是一種低成本地震信號數(shù)字濾波器設(shè)計的嘗試。從原理上驗證了此類濾波器實現(xiàn)的可能性,并從性能上給出了初步的評估結(jié)果。但是這種方案的應(yīng)用具有一定的局限性,它的功耗同商業(yè)濾波器相比相對較高。下一步可以在此方案的基礎(chǔ)上進行實現(xiàn)方面的研究,從而達到性能、功耗和價格方面的多點平衡。

電子發(fā)燒友App

電子發(fā)燒友App

評論