?

SPI4.2總線(System Packet Interface,系統間數據包接口)是一種速度高達10 Gb/s的芯片間互連總線,主要應用于ATM信元傳輸、POS(Packet Over SONET/SDH,基于SONET/SDH的包傳輸)和10 Gb/s以太網等高端場合。特別在通信領域,很多高端處理器和網絡處理器,如Intel公司的IXP2800、Cavium公司的多內核處理器CN58xx系列、NetLogic公司的XLR732、Broadcom的BCM1480,幾乎都集成了SPI4.2接口,以提高芯片的吞吐能力,適應通信產業朝著LTE(長期演進)發展的需求。還有眾多的物理層芯片,例如Cortina公司的CS1331,可以將SPI4.2總線轉換成8個千兆以太網接口。SPI4.2總線之所以被眾多的高端芯片所采用,與其高速、靈活、可靠的特性是密不可分的。

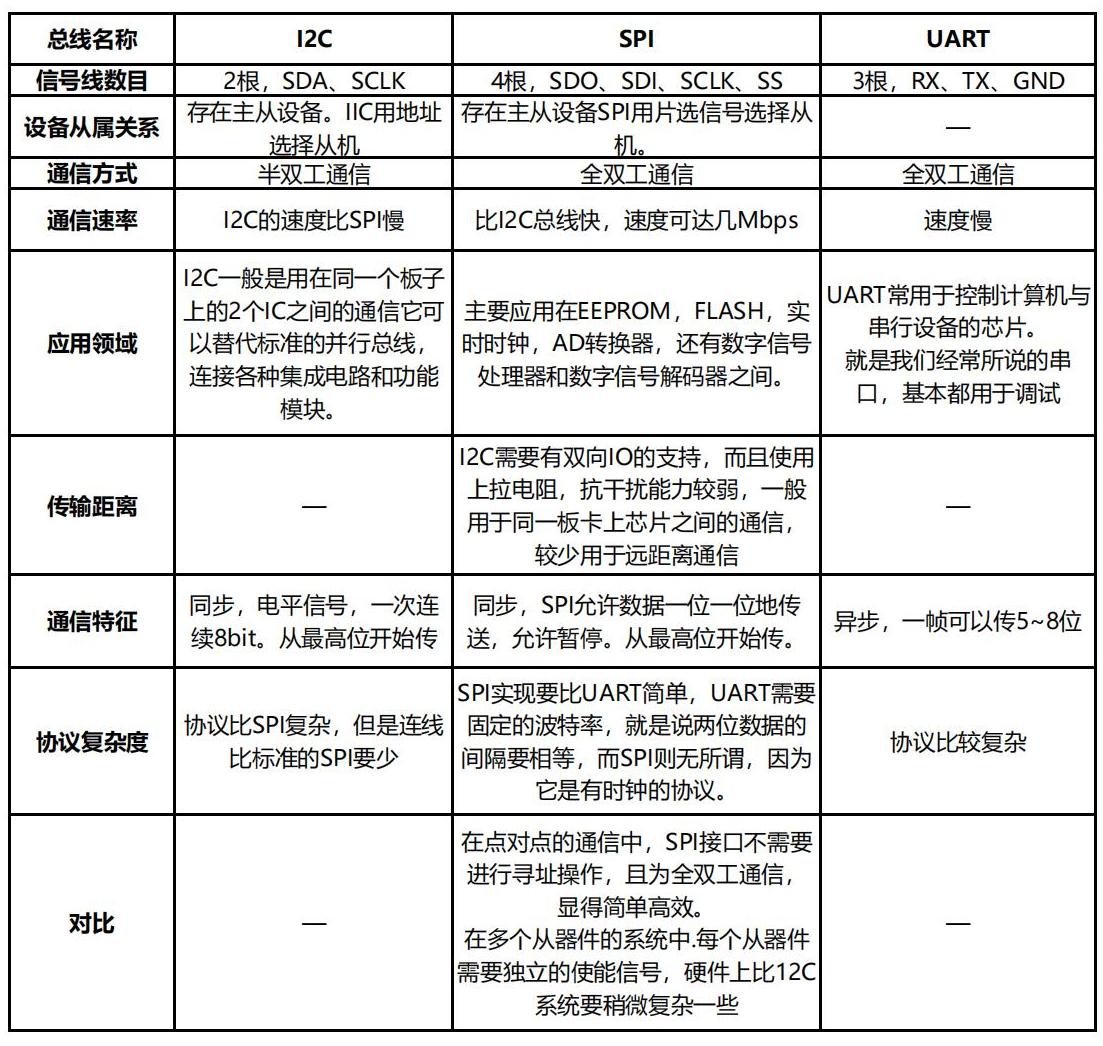

1 SPI4.2總線基本原理

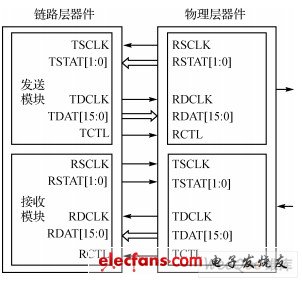

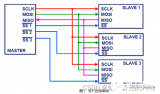

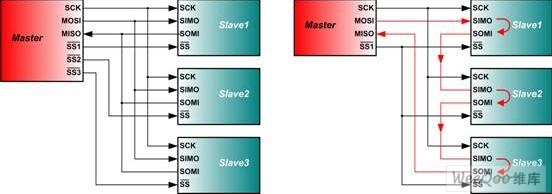

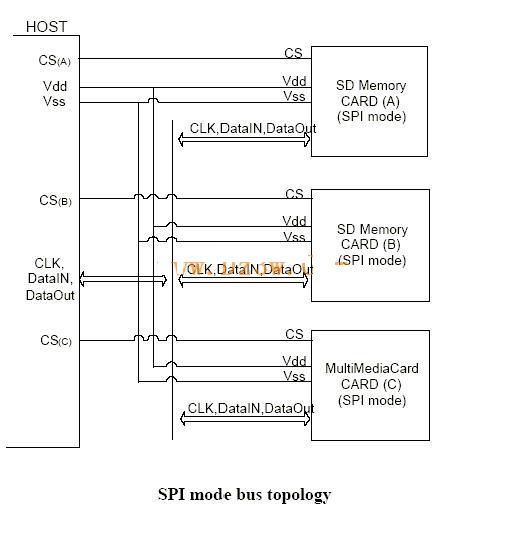

SPI4.2總線是一種芯片間的互連總線,連接芯片的鏈路層和物理層模塊。其工作時鐘是源同步雙邊沿觸發時鐘,至少為311 MHz。圖1是使用SPI4.2總線連接兩個芯片的示意圖。可見,SPI4.2總線的信號在發送和接收方向完全對稱而又互相獨立,數據鏈路和狀態鏈路分開,并且其時鐘也是完全分開的。因此,該總線不僅適合于雙向通道,而且適合于只收不發或者只發不收的單向通道。

?

圖1 SPI4.2連接示意圖

SPI4.2總線具有以下特點:

① 點對點互連,收發數據鏈路寬度為16位。

② 發送和接收模塊的信號各分為兩組,即數據信號和狀態信號,分別對應數據鏈路和狀態鏈路,每個鏈路具有自己的時鐘。數據鏈路發送和接收數據,狀態鏈路傳輸相應鏈路的狀態信息。

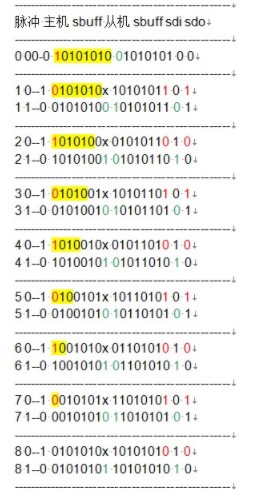

③ 數據鏈路包含DCLK、DAT[15:0]和CTL三種LVDS(低壓差分傳輸)信號。前面加“T”表示信號屬于發送模塊,加“R”表示信號屬于接收模塊。以發送模塊為例,TDCLK是雙邊沿觸發時鐘,TCTL是控制信號,TDAT[15:0]承載了數據和控制信息。當TCTL為高電平時,TDAT[15:0]傳送的是數據包;當TCTL為低電平時,TDAT[15:0]傳送的是控制包。數據采用DIP4校驗交織碼。

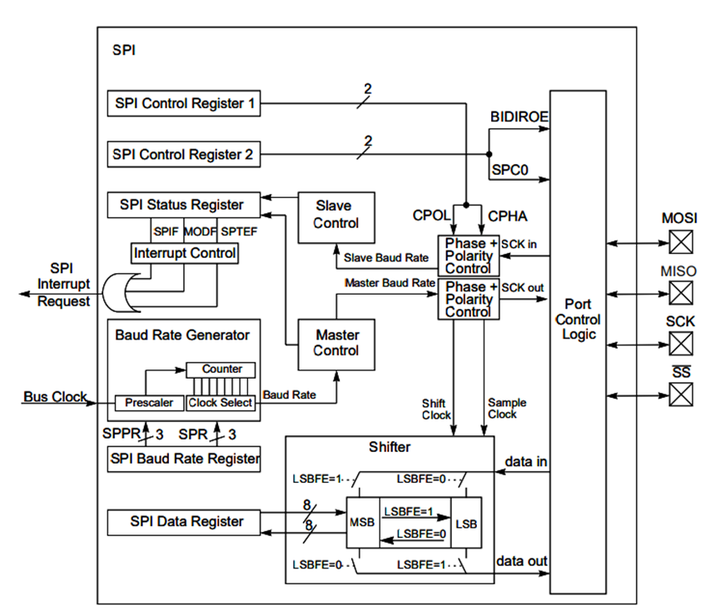

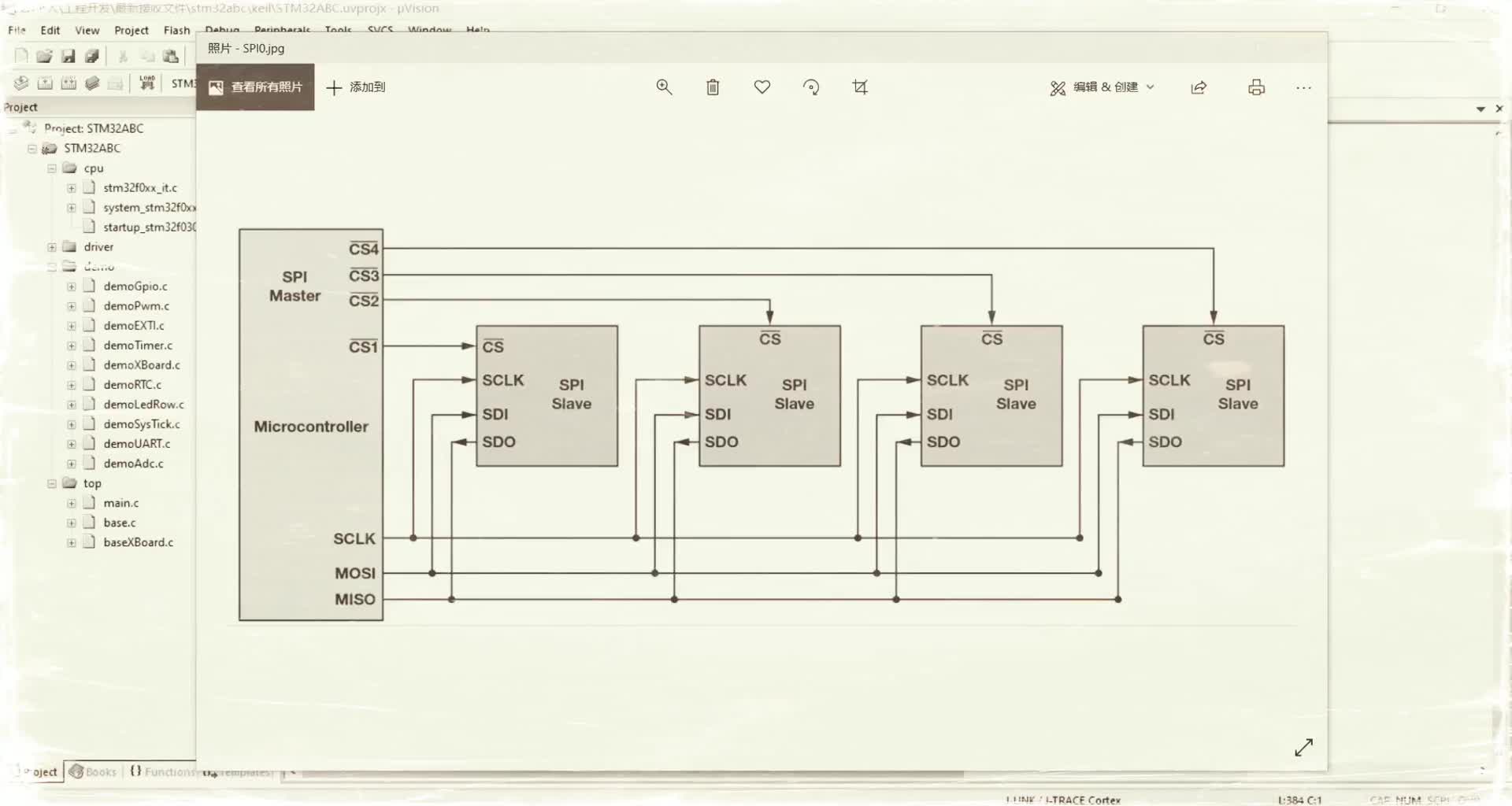

④ 狀態鏈路包括SCLK時鐘信號和STAT[1:0]狀態信號,信號類型是LVTTL或LVDS。SPI4.2 發送時序如圖2所示。如果選擇LVTTL,則SCLK時鐘頻率是數據鏈路時鐘速率的1/4。如果選擇LVDS,則SCLK時鐘頻率和數據鏈路時鐘頻率相同。下文中均以LVDS為例進行闡述。狀態鏈路主要用于流控。

⑤ 接收和發送模塊都含有一個FIFO隊列,用于緩存數據,隊列長度由芯片設計而定。隊列的狀態信息通過狀態鏈路周期性地發送,接收模塊和發送模塊的狀態信息是獨立的。狀態信息附加了DIP2交織校驗碼,以提高傳輸可靠性。

?

圖2 SPI4.2 發送時序

除了數據包中最后一段不滿16字節的數據(EOP)之外,SPI4.2總線的數據實行突發傳輸,以16字節為單位(稱為一個數據塊),每次傳輸多個數據塊。因為數據寬度是16位,所以一次突發傳輸至少需要4個時鐘周期。數據的高地址位字節先發送(MSB),低地址位字節后發送,數據塊傳輸過程中不會被中斷。每次突發傳輸的間隔期間傳送控制包或者訓練序列。圖2中,TDAT表示數據塊,TCTRL表示控制塊。控制包長度為16位,包含了前次傳輸和下次傳輸的狀態信息:包開始標志、包結束標志、邏輯端口地址和DIP4交織校驗碼等。數據鏈路遵循有限狀態機進行工作,狀態包括5種:控制包傳輸、數據包傳輸、空閑包傳輸、訓練序列傳輸以及訓練序列控制[1]。

因為狀態鏈路的寬度是2位,所以每次突發傳輸至少傳輸16位數據(4個時鐘周期)。反映FIFO隊列的狀態信息有3種:飽(SaTIsfied)、餓(Hungry)、極餓(Starving),分別對應二進制數字10、01和00。11表示鏈路處于失步狀態,正在同步過程中。當狀態是“飽”時,說明隊列幾乎滿了,只接收當前正在傳送的數據包,其他數據包只有等狀態更新后才能接收。當狀態是“餓”時,可以接收最大MaxBurst2個數據塊。當狀態是“極餓”時,說明隊列幾乎空了,可以接收最大MaxBurst1個數據塊。MaxBurst1和MaxBurst2是SPI4.2總線初始化時設定的參數,MaxBurst1不得小于MaxBurst2。

2 SPI4.2總線的初始化和同步

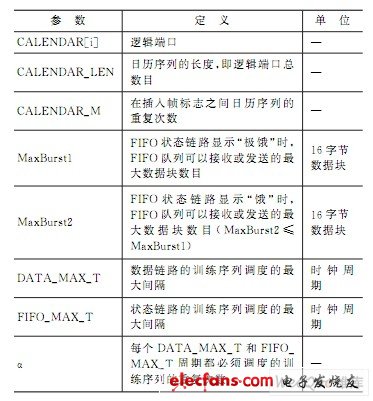

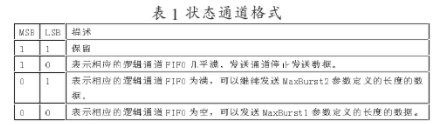

SPI4.2總線初始化時必須設定一些基本參數,如表1所列。

SPI4.2總線協議定義了一個叫“日歷”的數據結構CALENDAR[i](i=1,…,CALENDAR_LEN)。CALENDAR_LEN(日歷長度)參數規定了邏輯端口(或稱為虛擬通道)的數目,該數值不能小于實際的邏輯端口數目。例如,如果SPI4.2總線用于10 Gb/s以太網口,那么日歷長度是1(即CALENDAR_LEN = 1);如果SPI4.2總線用于10個1 Gb/s以太網口,那么日歷長度是10(CALENDAR_LEN = 10),CALENDAR[i] = 1,2,…,10,代表了10個以太網端口。CALENDAR[i]中承載的數據被周而復始地依次傳輸,重復次數是CALENDAR_M次。圖3為日歷長度和重復次數都是4的數據傳輸示意圖。SPI4.2總線被初始化時,必須確保接口兩端的CALENDAR_LEN和CALENDAR_M分別相等。從這個角度看,SPI4.2是一種時分復用的總線:總帶寬是固定的,“日歷”數據結構決定了帶寬和邏輯端口的分配。

當SPI4.2正常工作時,數據和狀態鏈路會不定期地發送訓練序列。在數據鏈路,訓練序列至少應該在DATA_MAX_T個時鐘周期內發送一次。在狀態鏈路,訓練序列至少應該在FIFO_MAX_T個時鐘周期內發送一次。設置DATA_MAX_T或FIFO_MAX_T為0將取消各自鏈路的訓練序列,一般情況下不推薦這種設置。

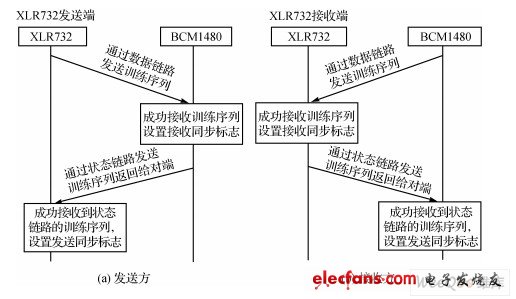

圖4以XLR732為參照描述了SPI4.2總線的收發同步過程。啟動之后,在發送方向,發送模塊(TX)通過數據鏈路發送連續的訓練序列,對端的接收模塊成功收到訓練序列后,會設置本端的接收同步標志;然后通過狀態鏈路發送訓練序列給對端,一旦發送模塊成功接收到訓練序列后,就設置本端的發送同步標志。

在接收方,接收模塊(RX)在數據鏈路成功接收到對端發送的訓練序列后,會設置本端的接收同步標志;然后通過狀態鏈路發送訓練序列,一旦發送模塊成功接收到訓練序列后,就設置本端的發送同步標志。在同步過程中,訓練序列由指定的連續的DIP4碼字組成。發送模塊必須連續發送訓練序列,直到本端的狀態鏈路收到有效信息。同時,接收模塊忽視所有接收到的數據,直到觀察到訓練序列,獲得數據同步。一旦數據鏈路同步之后, FIFO隊列狀態信息就開始傳送。

如果發送方接收到有效的狀態信息,它就可以開始進行數據突發傳輸。如果在工作過程中,由于某些原因(例如一端器件掉電或重啟)導致總線失步,那么為了再次獲得同步,雙方需要按照上述過程發送連續的訓練序列,直到建立同步為止。

表1 SPI4.2初始化基本參數

?

?

圖3 日歷長度和重復次數都為4的數據傳輸示意圖

?

圖4 收發同步過程示意圖

3 SPI4.2總線接口的調試

SPI4.2總線接口的調試包括兩個重要步驟:鏈路的同步和數據的正常收發。

在調試鏈路同步時,首先必須查看總線兩端的初始化參數配置。因為SPI4.2 總線協議是一個對等端數據傳輸協議,所以大部分參數需要雙方的匹配和協商,特別是接收方和發送方的CALENDAR_LEN和CALENDAR_M參數。

如何查看同步呢?芯片通常會提供一個狀態寄存器來反映總線的同步。“接收同步標志”只能說明在數據鏈路上成功接收到對端的訓練序列,但不能保證接收的狀態鏈路是正常的,如果需要確認可查看對端的“發送同步標志”。在收發雙向通道應用中,只有兩端的“接收同步標志”和“發送同步標志”都置位了,總線才算同步。此時,可以確認總線兩端的物理連接是正確的,握手成功。

如果不能同步,就必須檢查兩端的“接收同步標志”和“發送同步標志”,判斷是哪一端出了問題。檢查是否有DIP4和DIP2錯誤,如果有此類錯誤,說明鏈路上信號質量可能不佳,可以用示波器測量信號波形。如果信號質量確實不好,可以通過提高信號驅動能力或者調整硬件匹配阻抗來優化。

如果兩端的接收和發送都沒有同步,就必須測量芯片的電壓、工作頻率、重啟等信號。如果兩端的“接收同步標志”和“發送同步標志”都已經置位,說明雙方的接收和發送都同步,可以正常收發數據了。在大流量數據傳輸過程中,最相關的是FIFO隊列的參數配置,配置不當會導致錯包或丟包。以NetLogic公司的XLR732網絡處理器為例[2],SPI4.2總線的發送模塊的所有邏輯端口共享一個FIFO隊列,寬度為16字節,長度為128;接收模塊的所有邏輯端口共享一個FIFO隊列,寬度為16字節,長度為512。每個邏輯端口所占用的隊列地址和大小都可以通過寄存器配置。

假如某個端口接收端隊列的長度是48,MaxBurst1是12,MaxBurst2是8。那么當該模塊接收數據時,如果由于某些原因(例如軟件來不及處理),接收隊列只剩下12個空位,也就是接收隊列已經有48-12=36個空位被占用時,它將通過狀態鏈路向對端發送“餓”的狀態信號(反壓信號)。對端收到該信號后實施流控策略,根據本端發送端的MaxBurst1設置值發送數據,該值表示接收到“餓”狀態信號后最多還可以發送的數據塊數目。所以接收端的MaxBurst1 的值一定要大于對端發送端的MaxBurst1,并且要留出一定的余量,因為數據在鏈路上的傳輸也是需要時間的。同理,接收端的MaxBurst2要大于對端發送端的MaxBurst2。值得注意的是,流控是基于邏輯端口的,而不是整條鏈路。

為保證不發生接收端FIFO隊列溢出等問題,盡量將接收端的MaxBurst1和MaxBurst2設置大一些, 只要小于FIFO入口總數就可以,而發送端MaxBurst1和MaxBurst2的 設置不要超過本端接收能力。

如果出現EOP(結束包)和SOP(起始包)錯誤或缺失,或者其他錯包(例如包長變短、幀校驗錯誤等),但沒有DIP4 錯誤,該怎么辦?這類問題一般出現在FIFO隊列設置上,尤其是接收端的FIFO隊列可能溢出,從而丟失了某些數據塊,可以通過以下3種方法來檢測和解決:

① 通過查看接收端FIFO溢出標志來判斷FIFO隊列是否溢出;

② 通過調整接收端的MaxBurst1和MaxBurst2來防止FIFO隊列溢出;

③ 如果方法②的調整足夠大,還有此問題,可以查看對端是否收到反壓信號,以及對端的狀態等。

為了方便,通常將發送端的MaxBurst1和MaxBurst2設置為相同數值,將接收端的MaxBurst1和MaxBurst2也設置成相同數值。

結語

隨著處理器的速度越來越快,處理器集成的內核越來越多,處理器與外圍器件之間,處理器之間,以及外圍器件之間的連接速度逐漸成為制約平臺性能的瓶頸。許多芯片同時集成了多個總線接口,例如XLR732同時擁有SPI4.2、HT、以太網3種總線接口。SPI4.2總線在與其他總線的競爭中體現出了強大的生命力,希望本文所介紹的經驗對正在應用或計劃應用SPI4.2總線的同行有所幫助。

電子發燒友App

電子發燒友App

評論